### ESA's DSP Day: 3<sup>rd</sup> ESA workshop on Digital Signal Processing for Space Applications, 15<sup>th</sup> - 16<sup>th</sup> June 2016

Organized this year in conjunction with AMICSA, provides an overview on relevant development roadmaps, updates on Digital Signal Processing technology for space applications, and the results of contractual activities for the development of DSP rad-hard components, related equipment, IP cores, and software.

|          |    | DSP Day Round Table Discussion – DSP and FPGA   |

|----------|----|-------------------------------------------------|

|          | #6 | IP Cores, FPGAs, and their Synergies with DSPs  |

|          | #5 | DSP Software and Applications                   |

|          | #4 | DSP Day Reception & Poster session              |

|          | #3 | COTS based DSP Systems and Boards               |

|          | #2 | Test, Verification & Qualification of DSP Chips |

| Sessions | #1 | Rad-hard DSP Chips                              |

NEW: previous events (2012, 2014) were held as "final presentation Days" at ESA (Noordwijk, NL). This year: workshop character, open for non-ESA activities, conjunction with AMICSA

#### DSP Day 2016 – Programme Day 2 / session 5

#### ESA DSP Day - Day 2 Introduction - Radisson Blu Scandinavia Hotel (09:00-09:05)

- Conveners: Dr. Trautner, Roland

#### Session 5: DSP Software and Applications - Radisson Blu Scandinavia Hotel (09:05-11:05)

- Conveners: Mr. NOTEBAERT, Olivier

| time  | [id] title                                                                                            | presenter             |

|-------|-------------------------------------------------------------------------------------------------------|-----------------------|

| 09:05 | [38] DSP Benchmark Results of the GR740 Rad-Hard Quad-Core LEON4FT                                    | Dr. JALLE, Javier     |

| 09:35 | [26] A Lightweight Operating System for the SSDP                                                      | Mr. LUNTZER, Armin    |

| 10:05 | [39] High-performance DSP for onboard image processing                                                | Mr. NAGHMOUCHI, Jamin |

| 10:35 | [27] Space Debris Detection on the HPDP, a Coarse-Grained Reconfigurable Array Architecture for Space | Mr. SUAREZ, Diego     |

#### DSP Day 2016 - Programme Day 2 / session 6

Session 6: IP Cores, FPGAs, and their Synergies with DSPs - Radisson Blu Scandinavia Hotel (11:30-12:30)

- Conveners: Mr. Andersson, Jan

| 1 | ime   | [id] title                                                                        | presenter            |

|---|-------|-----------------------------------------------------------------------------------|----------------------|

|   | 11:30 | [15] Multi-core DSP sub-system IP                                                 | Dr. RAUWERDA, Gerard |

| ľ | 12:00 | [47] DSP and FPGA: Competition, Synergy, and Future Integration in Space<br>ASICs | Dr. TRAUTNER, Roland |

Round Table Discussion - DSP and FPGA: Open discussion on synergies of DSP and FPGA IP, related user requirements, and industrial views - Radisson Blu Scandinavia Hotel (12:30-12:55)

(description)

- Conveners: Dr. Trautner, Roland

**DSP Day 2**

Coffee Break

11:05 to 11:30

# DSP Day 2 – Session 6: IP Cores, FPGAs, and their Synergies with DSPs

# DSP Day 2 – Round Table Discussion: DSP and FPGA

#### The DSP Day Round Table Discussion will be structured as follows

- Intro: Discussion purpose and background (ESA)

- Round table discussion

- Some questions are presented, others invited from audience

- In discussion, first state name, company, then opinion

- ESA will record discussions

- Don't be shy ☺

- Summary / wrap-up

#### => What happens next?

- ESA will compile discussion summary, and distribute a questionnaire after the meeting

- Feedback in provided will influence future DSP related R&D performed by ESA

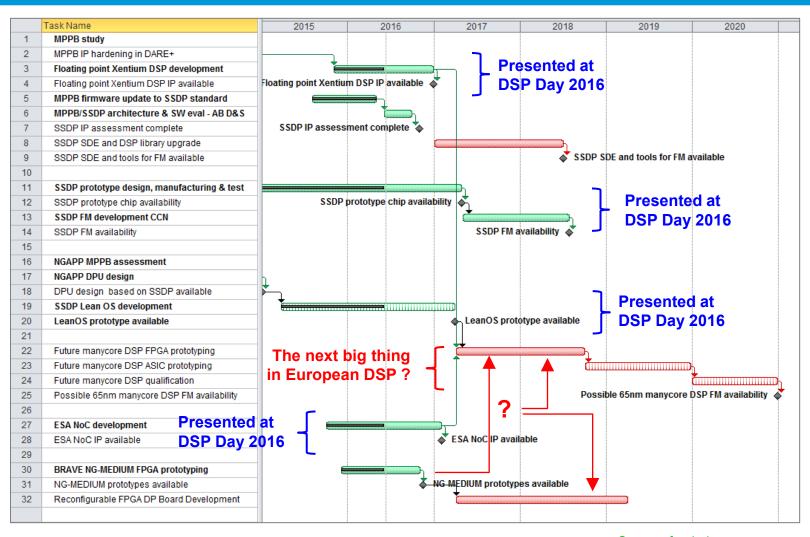

#### DSP Day 2016 — Round Table Discussion: Intro & Background / Some ongoing and future ESA activities in DSP

European Space Agency

DSP Day 2016 – Round Table Discussion: Questions

**Topic: DSP and FPGA**

- How do you see the future shares of rad-hard (DSP) ASICs and (rad-hard / rad-tolerant) FPGAs in payload data processing?

- 2. How attractive would you consider a high performance payload processor chip that combines GPP/DSP cores with on-chip FPGA(s)?

- 3. What are your expectations for the utilization of COTS DSPs and COTS FPGAs in future space data processing applications?

- 4. Additional questions from the audience

- 5. Discussion Wrap-up (ESA)

DSP Day 2016 – Round Table Discussion: Questions

#### **Last Questions - DSP Day 2018**

- 1. How do you rate the conjunction of DSP Day 2016 and AMICSA? Should it be repeated in 2018?

- 2. How do you rate the extended scope of DSP Day 2016 (workshop character instead of ESA final presentation days, as in 2012/14) Should we keep this format for 2018?

- 3. Do you have any preferences for the 2018 DSP Day location? **Do you prefer ESTEC, or could it / should it be elsewhere?**

#### **DSP Day 2**

### Wrap-Up

- Event Summary

- DSP Day 2018

- Round Table follow-up

- AOB

European Space Agency

## Thank You

The AMICSA & DSP Organizing Committee wishes you a safe trip back home –

and hopes to see you again at the next event in 2018!

European Space Agency