Radiation Prediction Tool Dedicated to Analyze and Harden by Design Readout Circuits of Photonic ICs

L. Artola<sup>1</sup>, S. Ducret<sup>2</sup>, G. Hubert<sup>1</sup>, F. Perrier<sup>2</sup>, and N. Ricard<sup>2</sup>

<sup>1</sup> ONERA DESP, Toulouse France <sup>2</sup> Sofradir, Veurey Voroize, France

retour sur innovation

#### **Context of the work**

- CMOS technology is relevant for integrate electronic functions in image sensors (raw decoders, registers, Flip-Flops)

- The SEEs (SEU and SET) sensitivity of CMOS technology increases with technological roadmaps for analog and digital circuits

- High temperatures rise the soft error duration and the SEU occurrence

- For performance reasons, infrared image sensors developed by Sofradir works at very low temperatures down to 77°K

→ What are the SEU sensitivity trends of Flip-Flops used in the read-out circuit at ambient temperature and down to 77°K under heavy ions?

→ Prediction tool relevant to propose a hardened design for Flip-Flop cell used in the read-out circuit of Photonic IC ?

### **Prediction tool: MUSCA SEP3**

SOFRADIR

- esa کے دور کے میں کے میں کے میں کے میں کے معام کے معام کی کھنچ کے معام کر کی کھنچ کے معام کر کھی کے معام کر کھ AMICSA & DSP ڈ

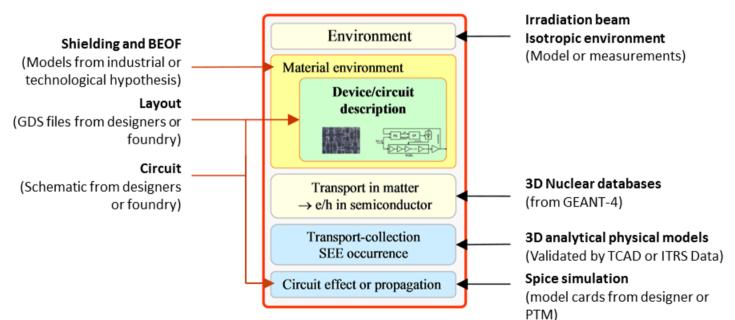

- MUSCA SEP3 is a Monte-Carlo prediction tool based on a multi-physics and multi-scales approach developed at ONERA dedicated for researches, space agencies, and industrials

**MUSCA SEP3**

Outputs: SEE (SET, SEU, SEL) estimations of cross section, operational rate, hardened design

- Modeling of the circuit at layout and schematics level

- Design extraction from GDS and circuit modeling

- Estimation of SEU sensitivity of Flip-Flops in 0.25µm technology

- Validation of SEU cross section estimations

- Estimation of temperature impact on the SEU cross section

- Failure analyses of Flip-Flops by sensitivity maps modeling

- Hardening by design of DFF cell based on prediction tool

- Presentation of the new hardened design of the DFF cell

- Evaluation of the hardening technique

- Conclusions and outlooks for analog and mixed-signal applications

- Modeling of the circuit at layout and schematics level

- Design extraction from GDS and circuit modeling

- Estimation of SEU sensitivity of Flip-Flops in 0.25µm technology

- Validation of SEU cross section estimations

- Estimation of temperature impact on the SEU cross section

- Failure analyses of Flip-Flops by sensitivity maps modeling

- Hardening by design of DFF cell based on prediction tool

- Presentation of the new hardened design of the DFF cell

- Evaluation of the hardening technique

- Conclusions and outlooks for analog and mixed-signal applications

### **Flip-Flop cells modeling**

- Test chip developed by Sofradir called SEU2\_01A

- 6 references of Flip-Flop cells designs

| Analyzed |  |

|----------|--|

| designs  |  |

| Reference | Cell area<br>(normalized) | Width<br>(normalized) | High<br>(normalized) | Techno. Node<br>(µm) |  |

|-----------|---------------------------|-----------------------|----------------------|----------------------|--|

| SEU_01A   |                           |                       |                      |                      |  |

| Design 1  | 1,03                      | 1,03                  | 1                    | 0,25                 |  |

| Design 2  | 1                         | 1                     | 1                    | 0,25                 |  |

| Design 3  | 1,1                       | 1,1                   | 1                    | 0,25                 |  |

| Design 4  | 1,07                      | 1,07                  | 1                    | 0,25                 |  |

| Design 5  | 1,2                       | 1,2                   | 1                    | 0,25                 |  |

| Design 6  | 1,17                      | 1,17                  | 1                    | 0,25                 |  |

SOFRADIR

2 Designs are investigated for their criticality in the read-out circuit used by Sofradir in their infrared image sensors

### **Circuit/design cell modeling**

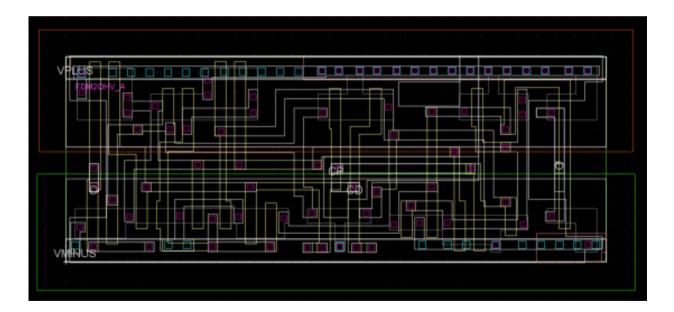

- Modeling of the Flip-Flop circuit at layout level

- Design extraction from GDS and circuitry development

- Extraction of collection areas from Sofradir's GDS file

- Circuit development with Cadence software suite based on the netlist

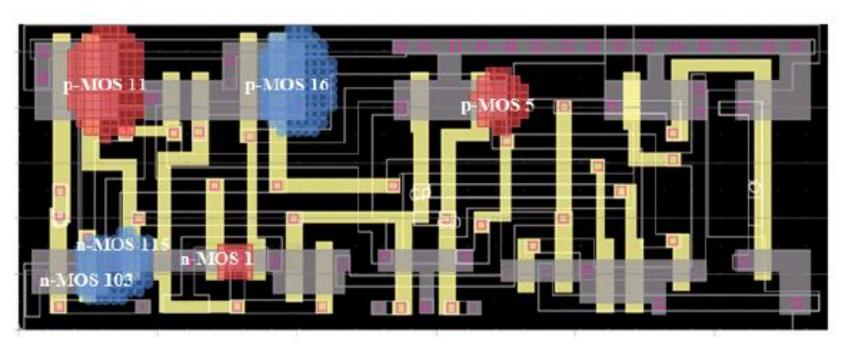

**GDS file from Sofradir**

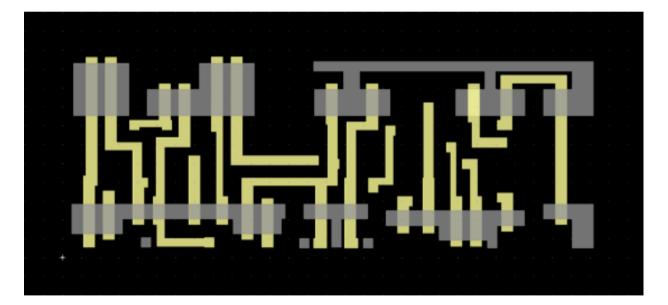

### **Circuit/design cell modeling**

- Modeling of the Flip-Flop circuit at layout level

- Design extraction from GDS and circuitry development

- Extraction of collection areas from Sofradir's GDS file

- Selection of relevant BEOL layers (polysilicon and active implants)

**GDS** file reworked

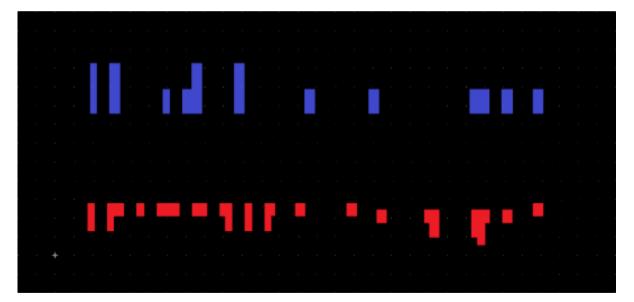

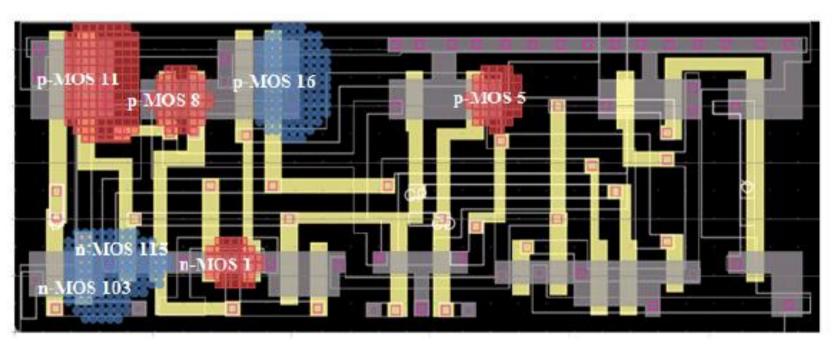

### **Circuit/design cell modeling**

- Modeling of the Flip-Flop circuit at layout level

- Design extraction from GDS and circuitry development

- Extraction of collection areas from Sofradir's GDS file

- Determination of collection area: drains of p-MOS and n-MOS transistors of floating nodes

**Extracted Design file**

d Terratio algorithms is

- Modeling of the circuit at layout and schematics level

- Design extraction from GDS and circuit modeling

- Estimation of SEU sensitivity of Flip-Flops in 0.25µm technology

- Validation of SEU cross section estimations

- Estimation of temperature impact on the SEU cross section

- Failure analyses of Flip-Flops by sensitivity maps modeling

- Hardening by design of DFF cell based on prediction tool

- Presentation of the new hardened design of the DFF cell

- Evaluation of the hardening technique

- Conclusions and outlooks for analog and mixed-signal applications

#### Setup of SEU exp. measurements

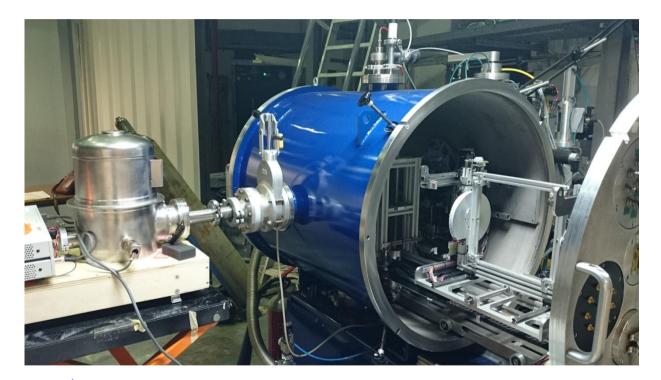

Experimental heavy ion irradiations for SEU measurements performed at UCL (Belgium) with CNES cryostat (in June 2014 and May 2015)

Temperature monitoring and regulation from 300°K to 80°K

Heavy ion irradiation from 6.6MeV.cm<sup>2</sup>.mg<sup>-1</sup> to 67.7MeV.cm<sup>2</sup>.mg<sup>-1</sup>

ONER

of Versity, additioned in

Dynamic SEU testing with TRAD test board using CNES cryostat under heavy ions beam at UCL, Belgium

Logic state, temperature are considered depending on LET of heavy ions

AMICSA & DSP 2016 - Goteborg June 13th – 16th 2016

SOFRADIR

# **Estimation of SEU sensitivity**

- Detection of SETs in the Flip-Flops (design 1 and 2)

- Nominal working of the Flip-Flop

| Output |  |

|--------|--|

| Clock  |  |

| Input  |  |

SOFRADIR

**No SEU detected**

SET/SEU occurrence on the Flip-Flop output

| Output | e seu | SEU detected |

|--------|-------|--------------|

| Clock  |       |              |

| Input  |       |              |

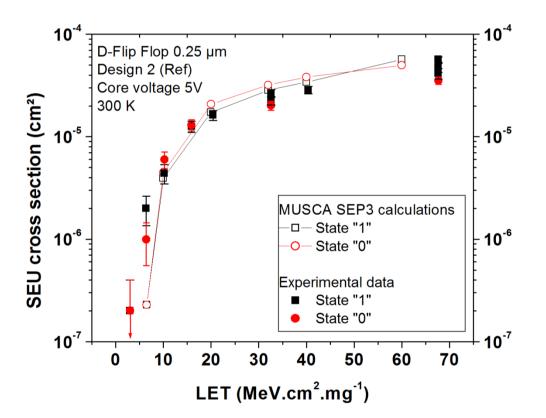

# Validation of SEU sensitivity (1/2)

Estimation of the SEU cross section of the Flip-Flop FDM2QHV (design 2)

Good correlation of SEU sensitivity between exp. And simulation for the reference design of DFF

AMICSA & DSP 2016 - Goteborg June 13th – 16th 2016

SOFRADIR

esa کے میں میں میں میں AMICSA DSP

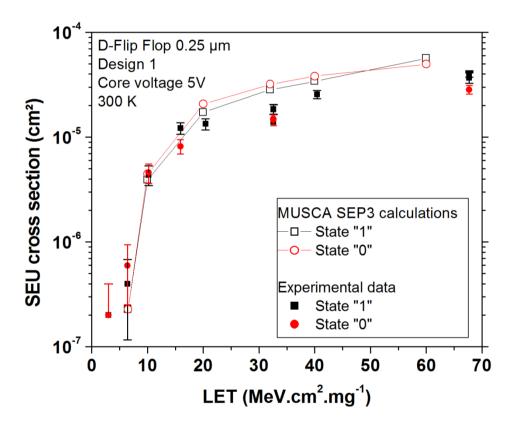

# Validation of SEU sensitivity (2/2)

Estimation of the SEU cross section of the Flip-Flop FDM2QHV (design 1)

Good correlation of SEU sensitivity between exp. And simulation for the reference design of DFF

AMICSA & DSP 2016 - Goteborg June 13th – 16th 2016

SOFRADIR

AMICSA DSP 🖁

esa

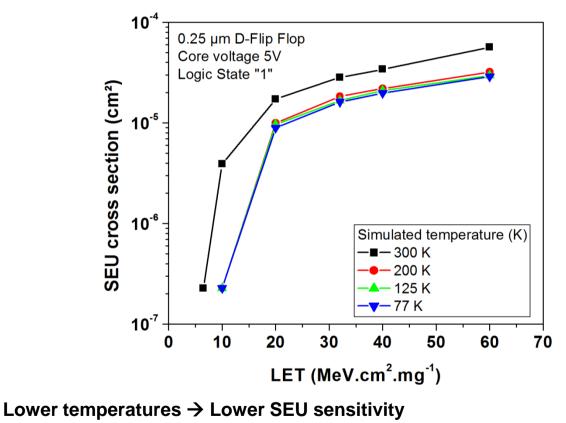

## **Estimation of SEU sensitivity**

SOFRADIR

ONERA

ted version administry i.e.

Effects of low temperatures on the SEU cross section of the Flip-Flop FDM2QHV (design 2)

Saturation of the temperature effects on the SEU sensitivity

# Failure analysis of Flip-Flop cell (1/2)

• SEU sensitivity maps of DFF design 2 for a LET 58,8 MeV.cm<sup>2</sup>.mg<sup>-1</sup> at **77°K**

The logic state changes the SEU critical areas of Flip-Flop cell

# Failure analysis of Flip-Flop cell (2/2)

SEU sensitivity maps of DFF design 2 for a LET 58,8 MeV.cm<sup>2</sup>.mg<sup>-1</sup> at 300°K

State « 0 »

At 300°K  $\rightarrow$  New sensitive transistor (p-MOS 8)  $\rightarrow$  State 1 more sensitive than State 0

- ្រ្វិ ខ្លាំ ខ្លាំ ខេនa AMICSA DSP នឹ

- Modeling of the circuit at layout and schematics level

- Design extraction from GDS and circuit modeling

- Estimation of SEU sensitivity of Flip-Flops in 0.25µm technology

- Validation of SEU cross section estimations

- Estimation of temperature impact on the SEU cross section

- Failure analyses of Flip-Flops by sensitivity maps modeling

- Hardening by design of DFF cell based on prediction tool

- Presentation of the new hardened design of the DFF cell

- Evaluation of the hardening technique

- Conclusions and outlooks for analog mixed-signal applications

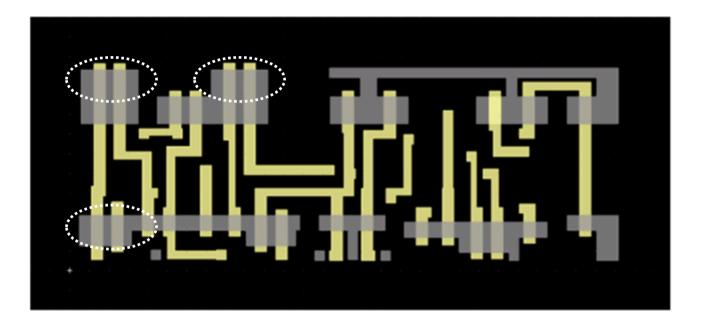

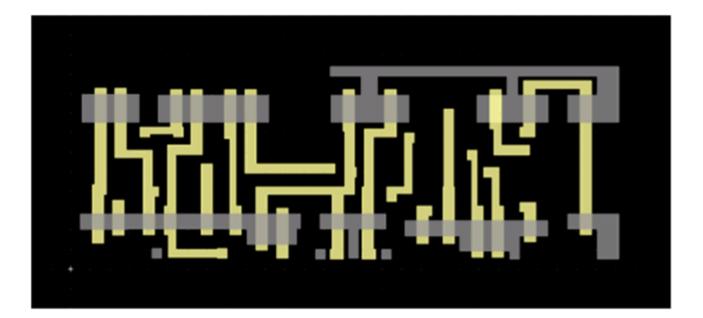

### Hardening by design DFF

ONER

and Verteille, additionant i.e.

Decrease the width of the wider sensitive n-MOS and p-MOS transistors

Limitation of the sensitive areas the DFF : 4 p-MOS and 2 n-MOS

Decrease the drive current  $\rightarrow$  Decrease in the power needed

No area penalty

SOFRADIR

### Hardening by design DFF

ONER

and Verteille, additionant i.e.

• Decrease the width of the wider sensitive n-MOS and p-MOS transistors

Limitation of the sensitive areas the DFF : 4 p-MOS and 2 n-MOS

Decrease the drive current  $\rightarrow$  Decrease in the power needed

No area penalty

SOFRADIR

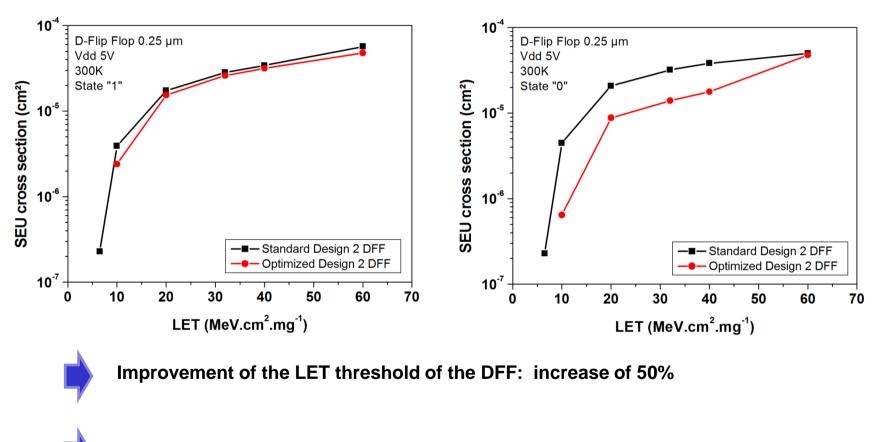

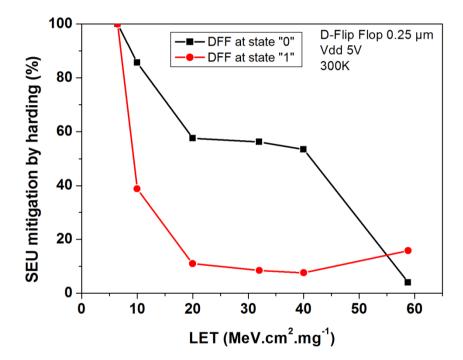

# **Evaluation of hardened DFF (1/2)**

SEU sensitivity of standard DFF and hardened DFF under heavy ions

Better mitigation of SEU for "0" stored in the DFF

SOFRADIR

# **Evaluation of hardened DFF (2/2)**

ONERA

ord Verteins additioners i.e.

• SEU sensitivity of standard DFF and hardened DFF under heavy ions

Better improvement for "0" stored in the DFF excepted at the highest LET

Differences of the SEU mitigation are due to the complete immunity of p-MOS-16 at state "0" stored in the DFF

AMICSA & DSP 2016 - Goteborg June 13th – 16th 2016

SOFRADIR

orginal contents of the second secon

of Versity additions in

- Modeling of the circuit at layout and schematics level

- Design extraction from GDS and circuit modeling

- Estimation of SEU sensitivity of Flip-Flops in 0.25µm technology

- Validation of SEU cross section estimations

- Estimation of temperature impact on the SEU cross section

- Failure analyses of Flip-Flops by sensitivity maps modeling

- Hardening by design of DFF cell based on prediction tool

- Presentation of the new hardened design of the DFF cell

- Evaluation of the hardening technique

- Conclusions and outlooks for analog and mixed-signal applications

#### **Conclusions and outlooks**

of Versity algorithms in

- Multi-scales modeling (with MUSCA SEP3 tool) leads to estimate the SEU sensitivity of Flip-Flops at 300K and cryogenic temperatures.

- Good correlations of SEU calculations and SEU measurements from 2014 and 2015 heavy ion irradiation campaigns at UCL facility (Belgium)

- The prediction tool allows to propose failure analysis at circuit and layout level useful for harden by design DFF

- The new hardened design of DFF presents a good mitigation ratio with no area penalty and lower power consuming.

→ Proposition of general hardening guidelines for DFF designs for space applications

$\rightarrow$  Application of the SEE prediction tool (MUSCA SEP3) and analog mixed signal circuits

SOFRADIR