# Using a Standard Commercial Process for Full Custom Rad Hard Mixed-Signal Design

12. - 16. June 2016, AMICSA 2016, Gothenburg

Dr. Sebastian Millner

Andreas Zoller

Volker Lück

PROPRIETARY INFORMATION

© Tesat-Spacecom GmbH & Co. KG reserves all rights including industrial property rights, and all rights of disposal such as copying and passing to third parties

#### **Overview**

- » Motivation for and special requirements for AMS-ASIC-Design at Tesat

- » Choices and Decisions

- » Process Selection

- » Design Flow

- » Hardening Approach

- » Example

- » Acknowledgements

#### Motivation and Requirements

- » Tesat is "just an equipment supplier"

- » Improvement of equipment needs higher integration of functionality

- » Effort to be concentated to main competence

- » ASIC design concentrated on own applications

#### History - where Tesat comes from

- » AT4, Atmel 0.5 µ CMOS 5V digital

- » First mixed signal designs using analog IPs and radiation hardened digital library (DARE), qualified

- » Knut, UMC 180 nm, CMOS, 3.3V, Mixed Signal

- » First mixed signal test designs using own analog circuits and non-hardened library elements, hardened on design level, tlfa1, Lfoundry 180 nm

- » Mixed signal ASIC design approach using analog lps

- »txfa1, XFab 180 nm

- » lama, XFab 180 nm

#### **Choices and Decisions**

"Make"

Analog-on-Top

"commercial process"

"Buy"

Digital-on-Top

"space qualified process"

Hardening by Process / Device / Design?

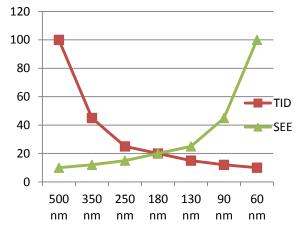

0.5µm, 0.35µm, 250nm, ... 90nm, 60nm

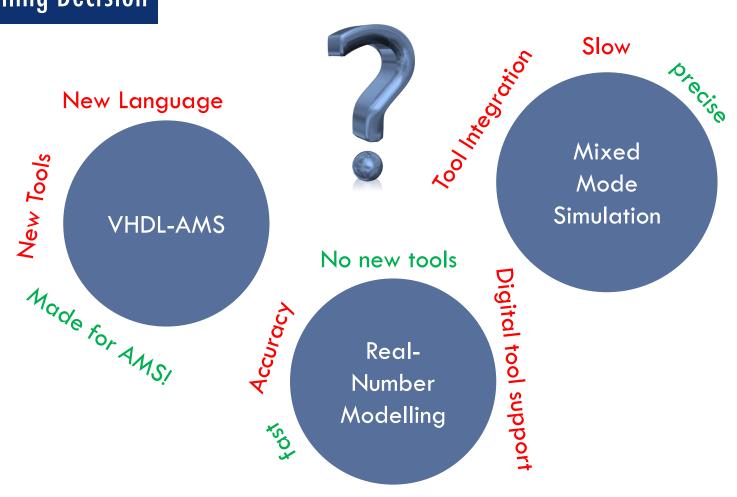

#### **Choices & Decisions**

PIONEERING WITH PASSION

### Make or Buy?

|      | Pro                                                                                                                                                                                                      | Contra                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Make | <ul> <li>» Independent</li> <li>» Easy adaption to modified requirements</li> <li>» Own experience grows</li> <li>» Detailed information on implementation</li> </ul>                                    | <ul><li>» Need for qualified personel and tools</li><li>» Increased qualification effort</li><li>» Increased procurement effort</li></ul>                   |

| Buy  | <ul> <li>No internal effort in tools and qualified manpower</li> <li>Experience from supplier can be used</li> <li>Existing designs might be reused</li> <li>Access to suppliers technologies</li> </ul> | <ul> <li>» Worse communication than make</li> <li>» Worse reuse than make</li> <li>» Dependency on supplier</li> <li>» No internal details known</li> </ul> |

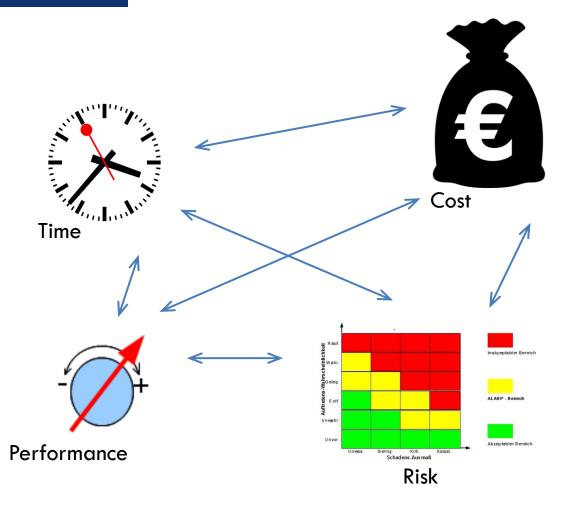

» Select node that most convinient with respect to

» TID

» SEE

» Cost

» Voltages

» Toolset

» Select process that supports MPWs

» Select process that supports small quantities

#### Hardening Approach

» On process level

much too expensive

» On primitive device level

results in expensive Library development!

» On design level / system level

"less optimal" than on device level "waste" of silicon area and power

» Hardening on design level provides solution with minimum investment and easiest transfer to other technologies!

#### Hardening Approach

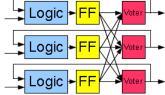

- » Digital Section:

- » Check library primitives by testing for radiation hardness

- » Select only suitable ones and apply hardening on design level

- → Tesat implemented full TMR by automated netlist modification after ordinary Synthesis

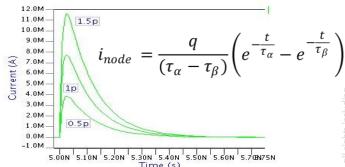

- » Check primitives by testing for radiation hardness

- » Select only suitable ones and take degradation into account

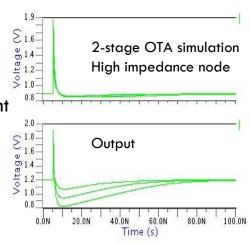

- » Perform SEE-simulation on sensitive nodes

- » by SEE-Pulse simulation and optimize circuit parameters

PIONEERING WITH PASSION

#### Analog or digital "on-top"?

|                   | Pro                                                                                                                         | Contra                                                                                                                                                                                                                                                                                                        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog<br>on top  | <ul><li>well known by analog designers</li><li>adapted to designs with rather small digital part and</li><li>Easy</li></ul> | » High effort and lots of manual work                                                                                                                                                                                                                                                                         |

| Digital<br>on top | <ul><li>» Good tooling support for P&amp;R</li><li>» Easy backannotation from external pins</li></ul>                       | <ul> <li>Integration of analog blocks not state of the art</li> <li>Integration of analog models into simulation and synthesis not state of the art</li> <li>Requires additional effort for integration of analog functions into digital design flow</li> <li>Worse support by tools and suppliers</li> </ul> |

#### Analog or digital "on-top"?

- » Hot topics for "digital-on-top":

- » What should top-netlist contain?

- » How about Power supplies, not usual in digital netlists.

- » How to pass analog signals through synthesis

- » How to model analog signals for simulation

- » How to manage wire width for analog signals during P&R?

- » How to characterize analog cells efficiently for digital design flow

PIONEERING WITH PASSION

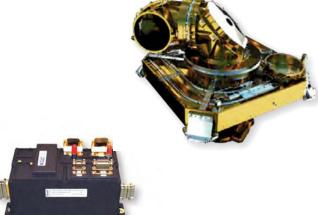

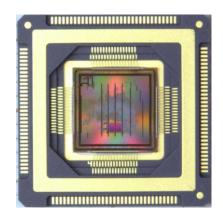

### Example

» Luca, TM/TC device for LCamp application, providing Bias point regulation for RF-chain

» Technology:

Xfab XH180

» Die Size: 6x6 mm²

» Gate Count: 500 kGates incl. full-TMR

» Clock domains: 1x 16 MHz

» Analog Functions: DAC, ADC, analog regulation, Power Supply

» Supply ranges: -5 V ... +8 V

» Radiation Hardness issues solved: SEU-hardness improved by

provision of TMR-IO-Buffer

#### **Actual Decisions**

- » Make, not buy

- » Commercial, not space qualified

- » Digital, not analog on top

- » Real number modelling and mixed-mode simulation, not AMS

- » Hardening on design and system level

- » IP reuse, not copy & paste

- » Accept deficiencies, don't try to change things you cannot change

#### What is missing?

- » Helpful Design rules for analog / mixed-signal Design

- » ECSS-Q-ST-60-02 seems not to really cover development of devices using commercial technologies

- » Standard Toolset used for mixed-Signal Design for Analog-on-Top and/or Digital-on-Top design approach

#### Acknowledgements

- » I want to thank my coauthors for their contribution to that paper and much more for all the effort they and my whole team take to make mixed signal ASIC designs as shown before real

- » I want to thank ESA for support during the last mixed signal development in frame of the ARTES 5.2 "New Lcamp Technologies" project ESTEC contract. no. 4000111633/14/NL/EM)

- » I want to thank the audience for the attention

## **Any Questions**