#### WE LOOK AFTER THE EARTH BEAT

## Hi-Rel COTS BASED Computer step 2

THALES ALENIA SPACE

#### ESA ESTEC Contract 4000104702

## inal Presentation ESTEC, December 9<sup>th</sup> 2015

Sanitas

Politecnico di Torino

- 1 Hi-Rel cots experience overview <u>TAS-I</u>

- 2 Hi-Rel cots board overview <u>SANITAS</u>

- >>> 3 Hi-Rel cots EGSE overview INAF

- >> 4 Hi-Rel cots SW test overview Politecnico di Torino

- **5** Conclusions and possible future developments <u>TAS-I</u>

## 1- Hi-Rel cots experience overview

THALES ALENIA SPACE

ESA ESTEC December 9th 2015 ThalesAlenia Space

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

3

- PrimeContractor:

- Subcontractors:

**~** Consultant:

Milan Site

#### SME company

Board and Basic SW development

#### Dept. of Automation and Computer Engineering of Politecnico di Torino (PoliTo):

Benchmark SW development

#### Institute INAF-IASF Milano

EGSE Development

Ulisse Consortium / University of Rome 2 "Tor Vergata"

DDR-II ECC Development

ESA Technical Officer: Claudio Monteleone (TEC-EDD)

#### THALES ALENIA SPACE

ThalesAlenia Space

ESA ESTEC December 9th 2015

- Thank to Hi-rel cots project new power PC applications for space on board computer with demanding computing needs has been developed

- The project objectives to build and test a Power PC board computer <u>has been achieved</u> and <u>new applications has</u> <u>been developed</u> with this board architecture

ESA ESTEC December 9th 2015

Single board Computer to be fly in <u>Meteosat third Generation Payload</u> <u>computer</u> has been developed.

- For MTG specific radiation test campaigns demonstrated adequacy of PC7448 E2V freescale versus GEO environment.

- For MTG Technologies for cooling power dissipation of CPU based on power PC has been faced and under development

- VISNAV ESA project for high performance imaging processing devoted to imaging space navigation system

- planetary landing systems

- ➤ rovers navigation

- >> Satellite & micro satellite maneuvers

- robotics

6

#### SBC single board Computer based on Power PC7448 for MTG

- CPU: PPC 7448 1GHz 2.3 Dhrystone MIPs/MHz

- Dual Boot ( on flash)

- ➢ RAM: 1Gbyte RSE (64+16)

- ➢ EEPROM: 512Kx16 +8 (EDAC code 16+8)

- ► FLASH: 8M16

- ➢ 6xSpiceWire: 200Mbps/each

- Mil-BUS1553B

- ➢ GPIO:

- 24 output

- 32 input

- 2x16 PWM

- ➢ Jtag/COP for emulation

- Test interface

- Power demand: 16W typical

- Package: BGA 360 (assembly qualified)

- Cooling: Heat pipe

- ➢ TID: 110kRad @ LDR

- SEE: tested @ 15MeV 20Ne, 40Ar. 84Kr. 129Xe

7

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

THALES ALENIA SPACE

#### THALES ALENIA SPACE

ESA ESTEC December 9th 2015

## 2- Hi-Rel cots Board overview

ESA ESTEC December 9th 2015 ThalesAlenia Space

9

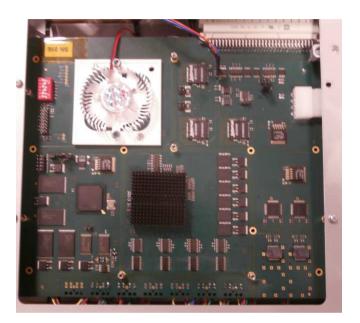

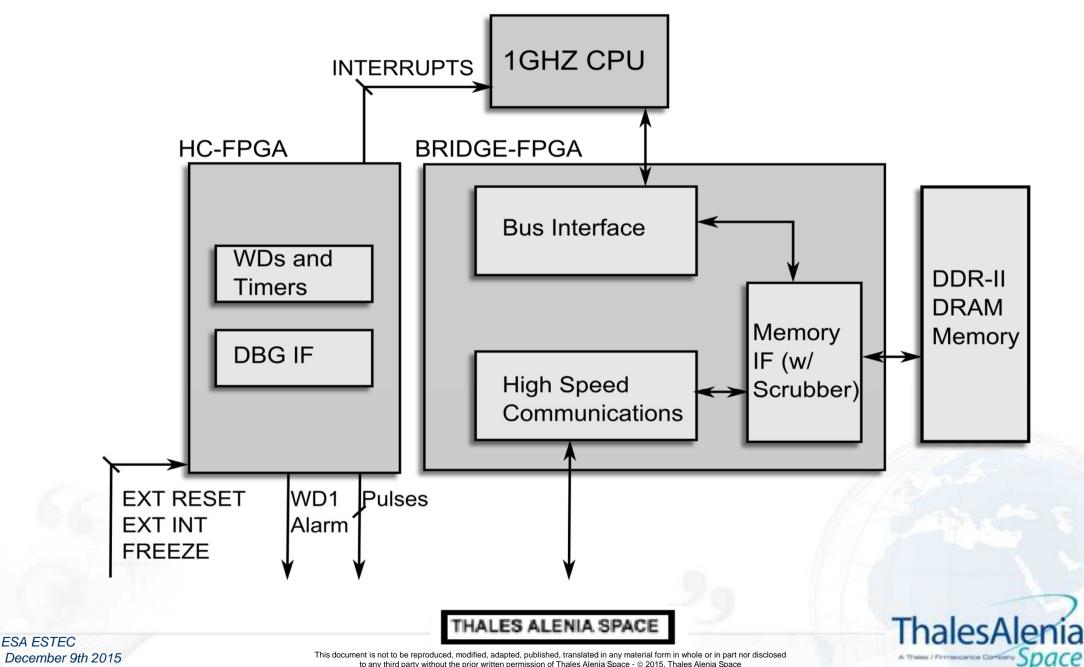

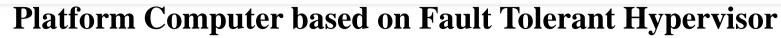

### **PM Block Diagram**

December 9th 2015

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

10

#### **Hi-Rel Cots board Main Characteristics**

#### ~ CPU:

- Freescale PowerPC PC7448 on Silicon-on-Insulator 90 nm process

- Performance 2.3 MIPS / MHz (Drystone 2.1 method) (\*)

- 🛰 2300 MIPS @ 1 GHz (\*)

- 32 KB L1 cache for Instructions, with Parity

- >> 32 KB L1 cache for Data, with Parity

- 1 MB L2 cache ECC protected

- ➤ Four Integer Units (IUs)

- A five stages Fully IEEE Compliant FPU for single and double precision operations

- ➤ Four Vector units (SIMD machine, typical task for DSP application) Altivec<sup>™</sup>

#### MEMORIES:

ESA ESTEC

December 9th 2015

- Up to 256 kBytes EEPROM Boot Memory (or 64 kBytes PROM)

- Up to 32 Mbytes Flash for Software Storage

- ➣ 512 Mbytes DDR-II DRAM as Working Memory, RS protected,

- High Memory access throughput for CPU and peripherals (> 500 Mbytes/sec)

- DMA Accesses to/from peripherals

#### (\*) Data from Freescale manufacturer

## Hi- rel cots board Interfaces

#### **High Speed Interfaces**

- ➣ 6 x Spacewire Links (up to 200 Mbps)

- 🛰 2 x HSSL:

- IGbit Ethernet

- UDP Layer

- standard Message frames (about 1500 bytes data max size)

- Communications through:

- DMA to/from Memory

- Mail-boxes (small data sets, typically 1/2 kBytes)

#### **Discrete Interfaces:**

- ✤ 4x External Interrupts (I)

- ✤ 4x Pulse Outputs (O)

- External Reset (I)

- 🛰 Alarms (O)

- 🛰 Heart-Beat (O)

#### **Test Interfaces:**

- CPU JTAG/COP Interface

- 🛰 RS232 UART:

- Zeading of SW in NVM

- Communication with CPU

- Access to FPGA registers

THALES ALENIA SPACE

ESA ESTEC December 9th 2015

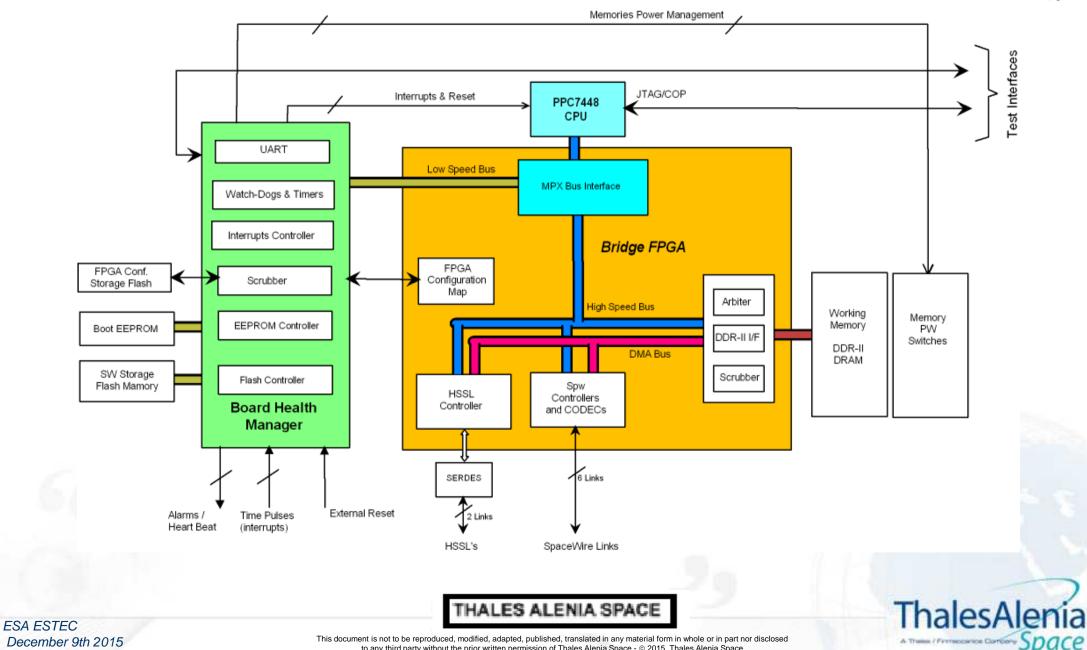

## Hi-rel cots PM Board view

- Extended Double Eurocard Form factor: 233 x 200 mm<sup>2</sup>

- Mass: < 850 gr (including stiffening frame)

- Power Consumption: ~ 17 W @ 1 GHz Core Clock (measured)

#### >> Development Tools

- Boot software and drivers developed in C and assembler

- Boot software and drivers developed and compiled using CodeWarrior 8.8 Development Tool by Freescale

- Soot software developed on the basis of the initialization functions provided by Freescale for the PCC74xx processors

- Boot operations organized in: initialization, self-check, and start of the User SW application

- Simple SW drivers developed to access and manage the PM basic functions

- SW driver have been grouped by PM architectural resource (e.g. I/O interfaces, timers, memories, etc.)

THALES ALENIA SPACE

9

## 3- Hi-Rel cots EGSE

THALES ALENIA SPACE

ESA ESTEC December 9th 2015 ThalesAlenia Space

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

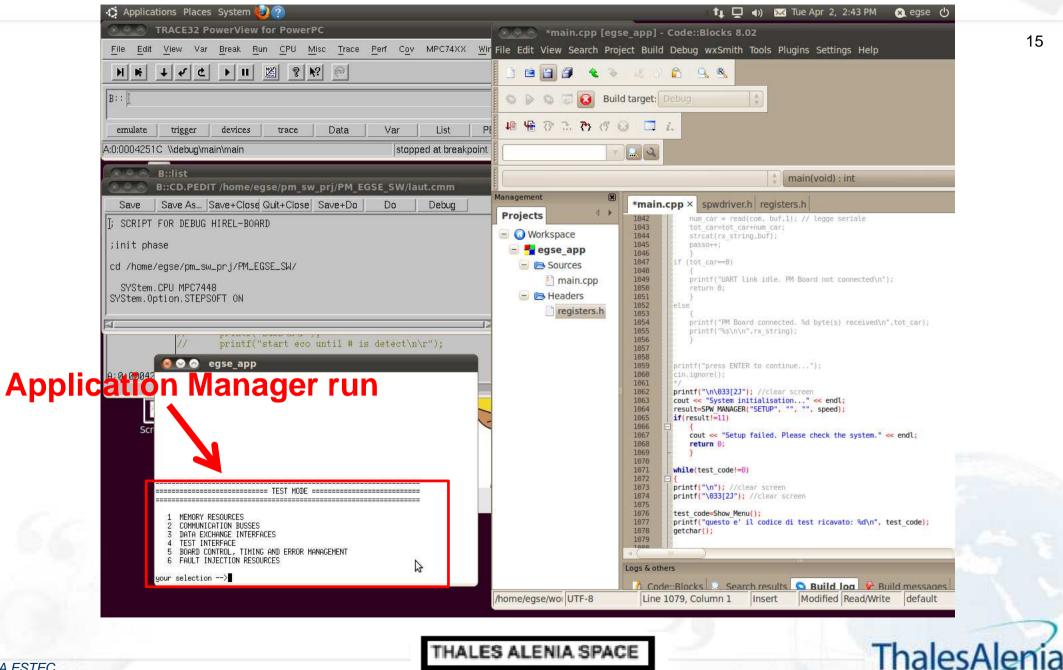

15

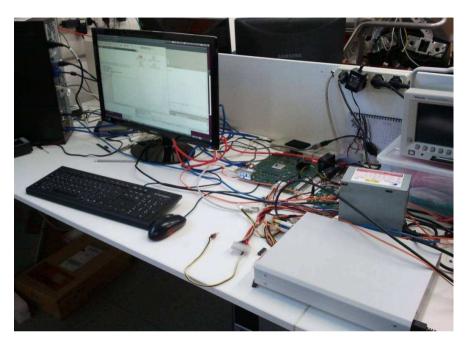

## Hi-rel cots board EGSE

#### >> Powerful workstation PC, including

- ✤ 6 SpaceWire ports

- 1 Lauterbach Debugger tool

- ➤ XILINX JTAG probe

- ➤ ACTEL JTAG probe

- 1 pci Digital I/O board

- 1 Ethernet board with two Gigabit ports

- Microsoft Windows 7, 32 bit

- Microsoft Visual C++ 2010 Express

Development Environment

16

ESA ESTEC December 9th 2015

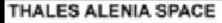

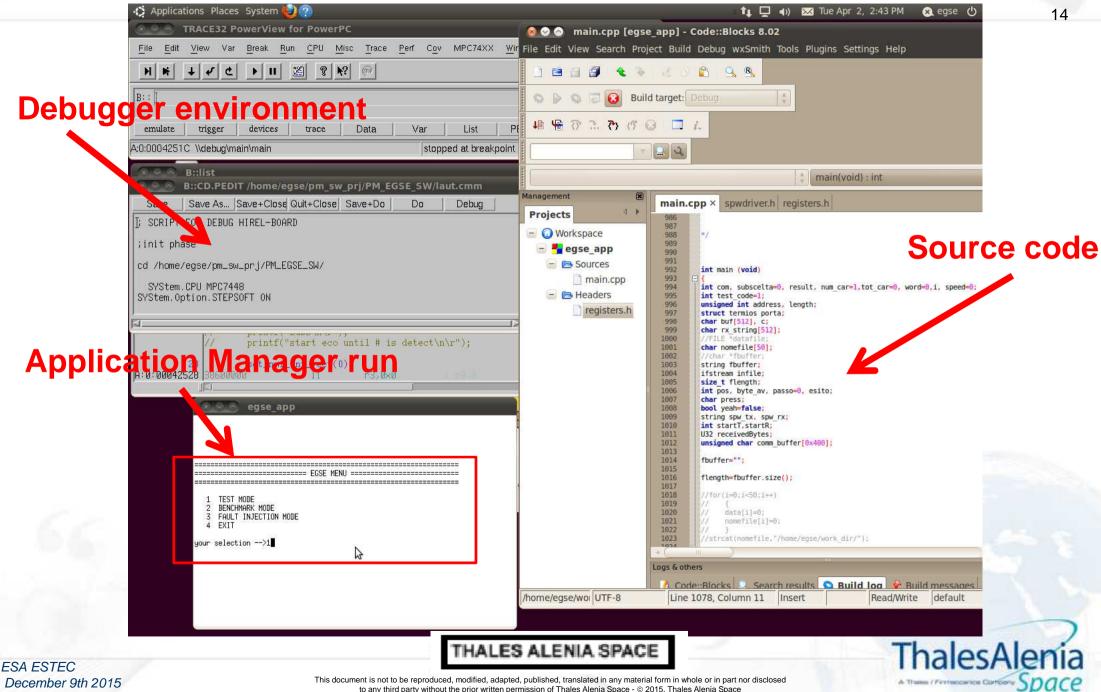

- PM Board testing/verification

- To test specific resources of the PM board, such as memory, communications links, and data interfaces

#### marking 🛰

- To test PM board performances when selected benchmarks are applied

- Fault injection

- To test the response of the PM board in presence of SEU like faults

#### modular approach

- Functional blocks that can be used in any applications, for instance PM Board testing, as basic atomic ingredients

- 🛰 uart\_manager

- spacewire\_manager

- 🛰 hssl\_manager

- rt\_event\_manger

- Avoid rewriting the same code multiple times, code can be reused

#### **Verification Tests**

- The objective is to show that implemented functions comply with all high level requirements.

- Implemented functions are verified by a set of procedures mainly running on the board processor and ruled by the EGSE

- Tests have been grouped in the following categories reflecting PM board and FPGAs specification:

- Memories resources (including registers)

- Communication buses

- Data exchange interface functions

- >> Board control, time and fault management

- Test interfaces

- Debug and fault injection specific function

THALES ALENIA SPACE

#### **EGSE** Operation

#### EGSE Operation (cont'd)

THALES ALENIA SPACE

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015. Thales Alenia Space

A Trains / Frytescarice Cortoory

## 4- Hi-Rel cots SIHFT test

THALES ALENIA SPACE

ESA ESTEC December 9th 2015 ThalesAlenia Space

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

22

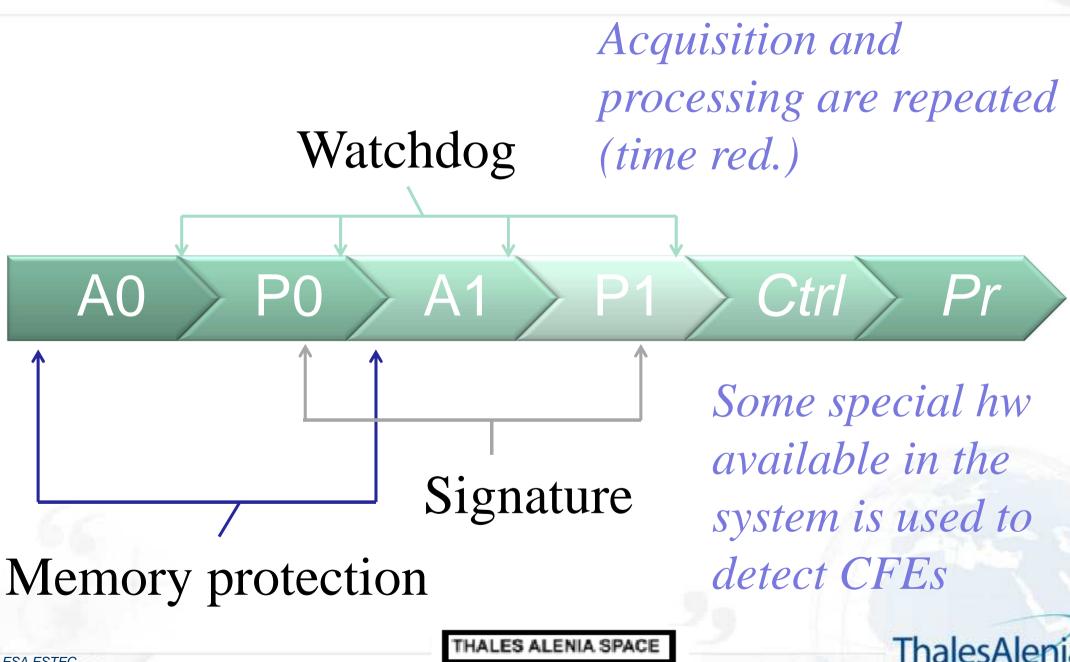

Develop a Software implemented hardware fault-tolerance technique

>> Develop a fault injection strategy

>> Evaluate system reliability through fault injection

ESA ESTEC December 9th 2015

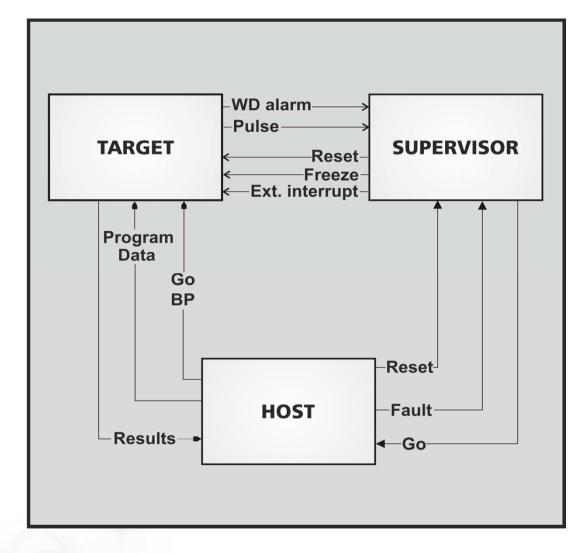

#### The target system (simplified diagram)

to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

# Composed of RICE, FFT, Dhrystone An SIHFT strategy was implemented on this benchmark

ESA ESTEC December 9th 2015

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

A Trains / Feynaccarica Clark

#### **Backward Recovery**:

>> If a fault is detected at checkpoint, repeat both executions

#### **Forward Recovery**:

If a fault is detected at checkpoint, execute a third time and select output through a majority vote

ESA ESTEC December 9th 2015

|                                                                                                                                                                                                                                                                                            | Exe. Time<br>(us) | .text+<br>.init | .data        | .sbss | .bss   | Total        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|--------------|-------|--------|--------------|--|

| w/o<br>SIHFT                                                                                                                                                                                                                                                                               | 9,670             | 23,808          | 29,312       | 40    | 39,584 | 92,744       |  |

| w/ SIHFT                                                                                                                                                                                                                                                                                   | 19,833            | 25,292          | 29,440       | 20    | 68,880 | 123,632      |  |

| Diff.                                                                                                                                                                                                                                                                                      | +105%             | +6%             | <b>+0.4%</b> | +100% | +74%   | +33.3%       |  |

| ESA ESTEC         December 9th 2015    This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space |                   |                 |              |       |        | ThalesAlenia |  |

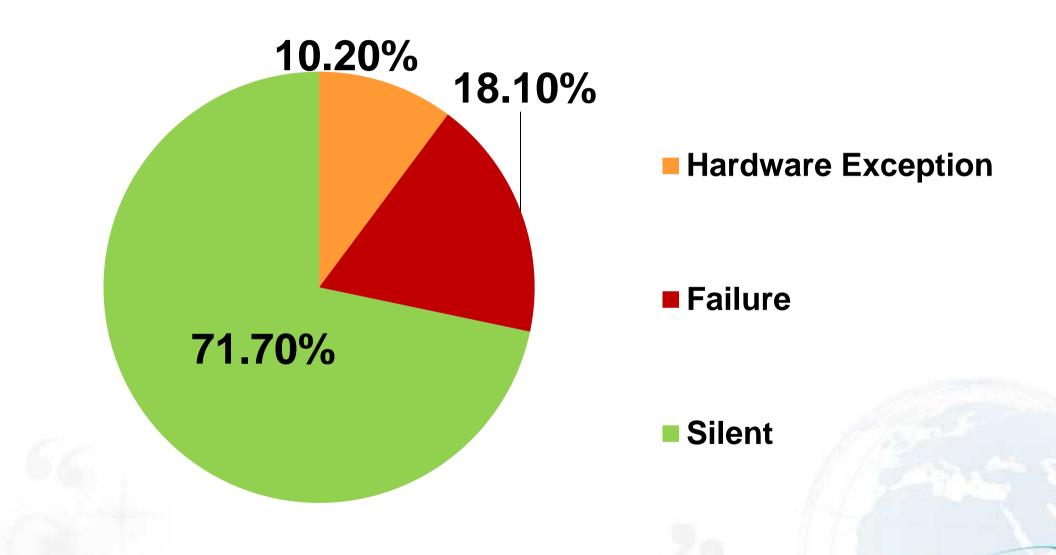

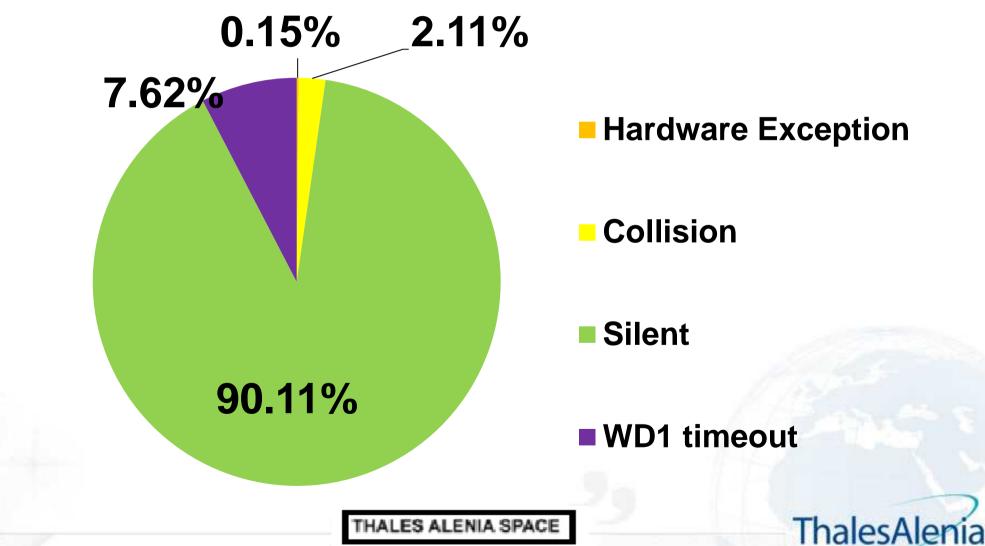

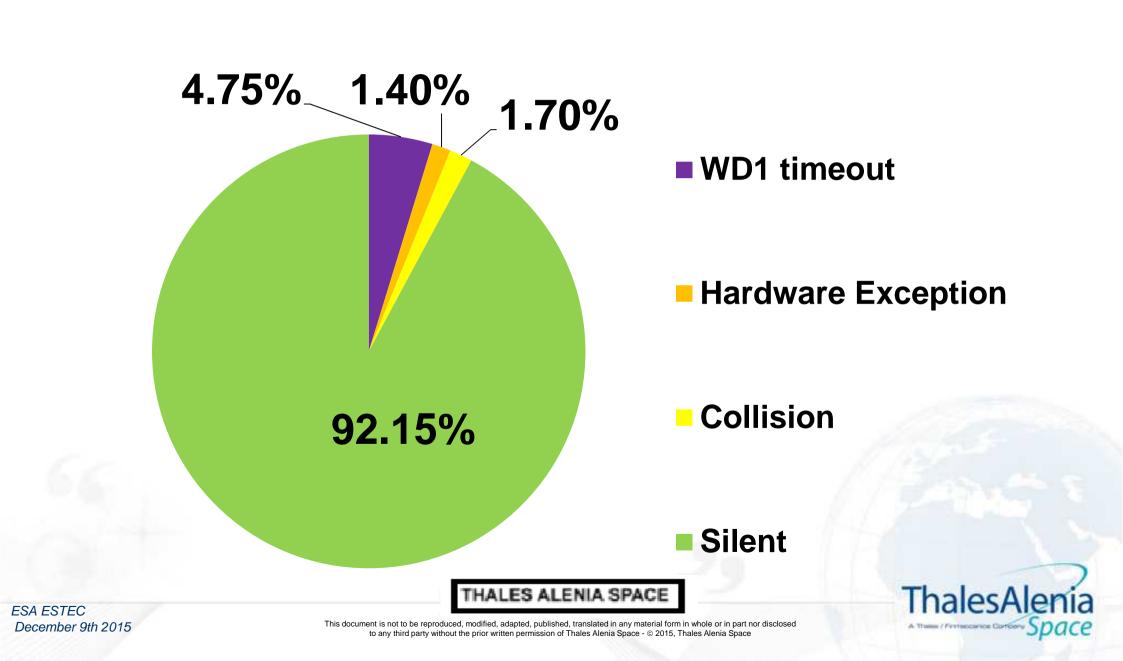

## Fault Injection Experiments

Software (SW)

Watchdog (TO)

Exception (EXC)

FAILURE

## •SILENT

THALES ALENIA SPACE

THALES ALENIA SPACE

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

30

**ThalesAlenia**

A Trainin / Frytheocartice Clarton

ESA ESTEC December 9th 2015

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

A Trainin / Frymocartical Clark

Results from this work were presented at the NSREC'15 conference held in Boston in July 2015.

- A paper describing the approach, the experimental methodology and the results was published on the December 2016 issue of IEEE Transactions on Nuclear Science.

- S. Esposito, C. Albanese, M. Alderighi, F. Casini, L. Giganti, M. L. Esposti, C. Monteleone, and M. Violante, "COTS-Based High-Performance Computing for Space Applications," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, 2015.

The implemented SIHFT solution is a viable way to implement space applications using COTS, meeting the dependability requirements of the domain.

Future solutions will leverage multicore architectures for fault tolerance implementation.

## 5- Hi-Rel cots project conclusion and possible developments

ESA ESTEC December 9th 2015

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space - © 2015, Thales Alenia Space

35

#### Main lesson learned for future developments:

- 1. Resources (memories) shall be interfaced directly with the CPU to use the full potentiality of power PC processing

- 2. I/O shall be managed by Hi rel FPGA and not by CPU

- 3. Future solutions will leverage multicore power PC architectures for fault tolerance implementation (i.e. majority voting) with Hypervisor in order to mitigate SW errors

#### Possible future development

#### High performance platform computer architecture

THALES ALENIA SPACE

ESA ESTEC

December 9th 2015