# SEFUW: SpacE FPGA Users Workshop, 3rd Edition

# Tuesday 15 March 2016 - Thursday 17 March 2016

**European Space Research and Technology Centre (ESTEC)**

SEFUW 2016 is organised with the support from CNES CTT and ESA's Data System Division

# Tuesday 15 March 2016

Registration and Early Morning Networking Break sponsored by CNES CCT and ESA's Data System Division (09:30 – 10:00)

### Welcome to SEFUW 2016 (10:00 - 10:25)

Presenter: Mr. DANGLA, David (CNES); Mr. MERODIO CODINACHS, David (ESA)

### Session: Design Experiences (10:25 – 12:10)

Chair: Mr. MERODIO CODINACHS, David (ESA)

| 10.06 | Implementation of Space-Industry IP : A Comparison of Space-Grade FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:25 | Presenter: Dr. BEDI, Rajan (Spacechips Ltd.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | The number and diversity of space-grade FPGAs offer many options when architecting satellite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | sub-systems. One-time programmable anti-fuse, flash and SRAM-based technologies, each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | with unique fabrics, present many interesting trade-offs when selecting the most appropriate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | device for your next mission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | Today, space-grade FPGAs are formally available from 350 µm to 28 nm nodes with advertised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | speeds ranging from 50 to 800 MHz. On-board storage varies from 55 kB to 50 MB with the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | latest devices offering high-speed serial links with data rates of 8.5 Gbps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | For some spacecraft sub-systems, <i>e.g.</i> high throughput payloads or localised control of a power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | supply, the system requirements quickly dictate the choice of FPGA. For some satellites, OEMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | have re-used devices from previous programs which in some cases has proven to be cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | effective, however, for others, this decision has resulted in expensive re-design, late delivery of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | hardware and over-budget projects.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | To avoid unnecessary over-design, some manufacturers of satellite sub-systems have started to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | compare space-grade FPGAs during the system architecture phase to allow them to make an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | informed decision and select the most appropriate device given their mission constraints, e.g.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | power consumption, cost, performance, reliability etc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | FPGA vendors offer unique device fabrics with each supplier promoting differently the capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | and the number of logic resources offered by their parts. Which FPGA is the most appropriate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | for your next mission? This paper compares the FPGA implementation of IP used by the space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | industry and offers an independent view of selecting the right device for your next spacecraft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10:55 | sub-system. FPGA development flow for future large space FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10.55 | Presenter: Mr. MANNI, Florent (CNES DC/TV/IN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | The FPGA available for Rad-tolerant or Rad-Hard applications are quite small (with regard to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | their commercial brothers). Some are SRAM based, many are antifusible based. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | development flow described inside the ECSS-Q-60-02 standard is well fitted for this kind of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | targets. The next generation of FPGA for space application will include bigger FPGA matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | most of them SRAM or flash based. The mix between biggest and reprogrammable matrix will                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | lead to longer FPGA development and new strategies to handle it. This kind of development will                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | match less easily with the ECSS standard. During this presentation two different FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | development examples will be described: one using FPGA Proasic3 and the other using the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | SOC Zynq.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11:20 | Prototyping a SOC on RTAX4000D for Solar Orbiter's Low Frequency Receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | Presenter: Mr. JEANDET, Alexis (Plasma Physics Laboratory)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

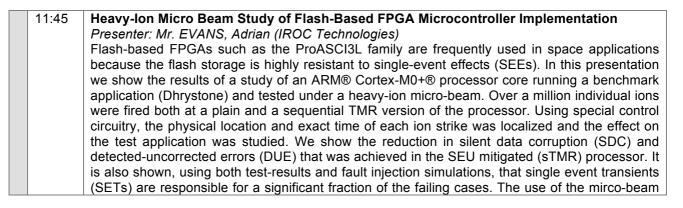

| 11:45 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | Cobham Gaisler develops the LEON3FT SPARC V8 fault-tolerant microprocessor that is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11:45 | Many space instruments using FPGA rely on the RTAX family, from the RTAX-250 to the RTAX-2000D but none of them embed a <b>RTAX-4000D</b> . For the first a RTAX-4000D will be onboard the <b>Solar Orbiter</b> (http://sci.esa.int/solar-orbiter/) spacecraft in the Low Frequency Receiver instrument ( <b>LFR</b> ) developed at the Laboratory of Plasma Physics (LPP) (http://www.lpp.fr/). The LFR is in charge of digitizing the E and B fields below 10kHz and processing them to extract basic parameters from the solar wind. In fact this need more RAM and logical resources than the RTAX2000D can provide, the reason for which the LPP decided to choose the RTAX4000D. In this workshop the LFR's FPGA prototyping will be presented from custom solderless socket solution to high level SOC debug and verification. <b>LEON3/GRLIB for Space-Grade Programmable Devices Update and Roadmap</b> <i>Presenter: Mr. ANDERSSON, Jan (Cobham Gaisler AB)</i> |

|        | available both as IP cores part of an IP library (GRLIB) that allows users to design their own custom system-on-chip (SoC) designs, and also as part of ready-made designs and devices. The GRLIB library currently provides template designs that allow users to target Xilinx Virtex-5QV, Microsemi RTAX, RT ProASIC3 and RTG4. The presentation will provide an update on the latest features supported and give a roadmap for future updates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | n: Industrial Experiences (12:10 – 12:35)<br>Mr. MERODIO CODINACHS, David (ESA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12:10  | <b>Feedback on Xilinx Virtex-5QV FPGA</b><br><i>Presenter: Mr. SEYCHAL, Florian (THALES ALENIA SPACE FRANCE)</i><br>A designer's approach is done on the last space-grade FPGA provided by Xilinx: Virtex-<br>5QV. The presentation gives details of features, performances and power consumptions of real<br>designs developed in Thales Alenia Space. The methodology used for Xilinx FPGAs is also<br>presented. Finally, some recommendations are delivered for designers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | n: FPGAs: High Performance (12:35 – 13:00)<br>Mr. MERODIO CODINACHS, David (ESA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12:35  | <b>SpaceWire and SpaceFibre on the Microsemi RTG4 FPGA</b><br><i>Presenter: Mr. MCCLEMENTS, Chris (STAR-Dundee)</i><br>To explore the implementation of SpaceFibre and SpaceWire in the new Microsemi RTG4<br>FPGA, a demonstration system has been developed which implements the STAR-Dundee<br>SpaceWire and SpaceFibre IP cores on the RTG4 development kit. In addition to the RTG4<br>development kit, the demonstration system uses the STAR-Dundee SpaceFibre and SpaceWire<br>FMC interface card, STAR Fire SpaceFibre interface and diagnostics unit, and a SpaceWire<br>Brick Mk3 USB. The system interconnects between RTG4 development boards using the<br>SpaceFibre and SpaceWire interfaces of the FMC interface boards. Each FMC board features<br>two SpaceFibre interfaces and four SpaceWire interfaces.<br>The RTG4 FPGA design has two SpaceFibre interfaces running at a bit rate of 2.5 Gbit/s and<br>four SpaceWire interfaces running at 200 Mbit/s. The SpaceFibre interfaces are configured with<br>eight virtual channels, with virtual channels 0 to 3 connected to the SpaceWire interfaces. The<br>design makes use of the new features of the RTG4 including the SpaceWire interfaces. The<br>design makes use of the new features of the RTG4 including the SpaceWire interfaces. The<br>design makes use of the new features of the RTG4 including the SpaceWire interfaces. The<br>design makes use of the new features of the RTG4 including the SpaceWire lock recovery<br>circuit and the high speed SERDES interfaces. The demonstrator system uses a STAR Fire as<br>a high speed SpaceFibre link. Another STAR Fire unit can be used in analyser mode to<br>capture data travelling over SpaceFibre. In parallel, one Brick Mk3 is used as a lower speed<br>SpaceWire source PC. The low speed SpaceWire traffic generated by the Brick MK3 is sent and<br>received over the same SpaceFibre link as the high speed data traffic. Thanks to the inbuilt QOS<br>for every virtual channel, the low speed traffic is not affected by the high speed traffic used to<br>saturate the link, as they travel over different virtual channels.<br>The use of the RTG4 with th |

| Sessio | rking Luncheon (13:00 – 14:20)<br>n: Fault Tolerance Methodologies and Tools (14:20 – 15:35)<br><i>Mr. DANGLA, David (CNES)</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14:20  | <b>Configuration Scrubbing and Mitigation Approaches for the Zynq System-on-Chip</b><br><i>Presenter: WIRTHLIN, Mike (Brigham Young University)</i><br>The Xilinx Zynq programmable system-on-chip offers new capabilities for spacecraft systems by<br>integrating two ARM A9 processors along with programmable logic on the same silicon die.<br>Tightly coupling embedded processors with a programmable logic fabric facilitates hybrid<br>computing systems that use the processors for higher-level sequential processing and the<br>programmable logic for parallel computing, low-level I/O, and stream processing's. A number of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | CubeSat satellite systems are planning on exploiting this novel architecture. Like all SRAM programmable logic, the FPGA resources on the Zynq processor are susceptible to single-event upsets (SEU). Conventional SEU mitigation techniques such as configuration scrubbing and TMR are necessary for protecting the programmable logic within the Zynq. This presentation will summarize a number of novel techniques for configuration scrubbing using the new PCAP configuration interface. In addition, a hybrid scrubbing system that exploits both the internal scan feature of the 7 series FPGA as well as the PCAP interface will be described.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14:45     | <b>SET effects analysis and mitigation on Flash-based FPGAs</b><br><i>Presenter: Prof. STERPONE, Luca (Politecnico di Torino)</i><br>Flash-based Field Programmable Gate Arrays (Flash-based FPGAs) are becoming more and<br>more interesting for safety critical applications due to their re-programmability features while<br>being non-volatile. However, Single Event Transients (SETs) in combinational logic represent<br>their primary source of critical errors since they can propagate and change their shape<br>traversing combinational paths and being broadened and amplified before sampled by<br>sequential Flip-Flops. In this paper the SET sensitivity of circuits implemented in Flash-based<br>FPGAs is mitigated with respect to the working frequency and different FPGA routing<br>architecture. We outline a parametric routing scheme and placement and routing tools based on<br>an iterative partitioning algorithm able to generate high performance circuits by reducing the<br>wires delay and reducing the SET sensitivity. The efficiency of the proposed tools has been<br>evaluated on a Microsemi Flash-based FPGA implementing different benchmark circuits<br>including a RISC microprocessor. Experimental results demonstrated the reduction of SET<br>sensitivity of more than 30% on the average versus state-of-the-art mitigation solutions and a |

| <br>45.40 | performance improvement of about 10% of the nominal working frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15:10     | <b>FT-UNSHADES2: the User Friendly Framework as an interface for designer support</b><br><i>Presenter: Dr. HIPÓLITO, Guzmán-Miranda (Universidad de Sevilla)</i><br>FT-UNSHADES2 is a framework dedicated to fault injection in both ASIC netlists and FPGA<br>devices. This system has been conceived to perform, in the same environment, large injection<br>campaigns and detailed analysis without additional user efforts.<br>The team at Universidad de Sevilla has created a system that is remotely accessible, avoiding<br>the necessity of having the hardware device present. Its remote access via web can be<br>installed, for example, in the intranet of a company.<br>The system allows with the same framework, both large fault injection campaigns and detailed<br>analysis to study the effects of single faults.<br>The design preparation procedure, and few examples of use, ASIC campaign mode, ASIC<br>detailed analysis and FPGA campaign mode are three ways of using FTU2, integrated in the<br>same framework.<br>In this presentation we describe the new framework for making fault injection in different cases<br>and procedures. The system in Sevilla is now accessible by all users because is offered as<br>online access.                                                                                                                                |

|           | n: Reconfigurability (15:35 – 16:00)<br>Mr. DANGLA, David (CNES)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15:35     | Dyplo: software driven threaded FPGA development using partial reconfiguration<br>techniquesPresenters: Ms. RUTTEN, Inge (Topic Embedded Systems), Mr. VAN DEN HEUVEL, Dirk<br>(Topic Embedded Products)Dyplo is a DYnamic Process LOader, enabling software-like programming capabilities on an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Dyplo is a DYnamic Process LOader, enabling software-like programming capabilities on an FPGA such as threading, dynamic process switching and on-the-fly context switching. This allows seamless integration of FPGA logic in a typical software application without the need of deep FPGA design knowledge. A software API gives you full control over functionality run on the FPGA as well as the data transaction of processes running on the FPGA and CPU. The concept behind Dyplo makes use of partial reconfiguration technology, supporting currently only Xilinx FPGA technology. Using an infrastructure that spans both the FPGA and operating system of the processor is a unique solution. This creates all kinds of special capabilities such as functional redundancy, self-repairing systems and time-division-multiplexing of FPGA fabric. This presentation will give you more insight in the concept, a description of the demonstration we will show and a glance of the road ahead where Topic goes with this concept.

Topic Embedded Products delivers embedded solutions to accelerate our customers development, forming a complete ecosystem of hardware and software building blocks which are all combinable and compatible. Topic is also one of 10 premier partners world-wide of Xilinx.

Networking Coffee Break sponsored by CNES CCT and ESA's Data System Division (16:00 – 16:30)

Demo Session and Cocktail Reception sponsored by CNES CCT and ESA's Data System Division (16:30 – 18:30) Chair: *Mr. DANGLA, David (CNES)*

# Wednesday 16 March 2016

SEFUW Intro – Opening Remarks (08:50 - 09:00) Presenter: Mr. DANGLA, David (CNES); Mr. MERODIO CODINACHS, David (ESA)

Session: FPGA Vendors (09:00 – 10:30)

Chair: Mr. FERNANDEZ-LEON, Agustin (ESA)

| 09:0 | 0 Microsemi RTG4 FPGAs – Product Overview, Update on Radiation and Reliability Testing                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Presenter: Mr. O'NEILL, Ken (Microsemi)                                                                                                                                                 |

|      | Dramatic increases in sensor resolution in remote-sensing space payloads are causing a                                                                                                  |

|      | processing bottleneck, as downlink bandwidth is not keeping pace. Operators require on-board                                                                                            |

|      | processing so that satellites send processed information, not just raw data. It is a growing                                                                                            |

|      | challenge for the designers of the hundreds of remote sensing satellite payloads launched each year. Microsemi's RTG4 Flash-based radiation tolerant FPGAs are now being applied to the |

|      | problem, combining high-speed signal processing with special built-in radiation mitigation                                                                                              |

|      | techniques to keep systems operational in harsh radiation environments. In addition, these                                                                                              |

|      | Flash FPGAs maintain low static power, and contribute significant dynamic power savings. With                                                                                           |

|      | more than 150,000 logic elements and up to 300 MHz system performance, this new class of                                                                                                |

|      | radiation tolerant FPGA incorporates significantly more registers, combinatorial logic, DSP                                                                                             |

|      | Mathblocks, and transceivers than were previously available with any radiation-tolerant FPGA                                                                                            |

|      | technologies.                                                                                                                                                                           |

|      | This presentation will provide an overview of the architecture and technology of the RTG4                                                                                               |

|      | FPGAs, and will then cover the latest information on reliability testing and radiation effects                                                                                          |

|      | analysis. Product qualification schedules and availability of flight units will also be discussed.                                                                                      |

| 10:0 |                                                                                                                                                                                         |

|      | Presenter: Mr. BANCELIN, Bernard (ATMEL Nantes S.A.S.)                                                                                                                                  |

|      | ATMEL keep up on enhancing its AT40K radiation-hardened FPGA family composed of the AT40K, ATF280, AFee560 and ATF697 devices. SpaceFpgaDesigner, the family design                     |

|      | software suite, has been significantly enhanced, including Mentor Precision and Figaro latest                                                                                           |

|      | releases. The new Hardware Macro flow now offers an optimally placed and routed, ready to                                                                                               |

|      | use, 1553 IP. Analysis are on-going for SpaceWire, PCI and CAN. Using ATMEL space                                                                                                       |

|      | packaging expertise, the ATF697 device efficiently combine in a SiP (system in package) the                                                                                             |

|      | ATF280 and the AT697 LEON2FT processor, allowing a significant footprint reduction for a                                                                                                |