**High Performance COTS** based computer **FPGA** implementation

SpacE FPGA Users Workshop 3<sup>rd</sup> edition

European Space Research and Technology Centre

Noordwijk, The Nederland

16 March 2016

Space Systems –Functional Avionics On board processing and S/W (TSOEF2) olivier.notebaert@airbus.com

**OPEN**

# High Performance COTS based computer FPGA implementation

- High Performance Processing needs

- The High Performance COTS Based Computer Study (HiP-CBC)

- Hi-P CBC FPGA implementation

#### **High Performance Processing Needs**

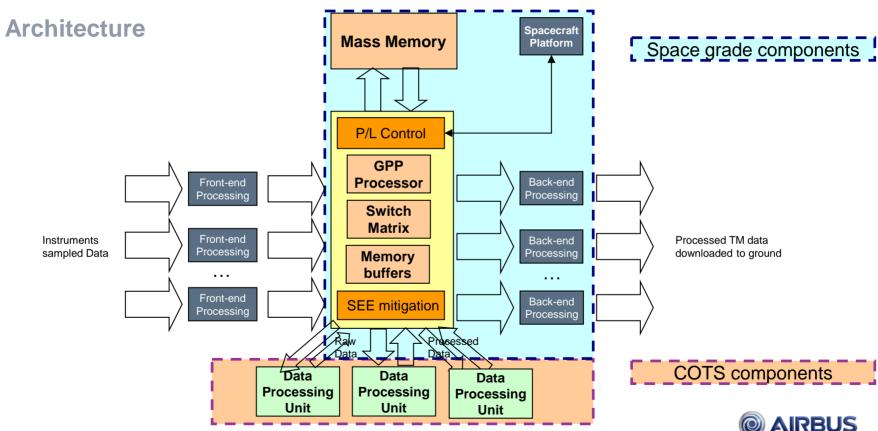

### **High Performance Payload Processing Needs**

- Payload / Instruments data processing

- Data-flow architecture

- High data rate front-end interface for raw data filtering and digitalization

- Mission dependant on-board data processing

- Data buffering in fast local memory

- Control loops / latency requirements (in few cases)

- Data storage in high capacity mass memory

- Processing performance / power consumption

- Industrial efficiency requires

Lower cost, Modularity, Flexibility...

Reprogrammable Devices

FPGAs and micro-processors

(DSP's, multi-cores, many cores,...)

**OPFN**

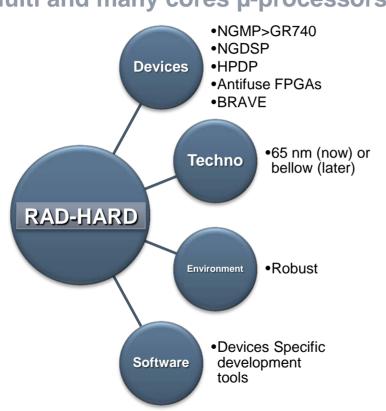

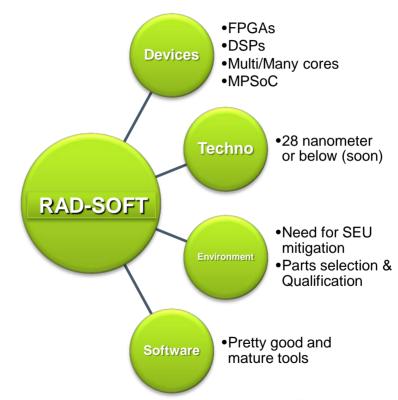

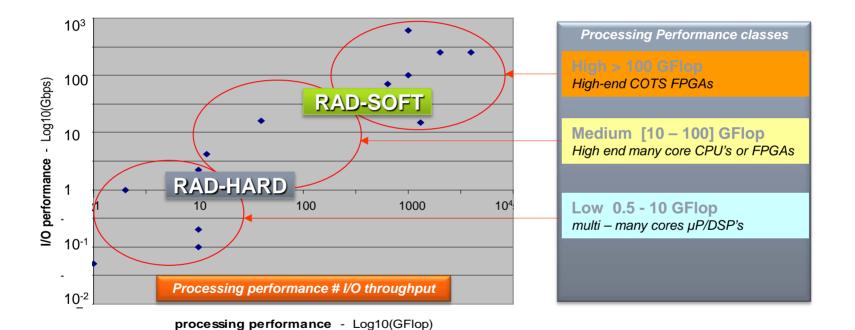

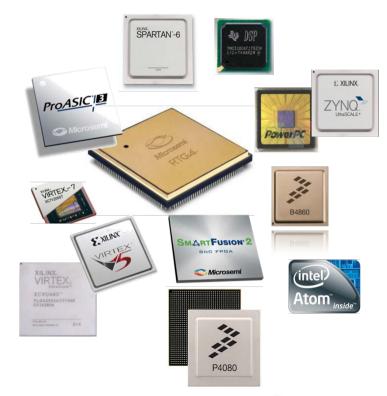

# High Performance Reprogrammable devices Multi and many cores µ-processors / reconfigurable FPGA's

#### Commercial µProcessors and FPGA's

- Dynamic roadmap with attractive products

- μProcessors: DSP6727, PPCs, ARM, ATOM...

- FPGA's: Virtex, ProASIC

- MPSoC: Zynq

- Manageable radiations issues

- Destructive effects

- Latch-up free or can be mitigated

- Total dose acceptable for many LEO missions

- Some products with "rad-hard" characteristics

- Non permanent effects require mitigation

RAD-SOFT components

May be used for a wide range of missions

(not for all)

- Robust architecture for COTS based processing

- Use existing COTS devices (DSP, FPGA's)

- Mitigate radiation effects from a robust and programmable external device (SmartIO)

- Applications to payload data processing

- Study priorities

- Mission scalability

- Independence of the mitigation mechanism w.r.t. processing device

- High data bandwidth standard interfaces

- Suitable for different types of missions

- TRL 5-6 demonstrator

- Mature technology

- DSP as COTS processor

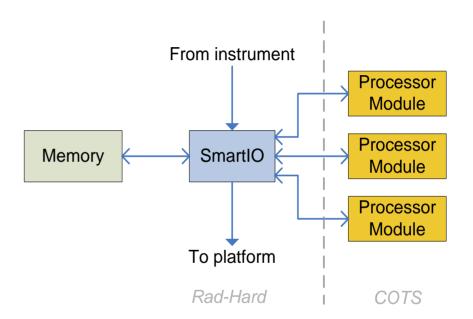

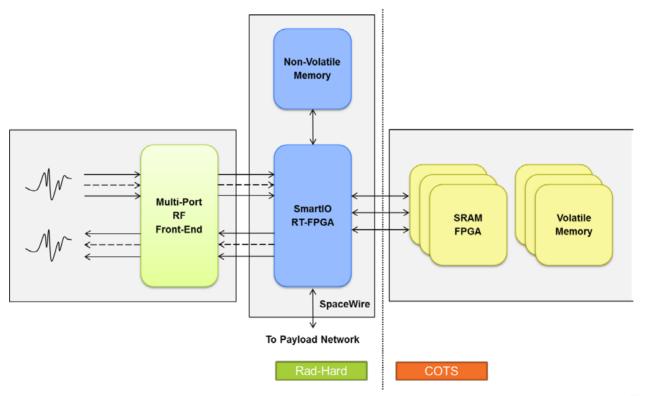

#### Concept

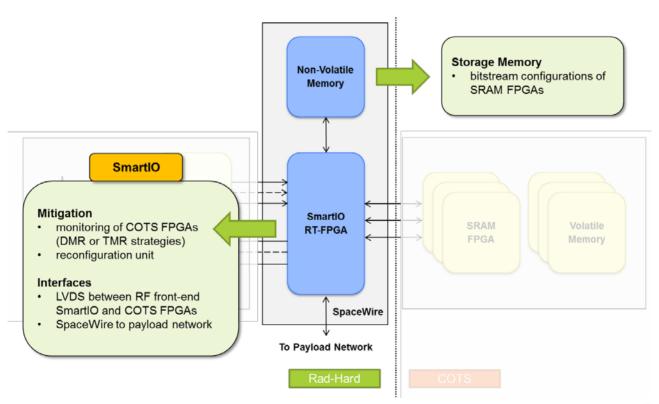

- SmartIO

- Rad hard component

- in charge of the isolation between the COTS world and the "rad hard" world.

- Controls several COTS components

- Provides scalable fault mitigation functions

- Buffers instrument data in a fast local memory, and replays it in case of error

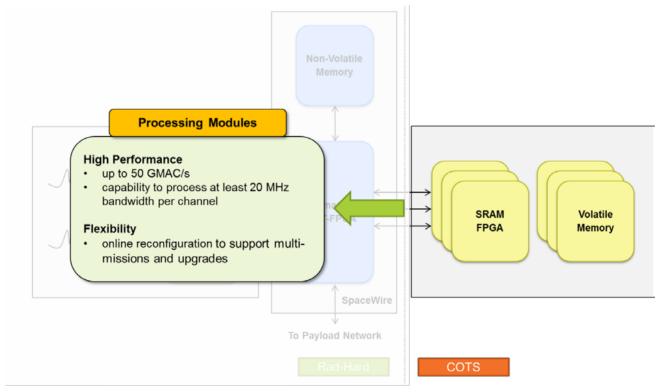

- Several Processor Modules

- Implemented with µProcessor or FPGA

#### **Concept**

- SmartIO

- Rad hard component

- in charge of the isolation between the COTS world and the "rad hard" world.

- Controls several COTS components

- Provides scalable fault mitigation functions

- Buffers instrument data in a fast local memory, and replays it in case of error

- Several Processor Modules

- Implemented with µProcessor or FPGA

#### **Benefits**

- SmartIO / PM link is a standard HSSL

- LVDS, SpW, SpFi, SRIO, PCIe\_serial, GbitEthernet

→ flexibility, technology independence

- PM's are slaves of the SmartIO

- · simplicity of the fault model

- SmartIO in HW+SW to manage fault mitigation

→ versatility

- Batch processing and results checks with signature

- → performance

- Scalable Architecture

- → adaptable to mission requirements

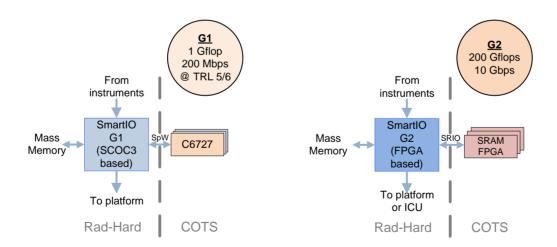

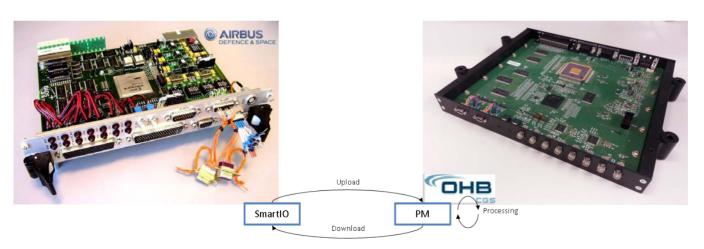

#### Demonstrator

SmartIO with SCoC3 (Leon3) for control, monitoring and reconfiguration

**High Performance COTS Based Computer (HiP-CBC)**

- DSP board developed by OHB<sub>CGS</sub> in Milano with a DSP 6727 from TI

- Demonstration Software on Smart I/O and Processing Module S/W

- Performance and availability model

#### **Hi-P CBC FPGA implementation**

## **FPGA Technologies**

| Feature                                 | Antifuse        | Flash                                       | SRAM                |

|-----------------------------------------|-----------------|---------------------------------------------|---------------------|

| Reprogrammable                          | No              | Yes but limited (hundreds of times)         | Yes                 |

| Volatile Configuration                  | No              | No                                          | Yes                 |

| Online reconfiguration                  | No              | Not Recommended                             | Yes                 |

| Capacity                                | Low             | Medium                                      | Very High           |

| DSP Performance                         | Low (125 MHz)   | Medium (350 MHz)                            | Very High (700 MHz) |

| Soft Error Sensitivity (SEFI, SEU, SET) | Low to Very Low | Medium to Low (configuration memory immune) | High                |

| TID Tolerance                           | High            | Low to medium                               | High                |

## **Application to SDR Payloads**

- Reprogrammable FPGA's are essential for Payload / Instrument Processing

- High performance COTS Based computer study

- Demonstration with SCoC3 + DSP C6727

- FPGA implementation in development (ACTEL + SRAM based FPGA) for Software Defined Radio