# SEFUW: SpacE FPGA Users Workshop 3<sup>rd</sup> Edition

ATF280E2J-E 0706 6T8044

> David Merodio Codinachs (ESA) David Dangla (CNES)

# European Space Research and Technology Centre (ESTEC) http://www.esa.int/SPECIALS/ESTEC/index.html

# Coffee breaks and Cocktail reception during the Demo Session are sponsored by

Communautés de Compétences Techniques

# Exchange of highly valuable information and experience among FPGA users, researchers, CAD vendors and FPGA vendors

# esa

#### http://spacefpga.atmel-nantes.fr/spacefpga/

**ATMEL** Aerospace FPGA working group: Workshops and website

*Workshop* on Fault Injection & Fault Tolerance in space FPGAs (2009)

#### 1<sup>st</sup> **SEFUW**, Oct **2012**

#### 2<sup>nd</sup> SEFUW, Sep 2014

|                                                                                     | Calepot More V                                                                                                                                                                                                                              | Europe/Amsterdam                                                         | <ul> <li>D. Nerodio Codinachs +</li> </ul> |  |  |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|--|--|

| ©esa と                                                                              | CNES SEFUW: Space Fr                                                                                                                                                                                                                        | nes SEFUW: SpacE FPGA Users Workshop, 2nd Edition                        |                                            |  |  |

| ESTEC)                                                                              | 16-18 September 2014<br>European Space Research a                                                                                                                                                                                           | and Technology Centre                                                    |                                            |  |  |

|                                                                                     | Note: all available presentations have                                                                                                                                                                                                      | been posted on the website                                               |                                            |  |  |

| BFUW 2014<br>Sponsor: Thales<br>Communications B.<br>Security<br>Cell for Abstracts | All FPGAs share several design methods<br>FPGAs are currently heavily used in mo-<br>technologies too: Flash-based and SRAI<br>The aim of this workshop is to address o                                                                     | st electronic equipment for space yet<br>M-based.                        | there are other emerging                   |  |  |

| View my Abstracts<br>Submit Abstract<br>tailed Programme                            | covering (not limited too):<br>- general design, verification and test is<br>- performance achievements and potent<br>- power consumption achievements and<br>- design tools performance, good practia                                      | tial problems<br>I potential issues<br>res and potential limitations     |                                            |  |  |

| Conference<br>Ny Contributions                                                      | <ul> <li>radiation mitigation techniques, tools<br/>already been presented at RADECS, NS<br/>- trends of PPGA usage in space applicat<br/>- lessons learned: ensuring successful an<br/>- choosing the best PPGA type for our su</li> </ul> | REC and SEE Symposium)<br>tions<br>nd safe use of FPGA in space applicat |                                            |  |  |

| jistration<br>Modify my Registration<br>Sidpent List                                | corport license limitations / changes / li<br>package and assembly challenges     companion non-volatile memory (whe                                                                                                                        | ITAR / EAR                                                               |                                            |  |  |

| ccomodation<br>lenue and Practical<br>Information                                   | The PPGA vendors ATMEL, MICROSE2<br>questions.<br>Presentations from at least the major de                                                                                                                                                  |                                                                          | and will be available for                  |  |  |

| ast and Related Events                                                              | Have you not been contasted set to need                                                                                                                                                                                                     | transment of Instrumental Instruments                                    | inv? Bease contact us                      |  |  |

http://www.esa.int/TEC/Microelectronics/SEMV57KIWZF\_0.html

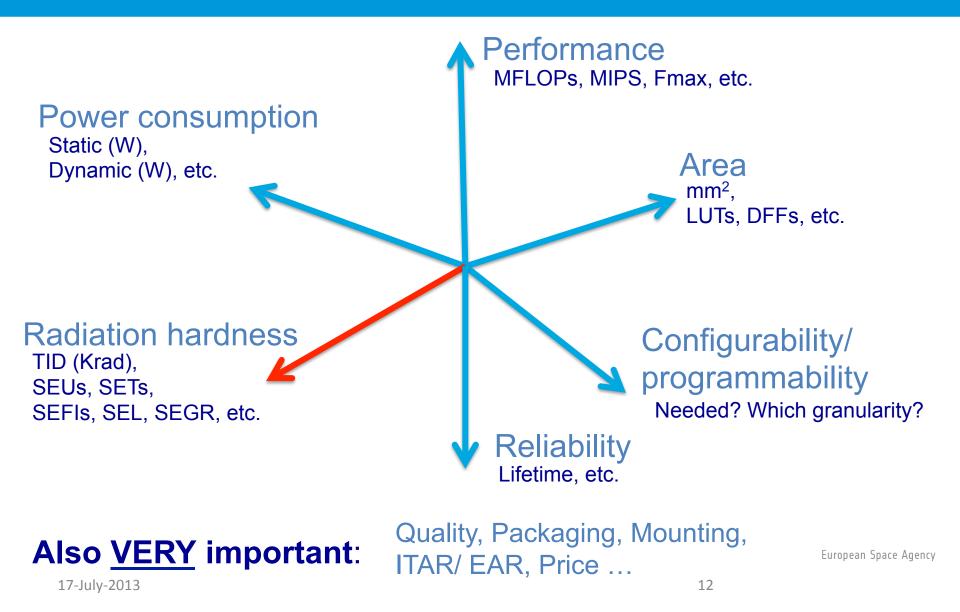

## **FPGA updates/ trends**

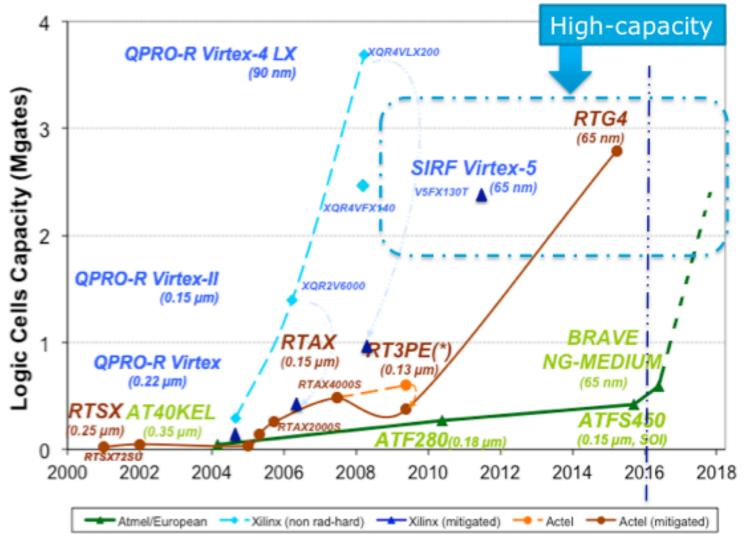

- 1. New FPGA vendors addressing space

- 2. Larger and higher performance FPGAs are becoming available

- 3. COTS FPGAs use is growing

- 4. FPGA domain usage expands:

- a. High performance using FPGAs

- b. Re-programmability (already addressed in previous SEFUW editions)

# FPGA updates/ trends (I): FPGA vendors addressing Space

✓ Space FPGA vendors in SEFUW 2016 and also in previous SEFUW editions:

✓ NEW FPGA vendors for Space in SEFUW 2016:

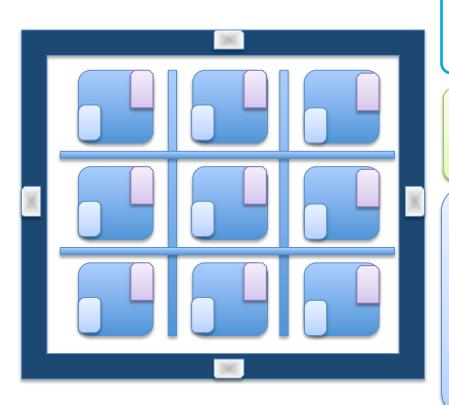

# 1. FPGA Architectural features (general)

#### **Logic fabric**

**Inter- connection**

**Internal memory**

**Clock generation** (PLLs, DLLs,...)

Arithmetic (Multipliers, DSP, ...)

**Flexible IOs**

**High speed serial links**

**Embedded processors**

**Other hard-macros (PCIe, ...)**

**1. FPGA "Eras"** (based in their architecture):

- 1. First: FPGA fabric (e.g. RTSX-SU)

- Second: FPGA fabric and Internal Memory (e.g. RTAX-S, ATF280F)

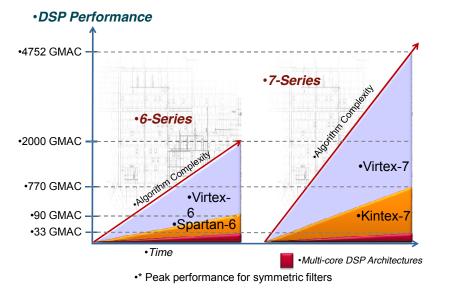

- Third: FPGA fabric, Internal Memory and specialized Hard-macros (DSP, etc). (e.g. Virtex-4/5, RTAX-DSP, RTG4, NG-MEDIUM)

- Fourth: SoC FPGA (e.g. Zynq, Smartfusion2, Cyclone V SoC, Arria V SoC)

- 2. Radiation hardened FPGA and COTS FPGAs:

- 1. COTS FPGAs: entered the 4<sup>th</sup> Era some years ago

- 2. Radiation hardened FPGAs: "behind" the COTS timeline, but better radiation performance

## FPGA updates/ trends (II): Larger and higher performance FPGAs (II)

Space Agency

# FPGA updates/ trends (III): COTS FPGAs (I)

ency

1. During subsystems development:

COTS FPGAs are used for bread boarding (**BB**)

- When moving to EQM and FM models, which FPGA is used? The "nominal" choice is:

- a. Radiation hardened FPGA: if the performance can be achieved

- b. ASIC: if the performance cannot be achieved

- Due to the changing programmatic constraints (shorted lifetime, better-faster-cheaper, etc.). Specially relevant for Nanosatellites and Cubesats:

a. COTS FPGA are proposed for EQM and FM

Understanding their radiation performance, mitigation techniques and guidelines on how to use them is paramount. The overall Quality (ECSS-Q-ST-60-13C) is paramount.

# FPGA updates/ trends (III): COTS FPGAs (II)

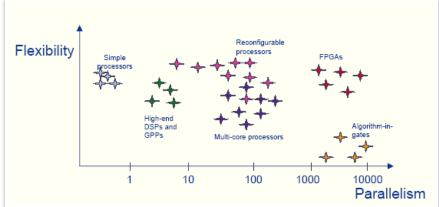

### FPGA updates/ trends (IV): Domain usage expands

#### 1. Re-configurability, High Performance

Source: Xilinx

**Source**: BDTi, "Benchmarking Multithreaded, Multicore and Reconfigurable Processors", 2006

#### https://indico.esa.int/indico/event/130/timetable/#all.detailed

# The agenda has been distributed among the participants

|                                                          |                                                                                                           | indico.esa.int/indico/event/130/timetable/#all.detailed                                 | 0 1 1                                    |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------|--|

| esa cres SEFUW: Space FPGA Users Workshop, 3rd Edition   |                                                                                                           |                                                                                         |                                          |  |

| (ESTEC)<br>Europe/Amsterdam timezone                     |                                                                                                           | -17 March 2016<br>ropean Space Research and Technology Centre                           |                                          |  |

| SEFUW 2016                                               | < Tue 15/0                                                                                                | 3 Wed 16/03 Thu 17/03 All days                                                          |                                          |  |

| Sponsors: CNES CCT and<br>ESA's Data System<br>Division  |                                                                                                           | Print PDF Full screen Detailec                                                          |                                          |  |

| Call for Abstracts L View my Abstracts L Submit Abstract | Demo Session and C     Design Experiences     FPGA Vendors     FPGAs: High Perform     see more  Tue 15/3 |                                                                                         |                                          |  |

| Detailed Programme<br>Contribution List                  |                                                                                                           |                                                                                         |                                          |  |

| Registration                                             | 09:00                                                                                                     |                                                                                         |                                          |  |

| Accomodation<br>Venue and Practical<br>Information       | 1                                                                                                         | Registration and Early Morning Networking Break sponsored by CNES CCT and E<br>Division |                                          |  |

| Past and Related Events                                  | 10.00                                                                                                     | Newton 1 and 2, European Space Research and Technology Centre (ESTEC)                   | 09:30 - 10:00<br>Mr. David DANGLA et al. |  |

| SEFUW Dinner                                             | ,                                                                                                         | Newton 1 and 2, European Space Research and Technology Centre (ESTEC) 10:00 - 10:25     |                                          |  |

| For information please                                   |                                                                                                           | Implementation of Space-Industry IP : A Comparison of Space-Grade FPGAs                 | Dr. Rajan BEDI<br>10:25 - 10:55          |  |

| write to                                                 |                                                                                                           | FPGA development flow for future large space FPGA                                       | Mr. Florent MANNI                        |  |

| Sefuw@esa.int                                            |                                                                                                           | Newton 1 and 2, European Space Research and Technology Centre (ESTEC)                   | 10:55 - 11:20                            |  |

|                                                          |                                                                                                           | Prototyping a SOC on RTAX4000D for Solar Orbiter's Low Frequency Receiver.              | Mr. Alexis JEANDET                       |  |

|                                                          | 1                                                                                                         | Newton 1 and 2, European Space Research and Technology Centre (ESTEC)                   | 11:20 - 11:45                            |  |

|                                                          | 1                                                                                                         | EON3/GRLIB for Space-Grade Programmable Devices Update and Roadmap.                     | Mr. Jan ANDERSSON                        |  |

|                                                          | 12:00                                                                                                     | Newton 1 and 2, European Space Research and Technology Centre (ESTEC)                   | 11:45 - 12:10                            |  |

# Agenda (II)

#### https://indico.esa.int/indico/event/130/timetable/#all.detailed

|                      | Indico.esa.int/indico/event/130/overview                                                                                                                                                                                                                         |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ∑ sefuw@esa.int      | The FPGA vendors ALTERA, ATMEL, MICROSEMI and XILINX will present updates and will be<br>available for questions.<br>A major update on the European FPGA status will be presented.<br>Presentations from at least the major design groups (Primes) are expected. |  |  |

|                      | Have you not been contacted yet to present and are you interested in presenting?: Please contact us and/or submit your abstract.<br>Do you need space for demonstrating hardware and/or a booth? Please contact us.                                              |  |  |

|                      | The workshop duration will be 3 days.<br>Attendance to the workshop is free of charge.                                                                                                                                                                           |  |  |

|                      | It is advised to register as soon as possible in order to ensure your place.<br>Registration is required via the website not later than 28 February 2016.                                                                                                        |  |  |

| SEFUW 2016 Book of   | The materials presented at the workshop are intended to be published on this website after the event.<br>All material presented at the workshop must, before submission, be cleared of any restrictions                                                          |  |  |

| Abstracts: available | preventing it from being published on the website.                                                                                                                                                                                                               |  |  |

| online               | Starts 15 Mar 2016 09:30       European Space Research and Technology         Ends 17 Mar 2016 18:00       Centre (ESTEC)         Europe/Amsterdam       Newton 1 and 2                                                                                          |  |  |

|                      | Keplerlaan 1 2201AZ Noordwijk ZH The<br>Nettermands                                                                                                                                                                                                              |  |  |

|                      | Mr. Dangla, David<br>Mr. Merodio Codinachs, David                                                                                                                                                                                                                |  |  |

| Powered by Indico    |                                                                                                                                                                                                                                                                  |  |  |

#### 1. Sessions:

Agenda (III)

- a. FPGA Vendors

- b. Design experiences

- c. Industry experiences

- d. FPGAs: High Performance

- e. Reconfigurability

- f. Radiation

- g. Fault Tolerance Methodologies

#### 2. Demo session

# **Organization notes**

#### 1. Presenters:

- a. Provide the presentations (preferably during the breaks, latest the break prior to your presentation) or have your laptop ready.

- b. Do you agree on having it available at the ESA website? <u>Default: YES</u> (the final version can be provided another day)

#### 2. Attendees:

a. Do you agree to be included in the attendees list? **Default: YES**

# 1. Networking Coffee Break sponsored by CNES CTT and ESA TEC-ED

2. Networking Luncheon at ESTEC main canteen

#### **3. Wireless access**:

a. Login and password included at the back of your visitor badge. Valid throughout the workshop

**SSID**: **esa-public** Authentication: Open **Username**: *d.merodiocodinachs* **Password**: *xxxxx*

If your badge does NOT include this information, please report to the Registration Desk

# Restaurant: Iets Anders in Bistro Bardot

**Date**:16<sup>th</sup> March 2016 At 8pm

Address: Pickeplein 4, 2202 CK Noordwijk

Price: 43 EUR

The price includes a 3 course menu and drink arrangement.

#### **Confirmation: Before lunch time** (if not done yet)

# **ENJOY THE WORKSHOP !!!**