# FINAL PRESENTATION DAYS 2016

**Control Loop Processor -**

Platform for hard real time space applications

M. Ruiz, J-B. Feron, H. de la Vallée S.A.B.C.A.

**D PERIMETER**

### **ARCHITECTURE**

- **SOFTWARE DEVELOPMENT ENVIRONMENT**

- EXAMPLE OF APPLICATIONS

### **SUMMARY**

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

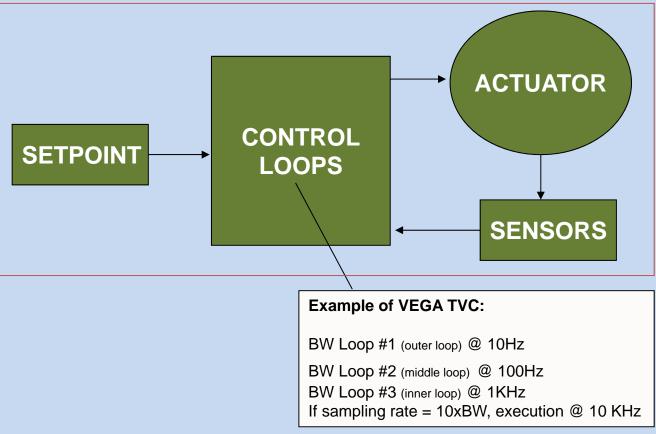

### Targeted needs characteristics

- One to several nested control loops with tight processing constraints

- Light to moderate interaction with equipment communication busses

- □ Tight interaction with on-board interfaces (sensors, PWM...)

- Most complex loop is often the inner one, e.g.

### +/- 1K to 10K arithmetic operations @1-10 kHz

### Limited implementation options are available for space

- Analog solution

- not always feasible if loop is too complex

- Hardwired digital logic on an ASIC/FPGA

- Must be tailored/redesigned from mission to mission (high non-recurrent cost)

- May be subject to ITAR

- SW implementation on a general purpose microprocessor or DSP

- May lead to real time issues or high cost solution

#### Towards Control Loop Processor

- Deterministic Behavior ASSP

- Application programmable by SW (no OS) or intuitive interface

- High data processing efficiency when needed

- ITAR free solution (for ASSP at least)

- Commercial product is targeted with Software Development Environment

- Tolerant to radiation effects

- **D** Tailored CLP alternatives: tunable solutions at RTL level to fit application needs

Ed9 Rev2 This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

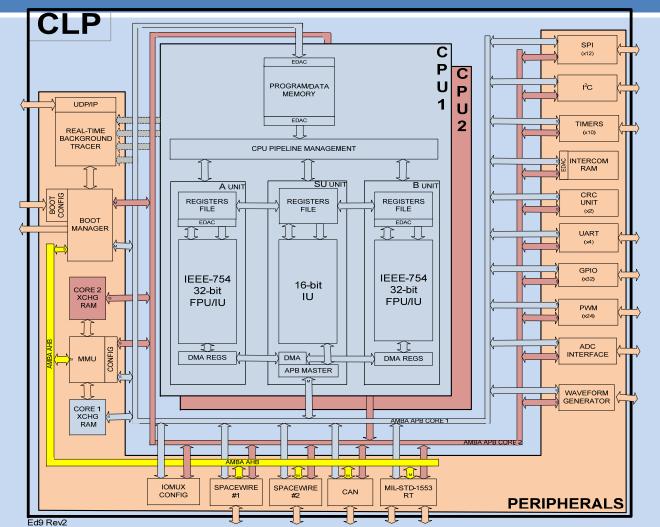

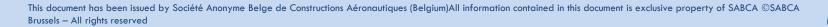

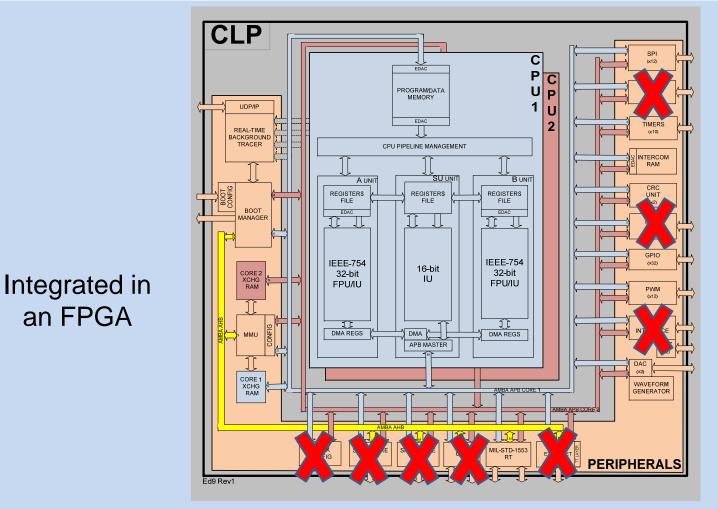

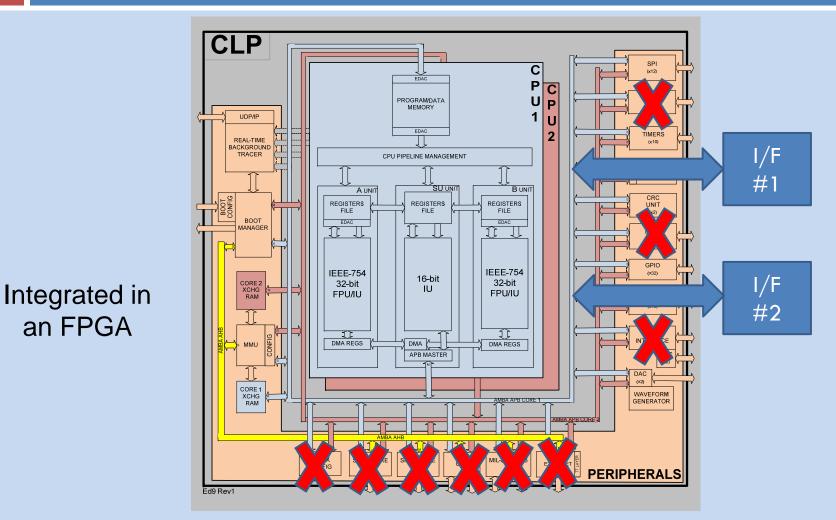

### Dual-CPU

- **D** Two-axis control or other partioning models

- RISC architecture

- SIMD approach

- For complex arithmetics (vectorial control)

- Deterministic Behaviour

- No caches

- No interrupts

- No operating system

- I/O servicing by SW is performed by polling or DMA

- Each I/F has dedicated or shared registers/memory with SW

- Each I/F can work in a stand-alone fashion

### Scheduling of SW tasks made with time slots controlled by timers

### Two 32-bit IEEE-754 FPU per CPU

- Enable high dynamic data usage

- Saturating arithmetic to avoid overflow

- Two large register files (RGP0 to RGP511)

- 16/32-bit integer operations are possible

- One 16-bit IU per CPU

- One Register File

- One 32768x39bits Program Memory per CPU

- Available for data storage if required

- One on-chip APB peripheral bus per CPU

- Allocation of peripherals to CPUs is defined and fixed during boot

- Exceptions management with counters

- Restart on errors can be programmed

### Wide range of interfaces

- ADC parallel interface to external ADCs

- Configurable and autonomous

- 2 AWG (Arbitrary Waveform Generator)

- Useful for LDVT or resolvers excitation

- 24 PWM

- 2 SPI

- master or slave

- Up to 6 slaves per SPI

- Autonomous behavior is also possible

- □ I2C

- Master or slave

- 4 UART

- **D** 106 GPIO

- Embeds 8-bit programmable I/F for EEPROM

### Wide range of bus interfaces

- 2xSpaceWire

- Support RMAP Protocol

- CAN

- Integrates redundancy management

- MIL-STD-1553 RT

- MMU dispatching AHB to XCHG\_RAM

### Real-Time Background Tracer (RTBT)

- Non-intrusive

- real-time debugging is available

### Booting via SpW, CAN, RTBT or 8-bit EEPROM (GPIO)

- 4 different boot tentatives can be programmed

- Performs APB peripheral allocation to CPUs and peripheral initialization

- EDAC and scrubbing management

- Programmable address ranges and frequency

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

# SOFTWARE DEVELOPMENT ENVIRONEMENT

# SDE

#### 15 Assembler and Macro Library already available in preliminary version Spacebel (B) as main subcontractor **ESA** End Customer SDE environment MACRO **USER INTERFACE** LIBRARY SABCA CLP prime Contractor **GENERATOR** COMPILER DEBUGGER Spacebel ASSEMBLER CLP SDE Subcontractor CLP

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

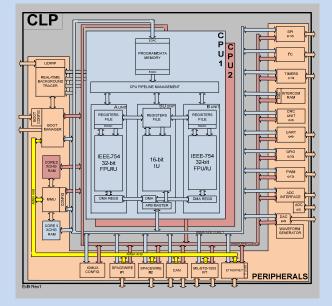

### SOFTWARE DEVELOPMENT ENVIRONEMENT

- Development Environment based on Eclipse

- Automatic code generation from Matlab/Simulink

- Based on QGEN tool (developed by ADACore)

- Pre-defined Macro library provided for some optimized functions

- C compiler based on LLVM

- LLVM supports SIMD and can extract vectorial behavior from linear code.

- Instruction Set Simulator/Debugger

- Initialization Generator

- Real-time background tracer Manager

- Unit Test Manager

### SOFTWARE DEVELOPMENT ENVIRONEMENT

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

### SOFTWARE DEVELOPMENT ENVIRONEMENT

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

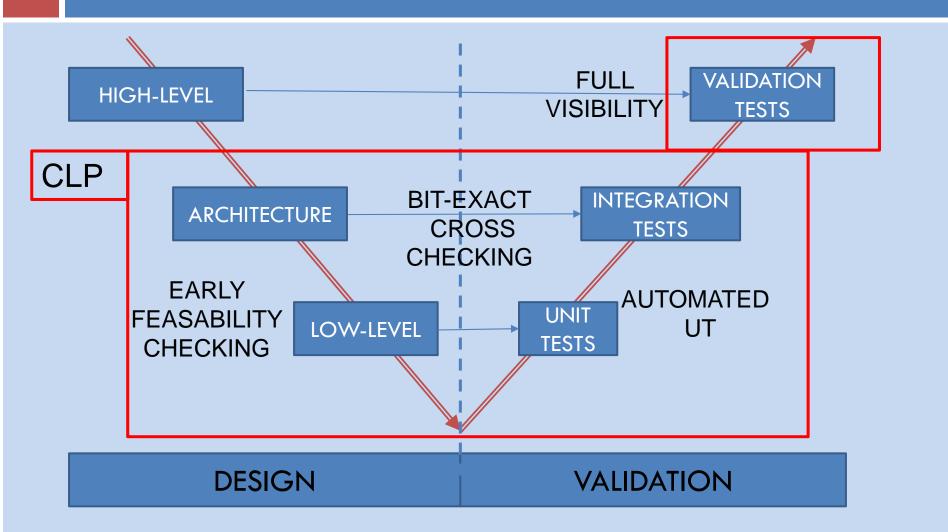

# VALIDATION

# **VALIDATION STRATEGY**

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

## **VALIDATION PLAN**

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

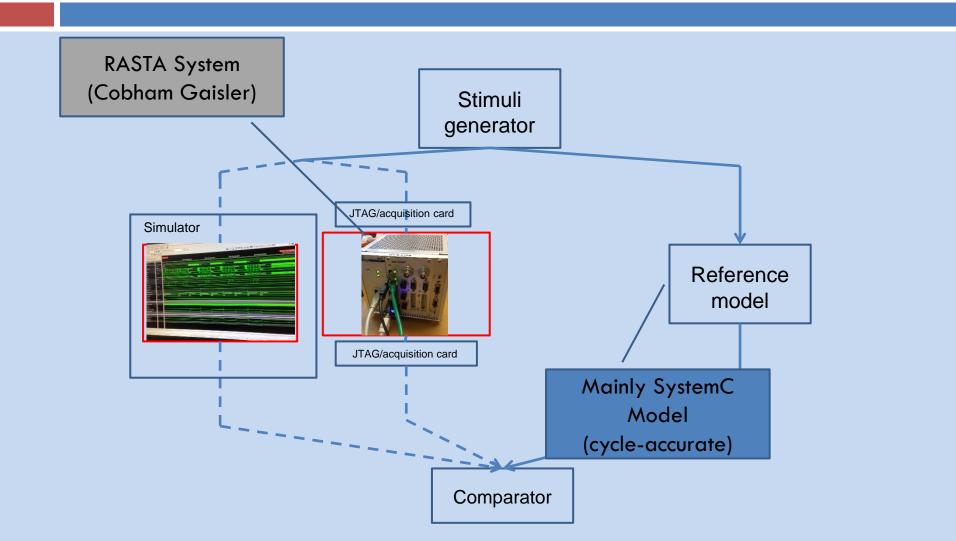

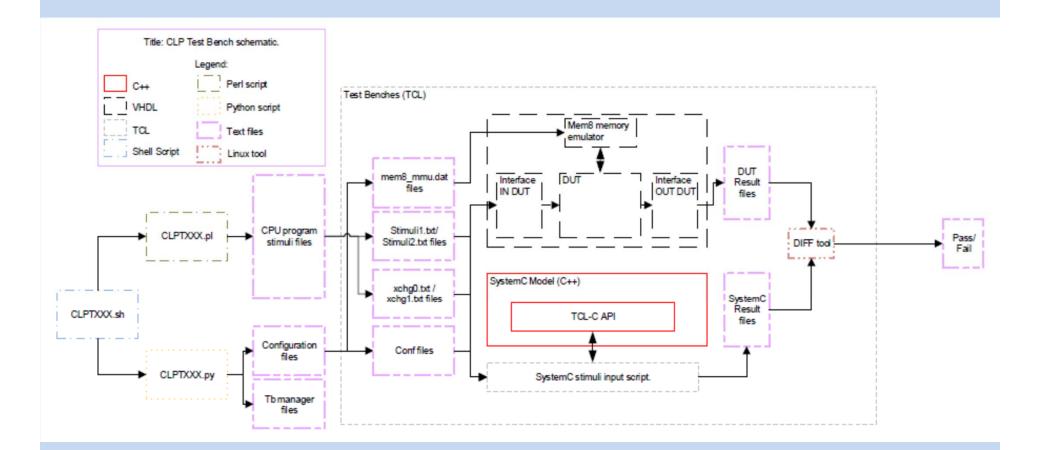

# **VALIDATION ACTIVITIES**

### Processor, models and testbenches complexity is high

- Full traceability between specification and validation plan

- 650+ files, 140 000+ lines of code (w/ comments)

- 700+ automated test campaigns executed around 5 testbenches

- Pseudo-random and directed vectors

### Unified architecture

Test scenarios can be reused (with minimal effort) between simulation (RTL and post-layout) and board testing

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

# **USE CASES**

## **USE CASES**

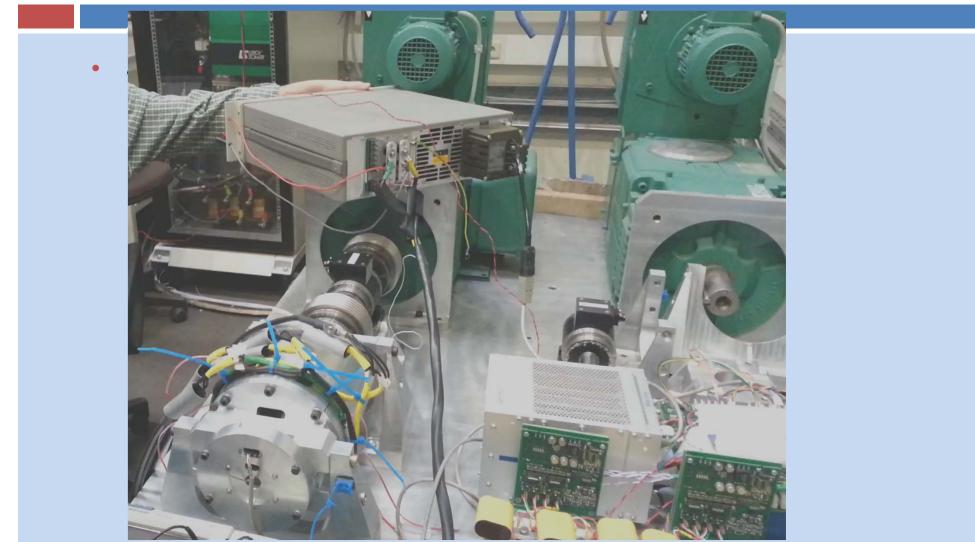

Launchers control of electromechanical actuators (VEGA-C and A6 TVC)

#### Flap control systems (IXV, PRIDE)

IXV based on Vega Z23 upper stage

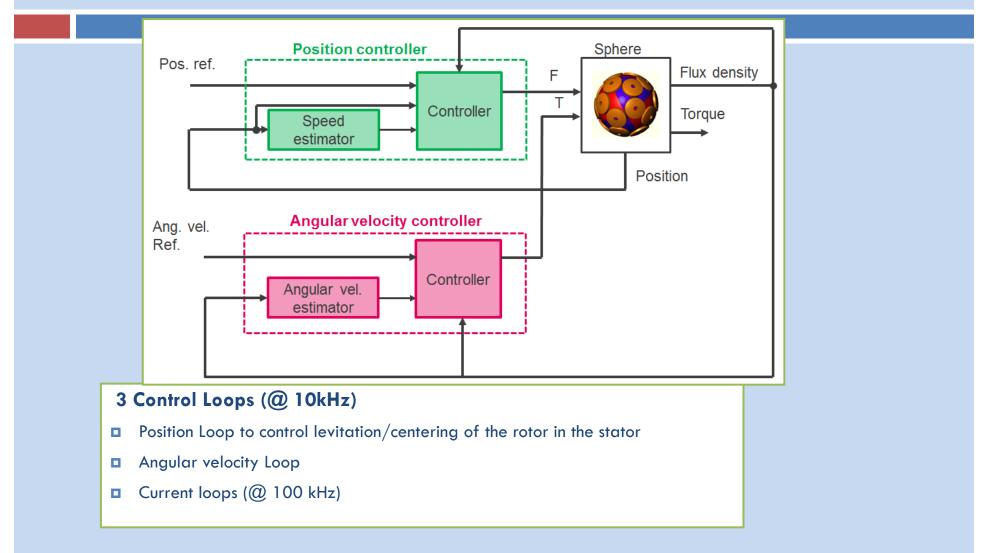

#### Levitated Reaction sphere control (ELSA)

- see next slide

- <u>http://elsa-project.eu/</u>

- Rover distributed motor control

### **Exo-skeleton and robotics applications in general**

## **EXAMPLE OF CLP APPLICATION**

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

# **EXAMPLE OF CLP APPLICATION**

- □ <u>TASK#1</u>: 3 torque setpoints and bus management @ 10Hz

- acquisition from MIL-STD-1553

- TASK#2: 3 position and 7 flux sensors @ 10 kHz

- acquisition and post-processing

- <u>TASK#3</u>: Main Control Loop @ 10 kHz

- 4000 to 5000 Floating-point operations required

- Up to 50 MFLOPS are required

- □ <u>TASK#4</u>: 20 Current Loops @ 100 kHz

- 20 PID with PWM generation

- 20 currents acquistion

# **EXAMPLE OF TAILORED CLP APPLICATION**

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

# **EXAMPLE OF TAILORED CLP APPLICATION**

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

### **EXAMPLE OF CLP APPLICATION**

This document has been issued by Société Anonyme Belge de Constructions Aéronautiques (Belgium)All information contained in this document is exclusive property of SABCA ©SABCA Brussels – All rights reserved

# **SUMMARY**

# **AVAILABLE ITEMS**

#### 31

### IP VHDL code, extensively validated

- can be configured as an IP for tailored versions

- Cobham Gaisler IPs have been used

- Spacewire, CAN and I2C validation still need completion

- SystemC model

- Cycle accurate with respect to VHDL code

- Evaluation board based on RASTA system (Cobham-Gaisler)

- CLP Bit stream is available

- □ Assembler, Tracer and unit test manager

- Automated and extensive testbench manager

- Preliminary CLP datasheet

# **COMING ITEMS**

#### **Q1 2017**

- Waiting for DARE65 availability (DARE180 initially foreseen)

- SDE v1.0 (C-compiler not included yet)

#### **Q3 2017**

- SDE v2.0 (full set of tools, confidence tests)

- **Q1 2018**

- Start of ASIC design (TBC)

#### **Q3 2019**

- ASIC prototype tests and characteristation (TBC)

- **2020**

- Flight Models according to ESCC-9000 (TBC)

- SDE qualified (production release) (TBC)

#### **<u>For more information</u>**

<u>http://clp-space.com/</u>