## **EUROPEAN SPACE TECHNOLOGY** HARMONISATION ROADMAP MEETING

## **Industrial Policy Committee**

**Technology Harmonisation Advisory Group**

MICROELECTRONICS: ASIC AND FPGA

Issue 4 rev. 2Draft

A. Fernandez-Leon, TEC-EDM

- 1. Technology Overview

- 2. Mission Needs and Market Perspectives

- 3. Proposed Development Approach

- a. Focus on deep-submicron (65nm and smaller) microchips

- 4. Closing Remarks

### **Technology Overview**

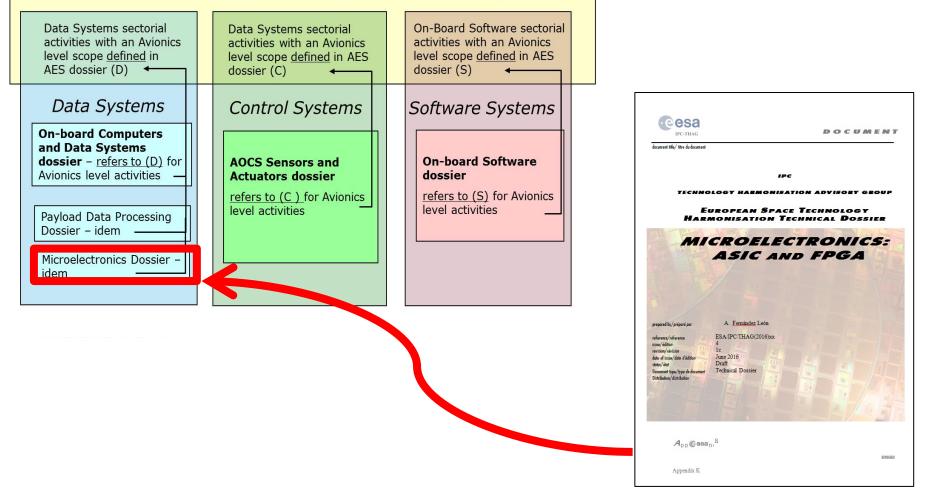

**Avionics Embedded Systems dossier**: roadmap listing Avionics level crosssectorial activities and sectorial activities with a cross-sectorial scope

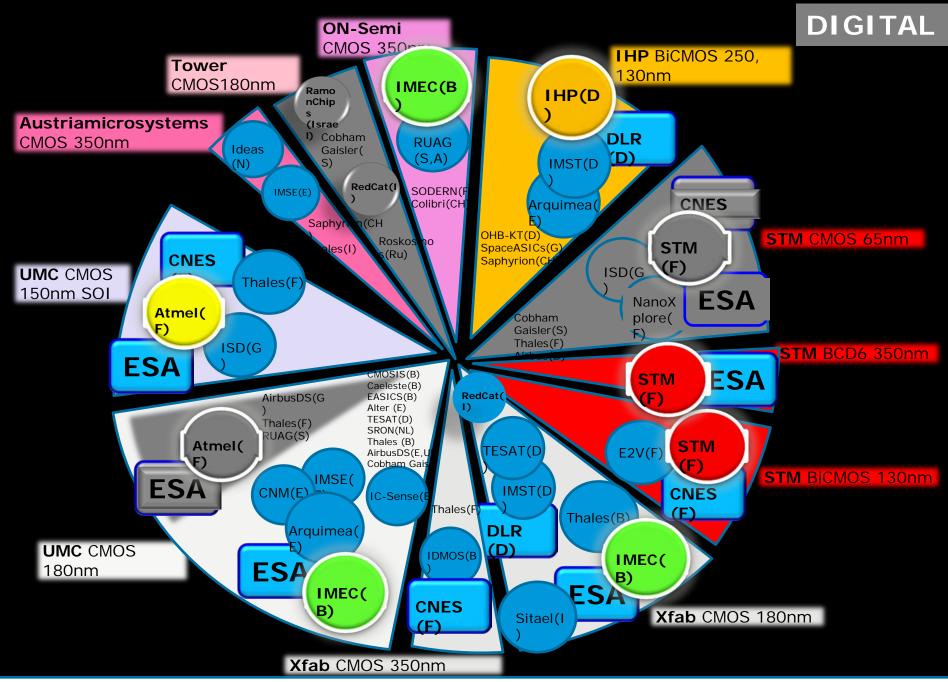

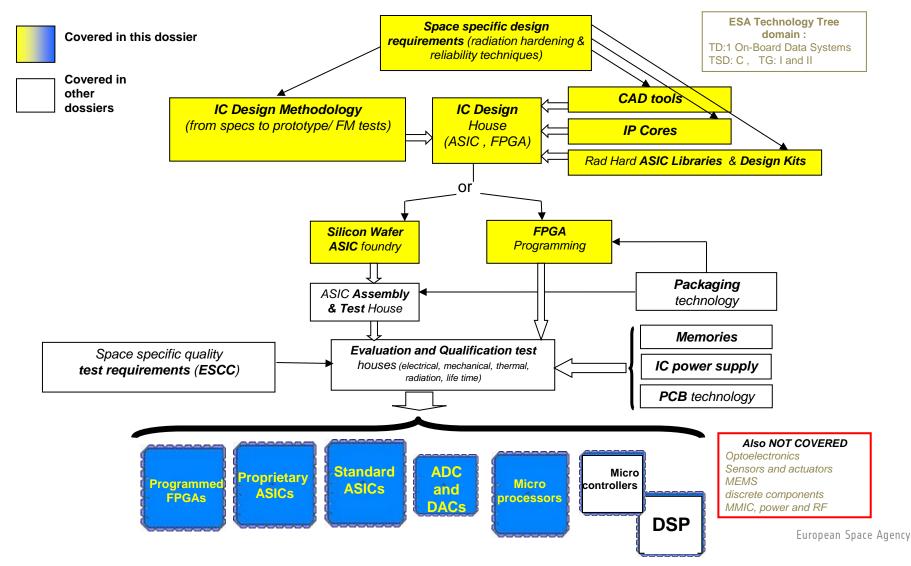

### Technology Overview: Areas covered in "Microelectronics: ASIC & FPGA dossier"

ESA UNCLASSIFIED – For Official Use | ADCSS 2016 | 18-10-20016 | Microelectronics roadmap | A. Fernandez Leon

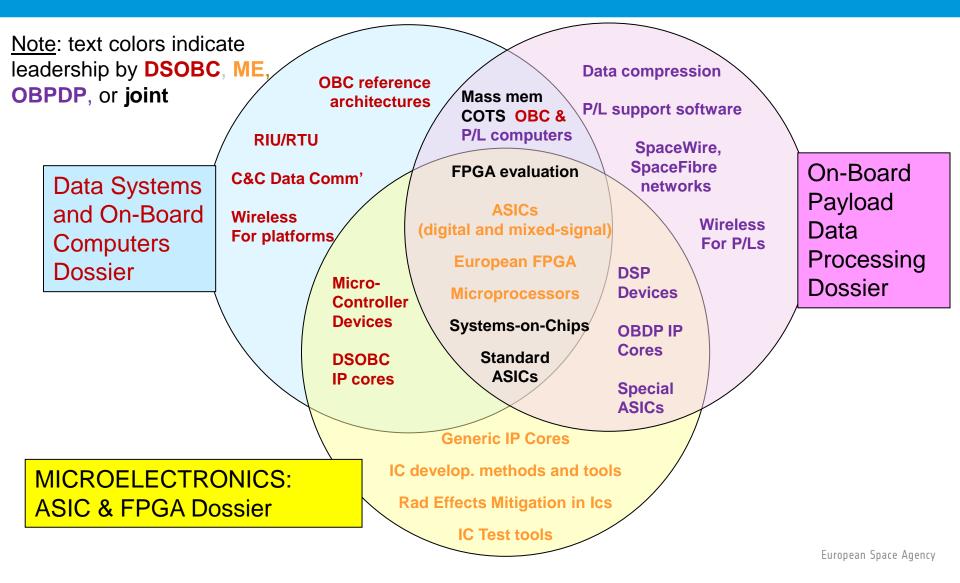

## Technology Overview: Synergies among the three Data Systems Dossiers

## MISSION NEEDS/MARKET PERSPECTIVES European strategic interest

- availability of European space ASIC and FPGA technology in general, at competitive prices

- miniaturisation and speed/power optimization

- make advances in the performances and functional capabilities of our satellites (e.g. DSM ASIC for next generation Telecom payloads)

- maintain and increase competitiveness of European satellite equipment manufactures

- minimize the dependency on export restrictions and overhead (e.g. US ITAR parts)

- trend: manufacturing in Asia, with cheaper labour costs and national incentives for foreign capital investment facilitates a better and more sustainable business model

- European strategic interest that all ASIC/FPGA capabilities (design houses, manufacturing and test) remain secured and sustainable in Europe.

- While in parallel there is a European strategy to work with Asian Fabs

## MISSION NEEDS/MARKET PERSPECTIVES FPGA

- steady increase in the use of FPGAs versus more or less constant use rate of new and existing catalogue ASICs and ASSPs.

- > IP Core-based SOC design is also experimenting an increase

- FPGAs used in space is dominated by US one-time-programmable technologies

- Rad hard reprogrammable FPGAs received a slow uptake by the space community.

- Reasonable parts costs shall be a major requirement in the European FPGA development

- The upcoming family of European BRAVE FPGAs offers potential for a much wider acceptance, as well as the new Microsemi FLASH-based reprogrammable parts.

According to the implementation of the **previous (2011) roadmap** :

- > 33 ESA activities are "funded" or "partially funded" for a budget of about 24M€.

- > 37 additional ESA activities that were not part of the 2011 Roadmap, amounted to ~ 24.5 M€.

#### Total of 70 ESA activities approved since 2011 for a budget of 48.5 M€

So, the yearly reference (total budget of all relevant activities approved since the previous Roadmap divided by the number of years (6 years, as of December 2015):

## Yearly reference budget = 8M€

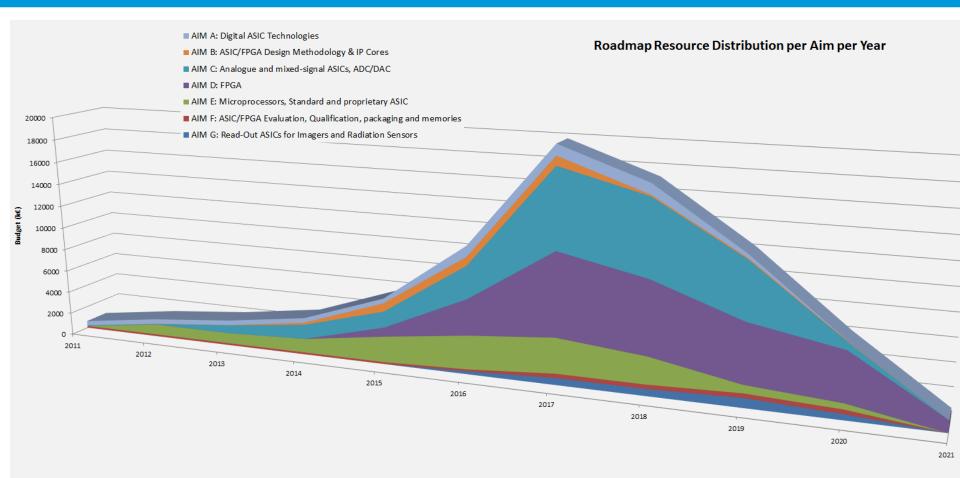

## ROADMAP Aims (1/2)

#### Aim A: Digital ASIC technologies

European deep submicron technologies 65nm and 28nm or beyond, evaluation of radiation effects in these technologies.

#### Aim B: ASIC/FPGA Design methodology and IP Cores

fault injection tools, HW-SW SoC co-design, various digital and A/MS new IP Cores, tools to optimise design of systems combining FPGA and Microprocessors, multi-core multithreading, timing predictability, fast simulation with Virtual Platforms and ESL, etc.

#### Aim C: Analogue and mixed-signal ASICs, ADC/DAC

multiple ADC and DAC ASSP developments and standard standalone devices; A/MS design kits and ASIC platforms like IMEC-DARE, Atmel-ATMX150RHA, or IMST/XFAB

#### Aim D: FPGA

new European reprogrammable BRAVE FPGA family (65nm, 28nm or beyond), tools to optimise radiation behaviour reprogrammable FPGAs

#### Aim E: Microprocessors, Standard and proprietary ASICs

Maintaining, improving, developing, evaluating or qualifying Microprocessors, "Standard ASICs" (or ASSPs) and other proprietary ASICs (with potential for reuse)

## Aim F: ASIC/FPGA Evaluation , Qualification, packaging, memories

#### Aim G: Read-Out ASICs for Imagers and Radiation Sensors

new AIM in the 2016 dossier. activities for maintaining, improving, developing, evaluating or qualifying microelectronic technologies needed for imagers, radiation sensors, namely read-out ASICs.

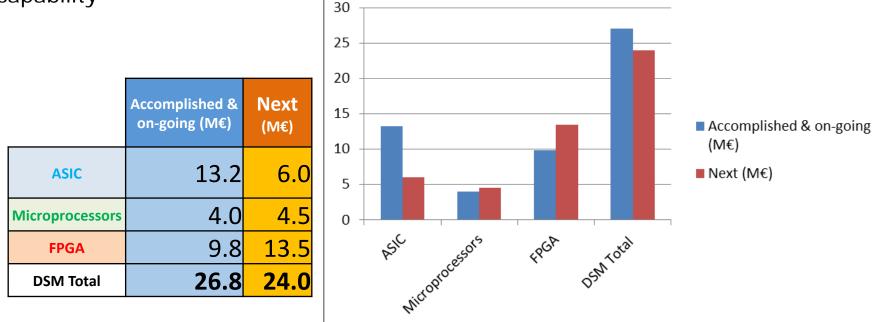

### ROADMAP Proposed development approach: Resource Distribution

European Space Agency

ESA UNCLASSIFIED – For Official Use | ADCSS 2016 | 18-10-20016 | Microelectronics roadmap | A. Fernandez Leon

# Overview of 2016 Roadmap ASIC & FPGA CSA activities

- 1- Standard ASICs & processors (DIGITAL and Mixed-Signal) 21 running activities

- 2 ASIC technology 6 running activities

- 3 IP Cores, FPGA, IC design and test tools & methodology 14 running activities

**46 new activities** being proposed in "Microelectronics: ASIC & FPGA" harmonization dossier 2016 (many in synch with "CTB/ECI5" roadmaps).

There are also many ASIC/FPGA/IP Core/uC/DSP activities in OBPayloadDS and DSOBComputer dossiers

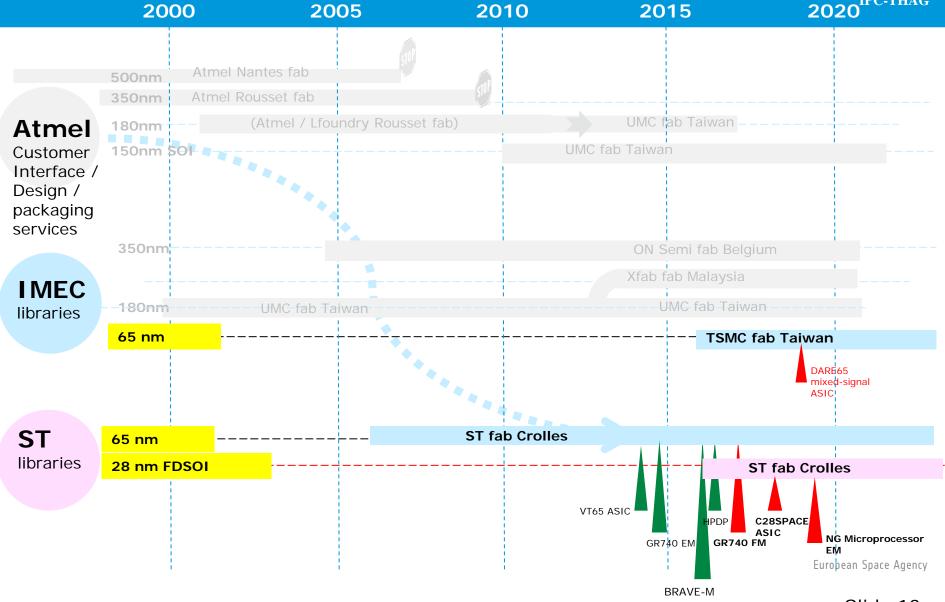

## European DSM processes & libraries for space microchips: 65nm and below

ESA UNCLASSIFIED – For Official Use | ADCSS 2016 | 18-10-20016 | Microelectronics roadmap | A. Fernandez Leon

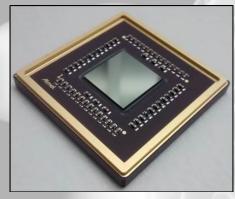

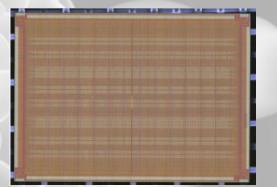

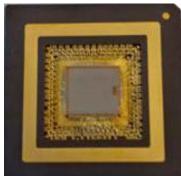

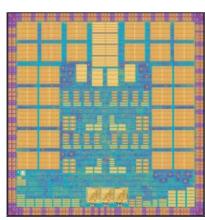

### recent examples of European DSM chips

#### brains processing the DATA inside our satellites

2015

2015

**VT65**" Telecom payload processor 200 mm<sup>2</sup> 1752 pins

TAS/ST/Atmel/E2V/CNES

NGMP/GR740

**General Purpose Microprocessor** 70 mm<sup>2</sup> 625 pins Cobham Gaisler/ST/E2V/ESA

2016

BRAVE FPGA

**General Purpose** Reprogrammable 170 mm<sup>2</sup> 625 pins NanoXplore/ST/ESA/CNES

#### All manufactured with 65nm rad-hard microchip technology provided by STMicroelectronics & partners European Space Agency

ESA UNCLASSIFIED - For Official Use | ADCSS 2016 | 18-10-20016 | Microelectronics roadmap | A. Fernandez Leon

**European DSM processes & libraries for** space microchips: 65nm and below

#### Accomplished

| STMicroelectronics<br>mature design<br>kit/libraries<br>(C65SPACE) | 7M€<br>ESA & CNES<br>8 yrs |

|--------------------------------------------------------------------|----------------------------|

| first users and<br>products (VT65,<br>NGMP, BRAVE-M)               |                            |

| On-going                                      |                  |

|-----------------------------------------------|------------------|

| Space Flip-Chip<br>packaging                  | 1.8M€            |

| HPDP ASIC                                     | 480K€            |

| DDR IP                                        | 900K€            |

| IMEC development<br>of mixed-signal<br>DARE65 | 3M€<br>2016-2019 |

|                                               |                  |

**ASIC**S

| Next                                                                   | Support<br>Needed ! |

|------------------------------------------------------------------------|---------------------|

| <b>C65SPACE</b> ESCC*<br>Qualification (wire<br>bonding and flip chip) | 1.5M€               |

| Development and<br>evaluation of<br><b>C28SPACE</b><br>(28nm)          | 1M€                 |

| DARE65<br>Analogue IPs<br>(GSTP+TRP)                                   | 3.5M€               |

\* European Space Components Coordination, https://spacecomponents.org/

& CNES

European DSM processes & libraries for space microchips: 65nm and below

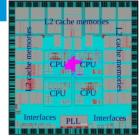

L2 cache memories

**System**

**IPC-THAG**

| Accomplished                                                 |        | Micro-<br>processors                                        | CPU CPU<br>CPU CPU<br>Dieface PLL Interfaces                               |

|--------------------------------------------------------------|--------|-------------------------------------------------------------|----------------------------------------------------------------------------|

| <b>GR740</b> Engineering<br>Model (4xLEON4 +<br>peripherals) | 2.6M€  | On-going                                                    |                                                                            |

| component<br>manufactured end<br>2015 with ST                | 11 yrs | Finish GR740<br>validation                                  | Next Support<br>Needed !                                                   |

| C65SPACE<br>Software                                         | 1.4M€  | HW optimisation for performance,                            | GR740 FlightModel & ESCC2M€Qualification                                   |

| benchmarks, multi-<br>thread, time-<br>predictability        | 5 yrs  | time-predictability<br>SW environment<br>tools optimisation | High Performance<br>Space<br>Microprocessor: 1.5M€                         |

|                                                              |        | for performance,<br>time-predictability,<br>debugging       | GR740-HP (Eng.<br>Model)                                                   |

|                                                              |        | aadaggiiig                                                  | Qualification of<br>new/complementa<br>ry GR740 SW1M€<br>tools & Operating |

European DSM processes & libraries for space microchips: 65nm and below

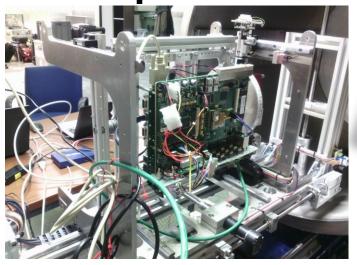

## GR740 4xLEON4 Micro-processor

#### GR740 SEE tests June 2016

1614 COBHAN GR740-XX Cobham Gaisler AB

#### GR740 Evaluation boards

ESA UNCLASSIFIED – For Official Use | ADCSS 2016 | 18-10-20016 | Microelectronics roadmap | A. Fernandez Leon

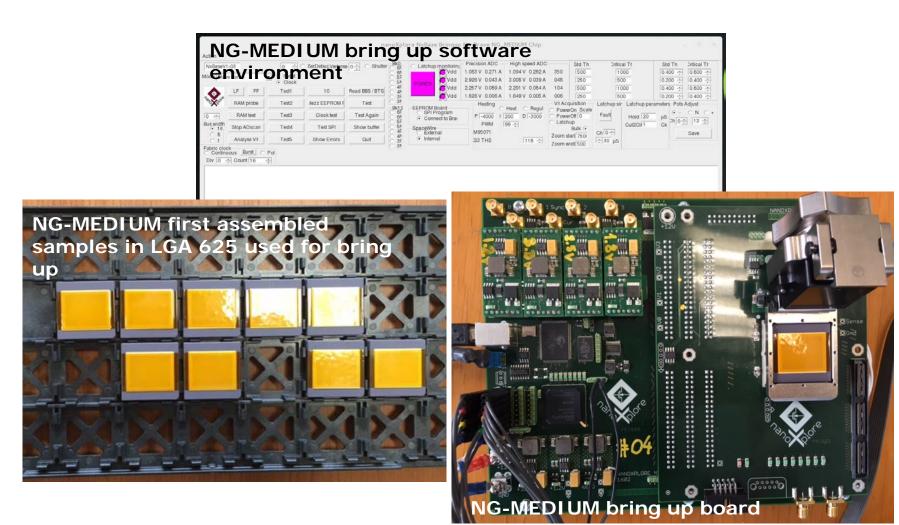

### **BRAVE NG-MEDIUM Bring Up**

European Space Agency

## **CONCLUSIONS on European space DSM**

- Deep Submicron (65nm and smaller) ASICs, FPGAs and Microprocessors enable higher performance, miniaturization and less power consumption than older microchip technologies

- First microchips have been manufactured: VT65, GR740, BRAVE-M...

- Urgent new investments needed to finish and qualify 1st products and tools, to develop next generations and more mixed-signal DSM ASIC capability

## **Closing remarks on ASIC & FPGA Roadmaps**

- ASICs and FPGAs are key for all missions

- ME dossier has been updated to reflect inputs from industry and delegations, and better coordination between dossiers

- New roadmap has been compiled and consolidated

- More FPGAs and fewer ASICs, as gate capacity and performance increases and because differences in price (NREs and per part) and development time

- European space ASICs vendors with European rad-hard libraries and IP, some manufacturing in Asia (fabless), but

- Many silicon fabs still in Europe, strong in niche, specialized, mixed-signal

- huge dependence on US (ITAR) space FPGAs (all manufactured in Asia).

- Many European ASIC/FPGA design groups and test houses with space knowhow

- European supply chain fragmented and international ownership makes space quality control difficult

- Technology changes call for updates and tailoring of old quality standards

- Space complex general use ICs difficult/expensive to develop and maintain, market sustainable only by parallel commercial (non-space) high volumes, and institutional (Agencies and EC) support

European Space Agency

#### -> important to coordinate and harmonise efforts and priorities

ESA UNCLASSIFIED – For Official Use | ADCSS 2016 | 18-10-20016 | Microelectronics roadmap | A. Fernandez Leon

# More info

## **ESA** Microelectronics section activity:

http://www.esa.int/TEC/Microelectronics

# Technology harmonisation dossiers will be available here:

http://www.esa.int/Our\_Activities/Space\_Engineering\_Technology/About\_st rategy\_and\_harmonisation

https://tec-polaris.esa.int/pls/adm/webloginext.login

### **BACK UP SLIDES**

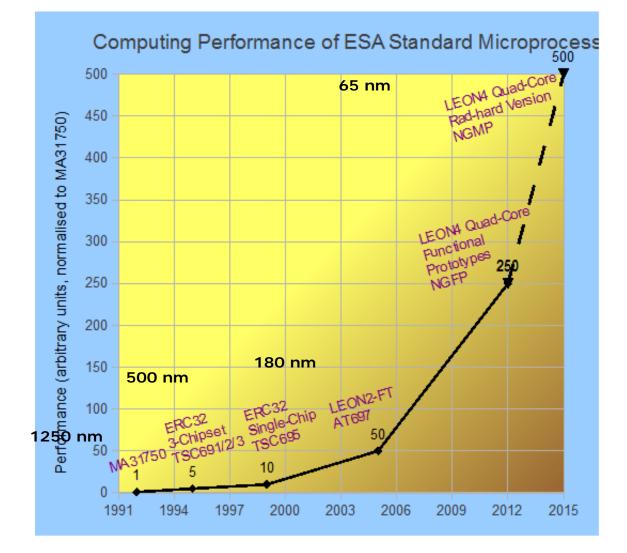

## Microprocessors: better performance thanks to DSM technology

European Space Agency

ESA UNCLASSIFIED – For Official Use | ADCSS 2016 | 18-10-20016 | Microelectronics roadmap | A. Fernandez Leon

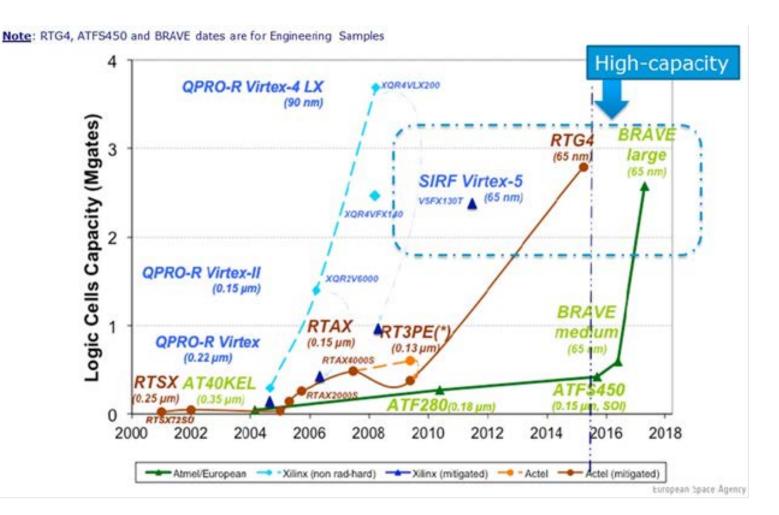

## **FPGAs:** better performance and functional capacity thanks to DSM technology

European Space Agency

#### Space ASIC Technology Observatory (draft 2 – Jan 13<sup>th</sup> 2016)