Modèle = 83230347-DOC-TAS-EN-004

2017 Thales Alenia Space

# TAS Space Processors view TABLE OF CONTENT

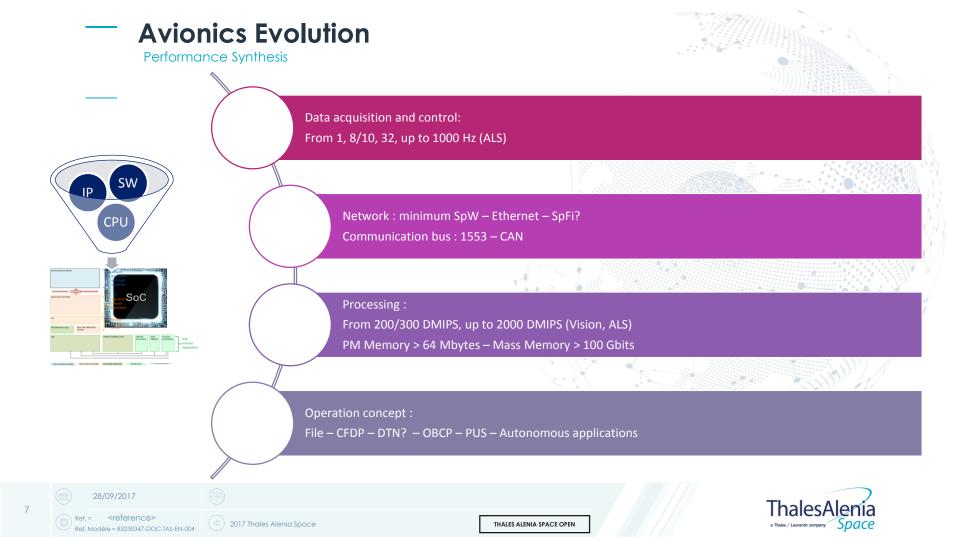

- 1. Integrated AVIONICS

- 2. New functional Needs

- 3. Operation Concept Evolution

- 4. Performance Overview

- 5. Avionics Development Needs

## MISSIONS GENERAL OVERVIEW

Constellation:

Low rec cost

Science – exploration : Rendez vous – capture landing

Future Applications: navigation

**Integrated Avionics**

STR data processing

**GNSS data processing**

**CMG** control

**Additional** functions

## **Operation Concept Evolution**

**GENERAL OVERVIEW**

## **OBC** to integrate

- File based operations

- **S**CFDP protocol

- More OBCPs (FDIR/autonomy feature)

- PUSLIB to be converted/upgraded in PUS C std

## **Operation Concept Evolution**

**GENERAL OVERVIEW**

Evolution of FDIR strategy induced by:

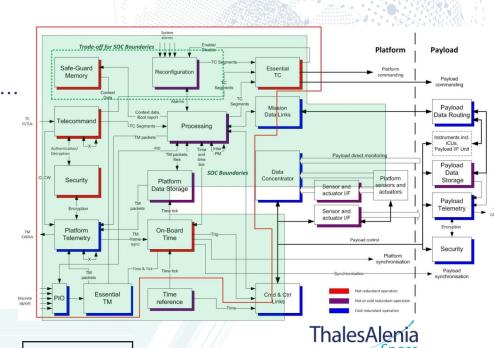

- Processing in one SOC

- Most PF applications centralised (ASW, STR, GNSS, ...

- Reconfiguration Module location

- SGM location

- Xstrap scheme simplified

- → Could lead to "half platform" recovery.

## **AVIONICS** development needs

GENERAL OVERVIEW

#### New space processor in Avionics require:

- Debugging capabilities

- SDSU Profiling

- Development models

- Development board to support SW migration

- Eventually Functional Model

- Simulated core

- To be inserted in numerical Avionics core simulator

- \*\* HDSW/Boot Sw development

- \* Hypervisor/OS

- Supporting TSP

- Supporting Multicore

- SVDE and SW migration

#### Significant Non recurring Activities associated to new space processor

## **AVIONICS** development needs

Common BB

What could/should be shared by Space stakeholders with the objective of harmonisation

Development board to support SW migration preparation (bread boarding activities)

To be inserted in numerical Avionics core simulator

#### \* Hypervisor/OS

Qualified on the targeted Space processors

#### **Space Agencies roles to support common BB**