**European Space Agency**

# Space Processors: Programs Views (Earth Observation)

Avionics, Data, Control and Software Systems (ADCSS)

Presented by J. Rosello (EOP- $\Phi$ MT , EO Future Missions Div.) (19-Oct-2017)

1+1

ESA UNCLASSIFIED - For Official Use

±=\_\_\_

# Table of Content

Locations of microprocessors: Platform + Payload

Overview of EO missions & which microprocessors in use

Challenges for the future

# Definition of processor

On-going developments and emerging topics in the field of space processors.

The term processor comprises:

- Various architectures and performance classes:

- single and multi-core,

- symmetric and asymmetric processors,

- microcontrollers and DSP's.

- Hardware + Software (development tools, compilers, operating systems, hypervisors etc.)

- Developments dedicated to space or (screened) COTS

- Developments of different maturity (from low TRL R&D up to In Orbit Demo.)

- → Large investments and consortia to reach adequate and complete (HW and SW) "qualified" solutions.

Emerging applications: higher performances and/or integration of new functionalities.

| ESA UNCLASSIFIED - For Official Use | ESA   19-Oct-2017   Slide 3 |

|-------------------------------------|-----------------------------|

|                                     | European Space Agency       |

# Location of Microprocessors

### **Platforms:**

- OBC or SMU: (On-Board Computers or Service Management Unit)

- **MMFU** (Mass Memory and Formatting Unit)

- GNSS Receivers

- Star Trackers

- **OCP** (Optical Communication Payload)

- Others (mini-IMU) not covered in this presentation (lack of information)

#### Payload:

- ICU or CES or DPU : (Instrument Control Unit or Central Electronic System or Digital Processing Unit)

- ➔ not always with a microprocessor (SW required)

- $\rightarrow$  different for each mission

| ESA UNCLASSIFIED - For Official Use | ESA   19-Oct-2017   Slide 4 |

|-------------------------------------|-----------------------------|

|                                     | European Space Agency       |

# **ESA Earth Observation Missions**

### **OBCs - SMUs**

### 31750:

SMOS

### ERC-32:

- Goce, EarthCare, ADM, Cryosat-2, Swarm, Sent-1a/b, Sent-2, Sent-3, Sent-6

- In Sentinel-2: CPU peak = 65% (normally much lower); 8 Gbit SDRAM

### Leon-2FT (AT697F, COLE):

• MTG-I, MTG-S,

### Leon-3 (GR712RC, SCOC3, EPICA-Next):

- MetOp-SG, SeoSat, Sent-1c/d, Sent-5p

- MetOp-SG: 75% worst case CPU usage with 32 MHz (normally much lower)

#### If more processing power available:

- Increase functionality: e.g. FDIR

- Serve as processor for other functions : star trackers, GNSS, ... (multi-core can be interesting)

| ESA UNCLASSIFIED - For Official Use | ESA   19-Oct-2017   Slide 6 |

|-------------------------------------|-----------------------------|

|                                     | European Space Agency       |

# MMFU (Mass Memory and Formatting Unit)

#### ERC-32:

- Sent-1, Sent-2, Sent-3, Sent-6

- In Sentinel-2: CPU peak = 6%  $\rightarrow$  with high CPU power, compression could be envisaged

### Leon-2FT (AT697F, COLE):

• Biomass, EarthCare

### LEON-3 (GR712RC, SCOC3, EPICA-Next):

• MetOp-SG, Sent-5p

#### **FPGAs + OBC**

• Goce, Swarm, ADM,

ESA UNCLASSIFIED - For Official Use ESA | 19-Oct-2017 | Slide 7

# **GNSS** Receivers for Navigation and POD

#### **Various microprocessors**

• ADM, Seosat, Sent-5p (Mosaic SW Rx with DSP-20120)

#### AGGA-2 + LEON or DSP-21020:

- TAS-I (GOCE 21020), RUAG-A: (EarthCare, Swarm, Sentinels 1a/b, S2a/b, S3a/b with Leon2-FT)

- non-ESA: Radarsat-2, Cosmo-Skymed Note: GNSS-Radio Occ. Instrum. with AGGA-2: MetOp-a/b/c, Oceansat2, Megatropiques, SAC-C/D

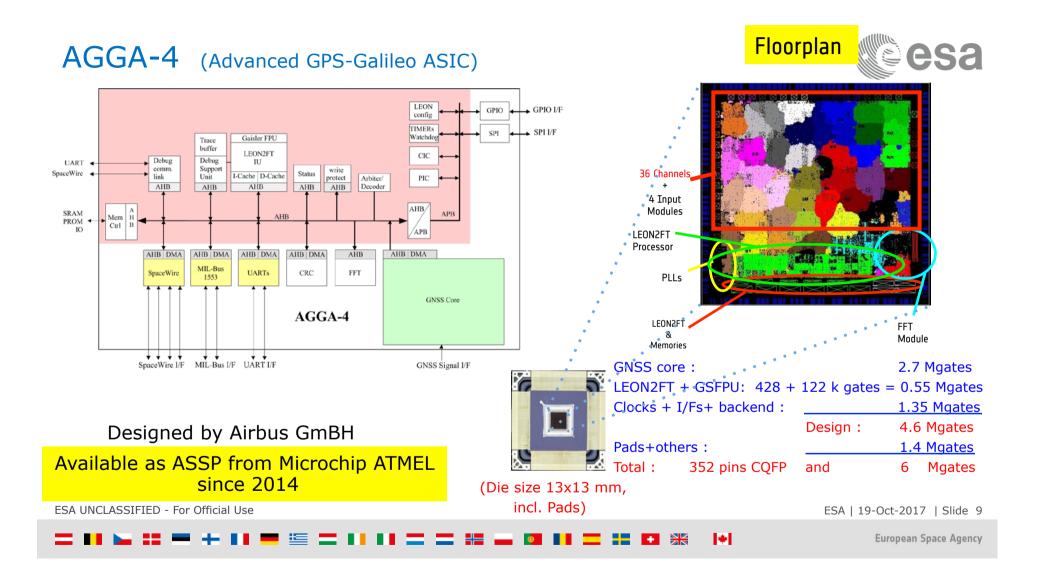

#### AGGA-4 (with Leon-2FT IP core on-chip @ 87 MHz) Note: PODRIX Rx board includes both AGGA-4 and AGGA-2.

- MetOp-SG, S1c/d, S2c/d, S3c/d, S6, Biomass → CPU usage ~ 70%

- Non EO: Proba-3, Neosat

- non-ESA missions: CSO, SARah, Korean Comp.Adv Sat.500, prototyping for Vega-C

#### AGGA-5

- Feasibility study "under negotiation".

- Not decided which microprocessor, but very likely more powerful than for AGGA-4 → more flexibility, cope with multi-GNSS constellation

| ESA UNCLASSIFIED - For Official Use | ESA   19-Oct-2017   Slide 8 |

|-------------------------------------|-----------------------------|

|                                     | European Space Agency       |

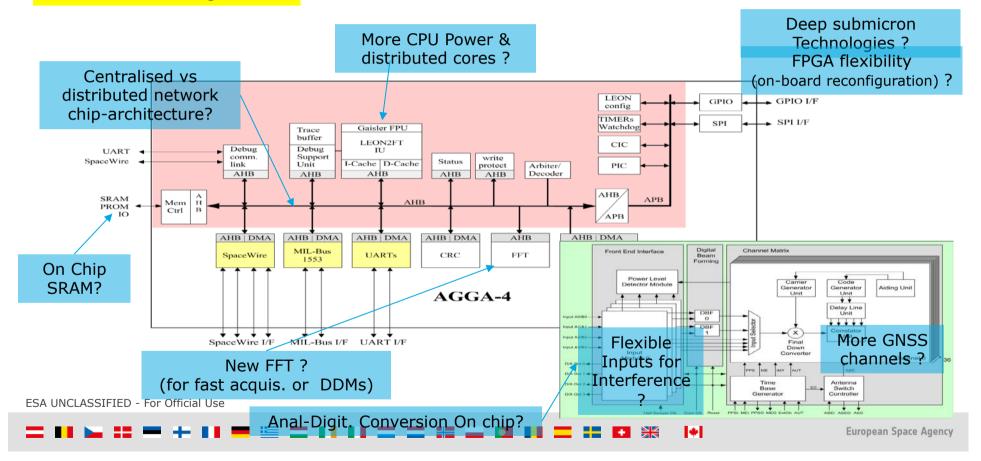

# AGGA-5 feasibility study (EOP funded): Trade-offs

### Status: Under Negotiation

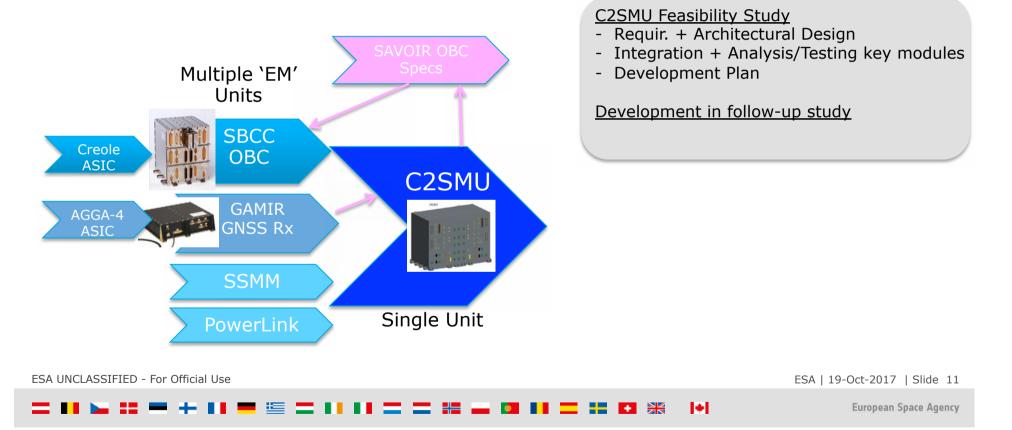

# Study Definition of C2SMU

Complex & Complete SMU and Critical BreadBoarding :

- integrating OBC + GNSS + SSMM + specs for S-PowerlLink

# Star Trackers

• Sent-1, MTG (no OS, interrupt driven)

#### **LEON2FT** (with Sodern)

• Sent-3, Sent-5p, Seosat,

#### **LEON2-FT** (with Jena)

• EarthCare, Sent-2, Sent-6

#### **COTS microprocessor**

- ADM, Swarm, Cryosat-2. (TERMA or DTU)

- SMOS (with SED16 from Sodern)

Highest CPU usage during acquisition (not during tracking). Reasonable usage (even during solar flare)

If more CPU becomes available  $\rightarrow$  robustness, higher performance

| ESA UNCLASSIFIED - For Official Use | ESA   19-Oct-2017   Slide 12 |

|-------------------------------------|------------------------------|

|                                     | European Space Agency        |

# OCP (Optical Communication Payload)

• Only in Sent.1 and Sent.2: PowerPC 750

# **Earth Explorers : Instruments**

| Missi  | on Launch   | Main<br>Instrument(s)                                                                        | ICU – CES - DPU                                     |

|--------|-------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------|

| GOCE   | 2009        | Graviometer<br>Adv. Stellar Compass                                                          | DSP-2010<br>Intel 80486                             |

| ADM-Ae | olus 2018   | Doppler Wind Lidar                                                                           | No microprocessor<br>(only FPGAs)                   |

| Earth  | Care 2019   | Atmospheric Lidar<br>Cloud profiling radar<br>Multi-spectral imager<br>Broad-band radiometer | LEON2-FT<br>Japanese µproc.<br>LEON2-FT<br>LEON2-FT |

| Bioma  | <b>2021</b> | P-Band SAR                                                                                   | Leon2-FT                                            |

ESA UNCLASSIFIED - For Official Use ESA | 19-Oct-2017 | Slide 14

# **Copernicus : actual sentinels and OBCs**

ICU – CES - DPU Sentinel Launch Instrument Sentinel-1 A Sentinel-1 B 3 April 14 25 April 16 C-Band SAR ERC-32 (also C + D)(Plan) Sentinel-2 A 22 June 15 7 March 17 Sentinel-2 B Multispectral None (FPGAs) (also C + D)(Plan) C/Ku Radar Altimeter DSP21020(A/B)-LEON2(C/D) Sentinel-3 A Sentinel-3 B 16 Feb 16 23.8/36.5 GHz radiometer None (FPGAs) 1 14 Plan 2018 OLCI spectrometer LEON2-FT (also C + D)(Plan) VIS-SWIR-TIR radiometer ERC-32 UVN-VIS-NIR Spectromet. LEON-3FT plan 2020 Sentinel-4 A Sentinel-4 B plan 2030 (in MTG-S) UVNS Spectrometer Sentinel-5 A plan 2022 plan 2028 LEON2-FT Infrared Sounder Sentinel-5 B (in MetOp-SG) Multi-view/pol Imager **TROPOMI** (passive LEON2-FT Sentinel-5 P Oct 2017 imaging spectrometer) ESA UNCLASSIF Sentinel-6 A plan 2021 C/Ku Radar Altimeter LEON2-FT plan 2025 Sentinel-6 B

ESA | 19-Oct-2017 | Slide 15

European Space Agency

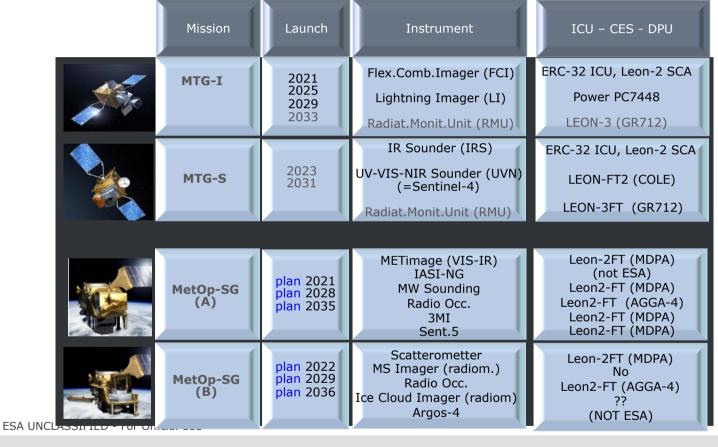

# **Meteorological : Instruments**

ESA | 19-Oct-2017 | Slide 16

European Space Agency

# Increasing functionality SoC

LEON-based Core computer architectures & System on a Chip (SoC), incl. microprocessor+I/Fs:

- ADS: MDPA with LEON-2FT & SCOC3 with LEON-3

- RUAG: CREOLE and COLE with LEON-2FT

- TAS: EPICA-Next with LEON3-FT

and also coming up

- CG: NGMP with multi-core LEON-4 and SpW router

- ARM IP-cores being embedded in new FPGA/ASIC devices (in multiple versions, Mo+, M7, R5, R9, ... )

- → Big legacy so far of single-core LEON family for platform applications

- → LEON also dominates in payloads (ICU), but other options found

#### Multi-core: Will increase processing power, and possibly cover well future growth.

- Common in on-ground apps., but yet in space

- **EOP needs one full (HW-SW) set solution,** possibly starting with payload applications (and combined with FPGA/ASICs). (Compilers, OS, etc.)

#### LEON vs ARM (both in the ESA Harmonisation process): Two key questions / challenges :

- Does one of them get substantial better performance / reliability ?

- Does anybody have the budget to fully develop both ?

- → Let's wait for the following presentations !!

ESA UNCLASSIFIED - For Official Use

ESA | 19-Oct-2017 | Slide 17

The set of th

European Space Agency

# Recap trends if more powerful processors

#### **Platforms:**

- **OBC** or **SMU**: larger functionality & robustness (FDIR, ... ), possibly more integration of functions (SoC)

- **MMFU** : very often same as OBC. CPU Room for more (e.g. compression)

- **GNSS Receivers** : getting integrated in OBC Units and SAVOIR OBC specs

- Star Trackers : if more CPU, higher robustness / performance

- **OCP** : (Optical Communication Payload) currently using PowerPC in S1/S2

#### **Payload:**

- ICU or CES or DPU : (Instrument Control Unit or Central Electronic System or Digital Processing Unit)

- most ESA missions have a microprocessor (SW required). ICUs might be shared between instruments

- More processing power, combined with OB reconfigurable FPGAs can be very attractive

- a bit more of flexibility (in terms of quality) than for Platform Critical functions.

| ESA UNCLASSIFIED - For Official Use | ESA   19-Oct-2017   Slide 18 |

|-------------------------------------|------------------------------|

|                                     | European Space Agency        |

# Conclusion

Overview of EO missions & which microprocessors in use (platform & payload)

- Clearly dominated by LEON family and SoC incorporating more functionality (I/Fs)

- Availability of IP cores is very important for SoC

#### Trends

- More processing power will be available (with multi-core), but also complexity (OS, Compiler) increases

- for OBC : could allow processing functions today done by other microprocessors

- for MMFU : could allow compression or other functions

- for payloads : very interesting, specially if combined with reconfigurable FPGAs/ASICs

- LEON vs ARM ? (technical and also resources issues)

| ESA UNCLASSIFIED - For Official Use | ESA   19-Oct-2017   Slide 19 |

|-------------------------------------|------------------------------|

|                                     | European Space Agency        |