# JUICE NAND FLASHs Total dose radiation tolerance

### ESA-CNES Radiation Final Presentation Days on Space Environments and Radiation Effects on EEE components

ITT AO/1-7740/13/NL/HB - Radiation testing of memories for the JUICE Mission

Main objective: Assess commercial state-of-the art memories radiation tolerance for JUICE mission.

Presentation focused on Nand Flash total dose radiations tolerance

## Outline

Parts selection

**Reverse Construction Analysis**

Test plan

□ Test tooling description

Results

# **NAND FLASH parts selection**

March 2017

# Parts Selection and criteria

#### Key drivers for memory selection:

- Mission lifetime is more than 11 years in space (7.6 years cruise and 3.5 years in the Jovian system).

- Without massive shielding mass, total ionizing dose required 200 kRad(Si).

- Minimum total dose tolerance should be 50 kRad(Si) with sufficient shielding mass.

- Storage capacity as a minimum 60 Gb and up to 500 Gb

- Download data rate < 100 Mbps</p>

#### Parts selection has been performed according to the following criteria :

- State of the art technology (end of 2015, beginning of 2016).

- Non obsolescence of the memory and new devices that haven't been already tested against radiations.

- Size and architecture.

- SLC (Single Level Cell) only for radiation tolerance purpose.

- Package

|                         | Hynix                                     | Toshiba                                   | Macronix                         | Spansion                         | Winbond                                    |

|-------------------------|-------------------------------------------|-------------------------------------------|----------------------------------|----------------------------------|--------------------------------------------|

| Part type               | H27U4G8F2D                                | TC58NVG2S0HTAI0                           | MX30LF4G18AC                     | S34ML04G200TFI00                 | W29N01GVSIAA                               |

| Туре                    | SLC Nand Flash<br>Memory                  | SLC Nand Flash<br>Memory                  | SLC Nand Flash<br>Memory         | SLC Nand Flash<br>Memory         | SLC Nand Flash<br>Memory                   |

| Capacity / Organization | 4 GB / 512M x 8BIT<br>1 bit ECC/528 bytes | 4 GB / 512M x 8BIT<br>8 bit ECC/512 bytes | 4 GB / 512M x 8 BIT<br>4 bit ECC | 4 GB / 512M x 8 BIT<br>4 bit ECC | 1 GB / 128M x 8 BIT<br>1 bit ECC/528 bytes |

| Date code               | 1503                                      | 1509                                      | 1444                             | 1442                             | 1437                                       |

| Package                 | TSOP48 (12x20mm)                          | TSOP48 (12x20mm)                          | TSOP48 (12x20mm)                 | TSOP48 (12x20mm)                 | TSOP48 (12x20mm)                           |

#### Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

March 2017

# Reverse Construction Analysis

### NAND FLASHs Construction Analysis summary

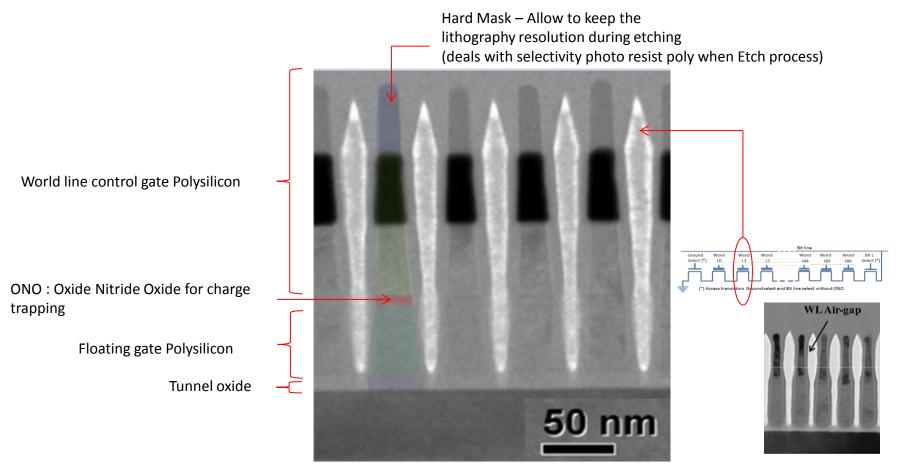

Main challenge for this type of technology is the process capability with the die manufacturing lithography and etching tools. Repeatability of cell spacing Air Gap and minimum Critical Dimension (CD's) patterns definition are most likely the main yield detractors on these parts.

Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

### **NAND FLASHs**

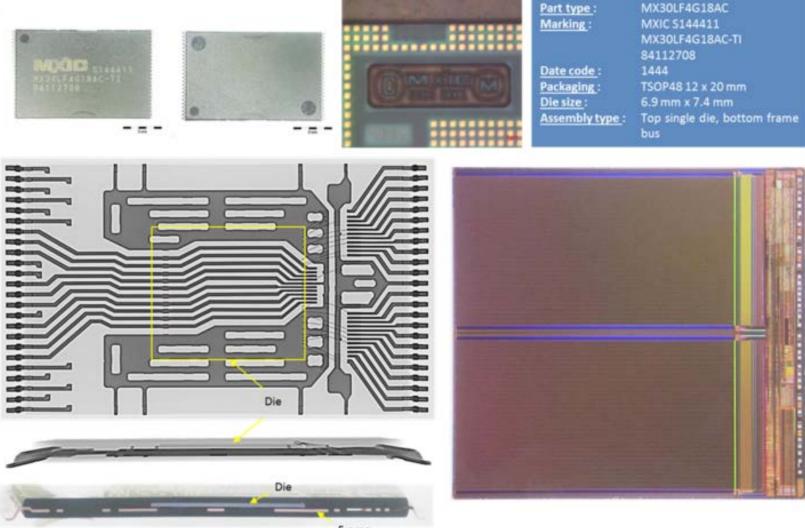

**Construction Analysis (Ex: Macronix Nand Flash)**

Frame

Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

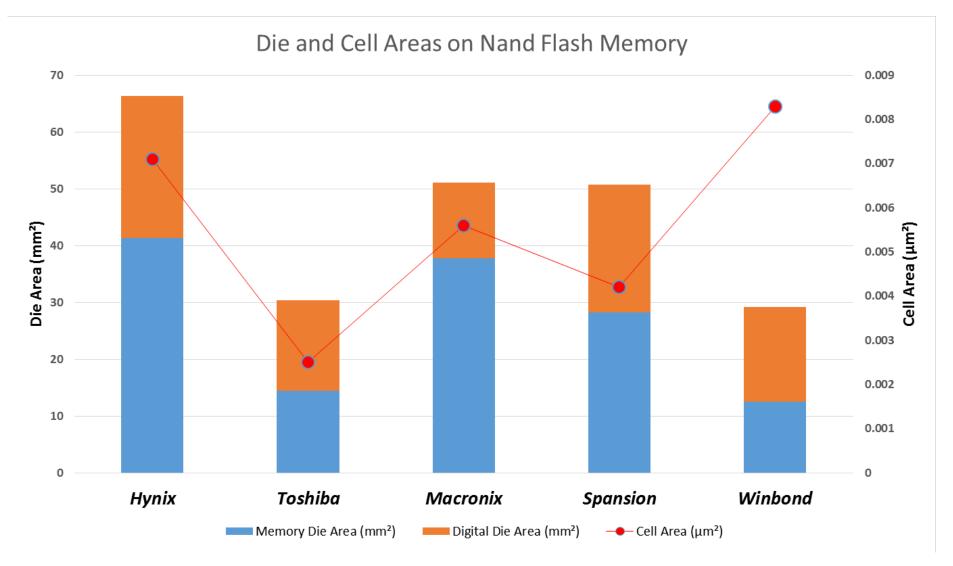

### NAND FLASHs Construction Analysis comparison

|                                                                                    | Hynix                             | Toshiba                            | Macronix                             | Spansion                             | Winbond                              |

|------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| Die size mm (area mm²)                                                             | 7.3 x 9.1 (66.4)                  | 4.9 x 6.2 (30.4)                   | 6.9 x 7.4 (51.1)                     | 6.5 x 7.8 (50.7)                     | 5.3 x 5.5 (29.2)                     |

| Assembly type                                                                      | Top single die + Top<br>frame bus | Flip single die + Top<br>frame bus | Top single die +<br>bottom frame bus | Top single die +<br>bottom frame bus | Top single die +<br>bottom frame bus |

| Serial word lines                                                                  | 34                                | <b>7 – 1</b><br>66                 | 34                                   | 34                                   | 32                                   |

| Memory/Digital area (%)                                                            | 62% / 38%                         | 47% / 53%                          | 74% / 26%                            | 56% / 44%                            | 43% / 57%                            |

| Memory cell area (µm²)                                                             | 0.0071                            | 0.0025                             | 0.0056                               | 0.0042                               | 0.0083                               |

| Minimum pitch (nm)                                                                 | 83                                | 48                                 | 65                                   | 64                                   | 91                                   |

| Critical dimension (nm)                                                            | 41                                | 24                                 | 32                                   | 32                                   | 45                                   |

| Air gap (top cells level)                                                          | Yes                               | No                                 | Partial                              | Yes                                  | No                                   |

| Cells (bit line axis)                                                              | BAAAA                             |                                    | 876 676 8                            | 66667                                | AAA                                  |

| Ground Word Word Word Word Word Word Word U La | ord Word Bit L<br>L66 Select (*)  |                                    |                                      |                                      |                                      |

Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

ass transistors. Ground select and Bit line select without ONC

Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

# **Test plan**

$\succ$  For each reference : ➤ 10 devices in HDC (High Duty Cycle) bias ➢ 10 devices in LDC (Low Duty Cycle) bias  $\geq$  10 OFF devices (pins connected to ground) Devices are irradiated up to 200 Krad (Si) with Co60 Power monitoring of DUT bias board  $\geq$  Electric Measurements steps are performed at 20, 30, 50, 100, 150 and 200 Krad (Si) ➢After irradiation, 24h @25°C and 168h @100°C annealing are performed on devices Electric Measurements steps are performed after each annealing

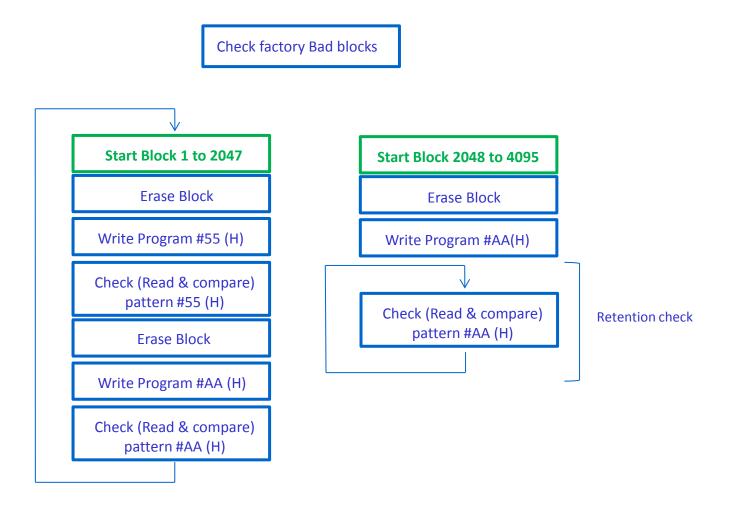

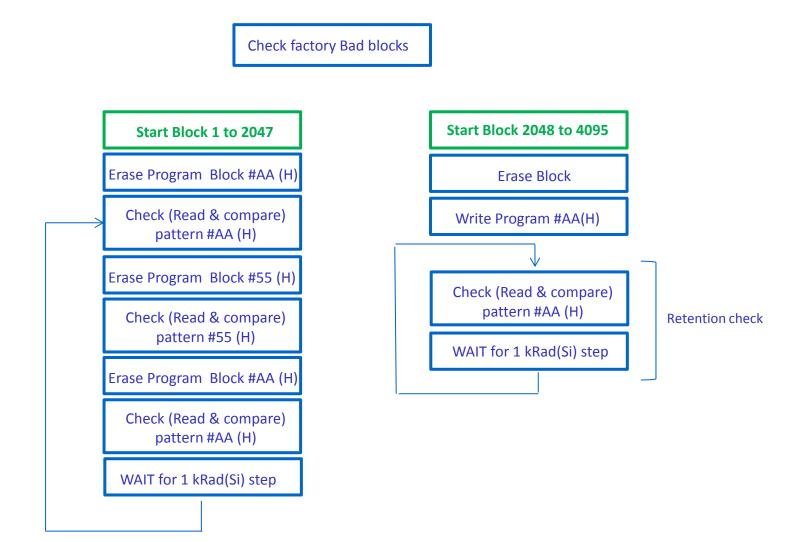

### In situ: FPGA based tester and biasing boards Software description HDC (High Duty Cycle)

March 2017

### In situ: FPGA based tester and biasing boards Software description LDC (Low Duty Cycle)

### **Electrical test system description**

Parameter tests list table (Macronix as an example)

| PARAMETERS                      | SYMBOLS   | TEST CONDITIONS                         | MIN  | мах  | UNITS |  |  |  |  |

|---------------------------------|-----------|-----------------------------------------|------|------|-------|--|--|--|--|

| DC                              |           |                                         |      |      |       |  |  |  |  |

| Continuity Neg                  | Cont_Neg  | Iin=-100uA                              | -1.5 | -0.2 | v     |  |  |  |  |

| Input Leakage Current<br>Low    | ILIL      | Vin=0V , VCC= VCCmax (3.6V)             | -10  | 10   | μА    |  |  |  |  |

| Input Leakage Current<br>High   | ILIH      | Vin= VCC= VCCmax (3.6V)                 | -10  | 10   | μА    |  |  |  |  |

| Output Leakage<br>Current Low   | ILOL      | Vout=0V , Vcc = 3.6V DQ are disabled    | -10  | 10   | μА    |  |  |  |  |

| Output Leakage<br>Current High  | ILOH      | Vout=VCCmax, Vcc = 3.6V DQ are disabled | -10  | 10   | μΑ    |  |  |  |  |

| Output Low Voltage              | VOL       | IOL=2.1mA, Vcc = 3.3V                   | 0.4  | -    | v     |  |  |  |  |

| Output High Voltage             | VOH       | IOH=-400uA Vcc = 3.3V                   | -    | 2.4  | v     |  |  |  |  |

| Input Low Voltage               | VIL       | Vcc = 3.3V                              | -    | 0.66 | v     |  |  |  |  |

| Input High Voltage              | VIH       | Vcc = 3.3V                              | 2.64 | -    | v     |  |  |  |  |

|                                 | Power     | supply (VCC =3.3V)                      |      |      |       |  |  |  |  |

| Operating Current,<br>Page Read | ICC1 CODE | trc=25ns CE/=Vil, Iout=0mA              | -    | 30   | mA    |  |  |  |  |

| Operating Current,<br>Program   | ICC2 CODE | -                                       | -    | 30   | mA    |  |  |  |  |

| Operating Current,<br>Erase     | ICC3 CODE | -                                       | -    | 30   | mA    |  |  |  |  |

| Standby Current TTL             | ISB ICC4  | CE/=XIH WP/=0V/VCC, VCC & VCCQ          | -    | 1    | mA    |  |  |  |  |

| Standby Current CMOS            | ISB_ICC5  | CE/=VCC-0.2Ve WP/=0V/VCC, VCC & VCCQ    | -    | 50   | μΑ    |  |  |  |  |

### Electrical test system description Parameter tests list table (Macronix as an example)

| 0/00-2 20/ 10-      | # Dulea Laurale =00/ to 1/00 Ter | AC<br>out and Output Timing Levels=VCC/2) Mode 0 t               | end t | TTI at |           |

|---------------------|----------------------------------|------------------------------------------------------------------|-------|--------|-----------|

| Program Time        | Prog                             | PROGRAM PAGE operation time, internal<br>ECC disabled, GO NOGO   | -     | 600    | µs.       |

| Block Erase Time    | tBera                            | BLOCK ERASE operation time , GO NOGO                             |       | 3.5    | ms        |

| CLE Setup Time      | 1CLS                             | -                                                                | -     | 10     | ns        |

| CLE Hold Time       | SCLH.                            | -                                                                |       | 5      | ns        |

| CE/ Setup Time      | 105                              | *                                                                |       | 15     | ns        |

| CE/ Hold Time       | <u>10</u> H                      | GO NOGO                                                          | -     | 5      | ns        |

| WE/ Pulse Width     | <u>tWP</u>                       | *                                                                | -     | 10     | ns        |

| ALE Setup Time      | 186.5                            | ¥.                                                               | - 44  | 10     | ns        |

| ALE Hold Time       | 1819                             | •                                                                |       | 5      | ns        |

| Data Setup Time     | 10.5                             | *                                                                | +     | 7      | ns        |

| Data Hold Time      | 28                               | -                                                                | -     | 5      | ns        |

| Write Cycle Time    | tWC                              | -                                                                | •     | 20     | ns        |

| WE/ High Hold Time  | <u>tWH</u>                       | GONOGO                                                           | -     | 7      | ns        |

| ALE to RE/ Delay    | <u>MAR</u>                       | GO NOGO                                                          | -     | 10     | ns        |

| CLE to RE/ Delay    | 1018                             | GO NOGO                                                          | -     | 10     | ns        |

| RE/ Pulse Width     | 18.9                             |                                                                  |       | 10     | ns        |

| Read Cycle Time     | 1BC                              |                                                                  | -     | 20     | ns        |

| RE/ Access Time     | 1856                             | +                                                                | •     | 16     | ns        |

| WE High to Busy     | tWB                              | -                                                                | -     | 100    | ns        |

| CE/ Access Time     | 1CEA                             | ÷                                                                | -     | 25     | ns        |

| RE/ High Hold Time  | IREH                             | GO NOGO                                                          | +     | 7      | ns        |

| WP/ High to WE/ Low | DXXX                             | GO NOGO                                                          | •     | 100    | ns        |

|                     |                                  | Functionality                                                    |       |        |           |

| Checkerboard        | Func ChkBrd                      | Erase memory Write , Read pattern<br>Checkerboard Block#0 Note 1 | •     | -      | Pass/Fail |

| SLC-March           | Func SLC March                   | Erase memory Write , Read with SLC March<br>Algorithm Block#0    | -     | -      | Pass/Fail |

| Retention Check     | Euro READ Childred Retention     | Read with \$55 \$AA on Block#81<br>(OFF samples only)            | •     | -      | Pass/Fail |

Note 1: Pattern checkerboard is made of Erase, Write 55 & AA, Read 55 & AA, Erase, Write AA & 55, Read AA & 55, Erase

#### Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

### Electrical test system description Specific SLC – March detection Algorithm

#### Specific March algorithm fore NAND FLASH for :

AF

- TF: Transition Fault Detection

- AF: Address Fault Detection

- DF: Data Fault Detection

SLC-March employs march algorithm and patternbased approach to detect all faults.

- The march algorithm detects faults by controlling the operation address order.

- The pattern P<sub>SLC</sub> detects faults happened in a page

#### SAF, SOF

$SLC - March = \{(e); \Uparrow (r1, w0, r0); \clubsuit (r0);$

DF

w0 : a write operation on a page of all-0's pattern r0/r1: a read operation on a page, expecting all-0's/all-1's pattern

Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

TF

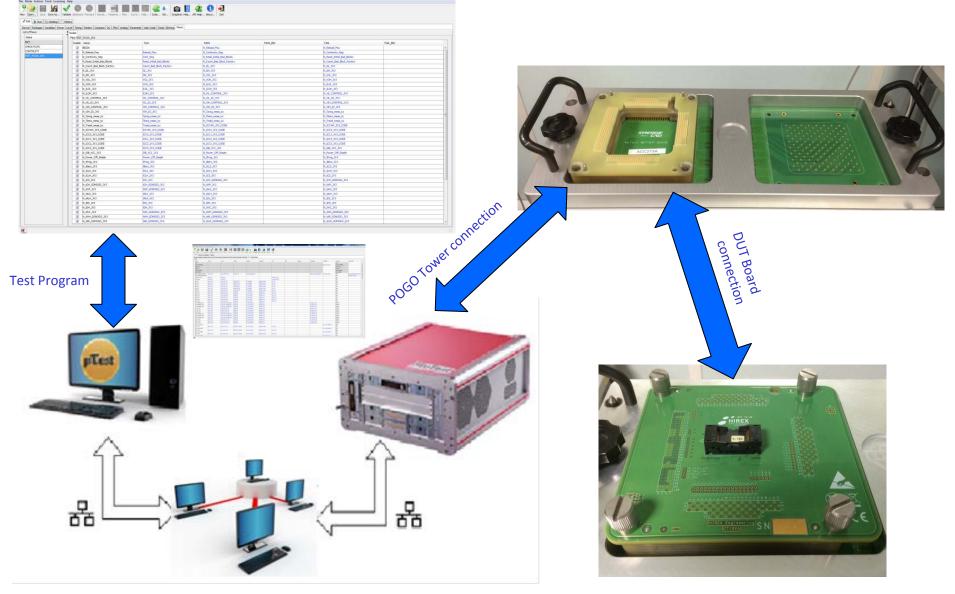

# Test tooling descriptions Hardware and Software

In situ (FPGA based tester and biasing boards)

Electrical test system using an ATE (Automatic Test Equipment)

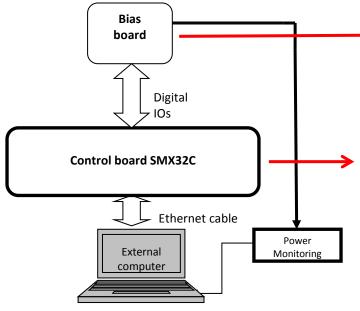

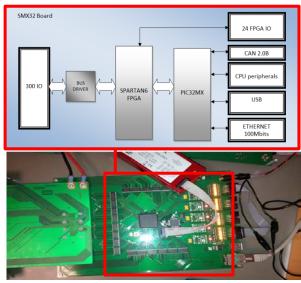

### In situ: FPGA based tester and biasing boards Hardware description

### User interface app. on PC

- Configures test sequence

- Sends test sequence commands to Control board

- Records error data, status data and log data received from Control board

#### Control board SMX32C

**Bias board**

- Control board

- Controls and commands DUTs in parallel

- Sends status and error data to the PC

Hirex Engineering a Company of Alter Technology

**Overall Campaign Results**

- In situ (FPGA based tester and biasing boards).

- Electrical test system using an ATE (Automatic Test Equipment).

- Based on results we have differentiated two families

- Preselected references for SEE irradiation campaigns

- Non selected references for SEE irradiation campaigns

|                         | HRX – Non selected refe                   |                                           |                                  |                                  |                                            |  |  |  |  |

|-------------------------|-------------------------------------------|-------------------------------------------|----------------------------------|----------------------------------|--------------------------------------------|--|--|--|--|

|                         |                                           |                                           |                                  |                                  |                                            |  |  |  |  |

|                         | Hynix                                     | Hynix Toshiba Macron                      |                                  | Spansion                         | Winbond                                    |  |  |  |  |

| Part type               | H27U4G8F2D                                | TC58NVG2S0HTAI0                           | MX30LF4G18AC                     | S34ML04G200TFI00                 | W29N01GVSIAA                               |  |  |  |  |

| Туре                    | SLC Nand Flash<br>Memory                  | SLC Nand Flash<br>Memory                  | SLC Nand Flash<br>Memory         | SLC Nand Flash<br>Memory         | SLC Nand Flash<br>Memory                   |  |  |  |  |

| Capacity / Organization | 4 GB / 512M x 8BIT<br>1 bit ECC/528 bytes | 4 GB / 512M x 8BIT<br>8 bit ECC/512 bytes | 4 GB / 512M x 8 BIT<br>4 bit ECC | 4 GB / 512M x 8 BIT<br>4 bit ECC | 1 GB / 128M x 8 BIT<br>1 bit ECC/528 bytes |  |  |  |  |

| Date code               | 1503 1509                                 |                                           | 1444                             | 1442                             | 1437                                       |  |  |  |  |

| Package                 | TSOP48 (12x20mm)                          | TSOP48 (12x20mm)                          | TSOP48 (12x20mm)                 | TSOP48 (12x20mm)                 | TSOP48 (12x20mm)                           |  |  |  |  |

w a sha sha sha sha wa fa wa w

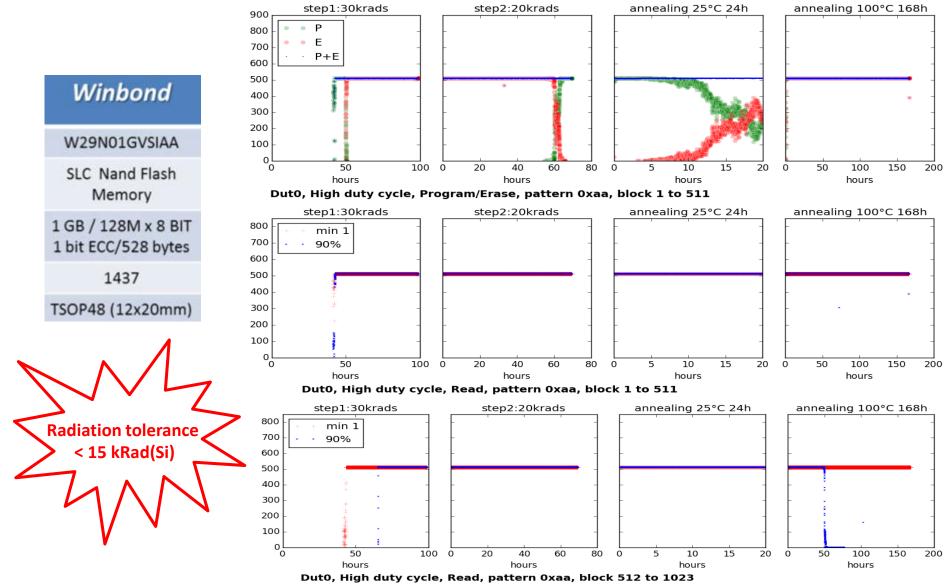

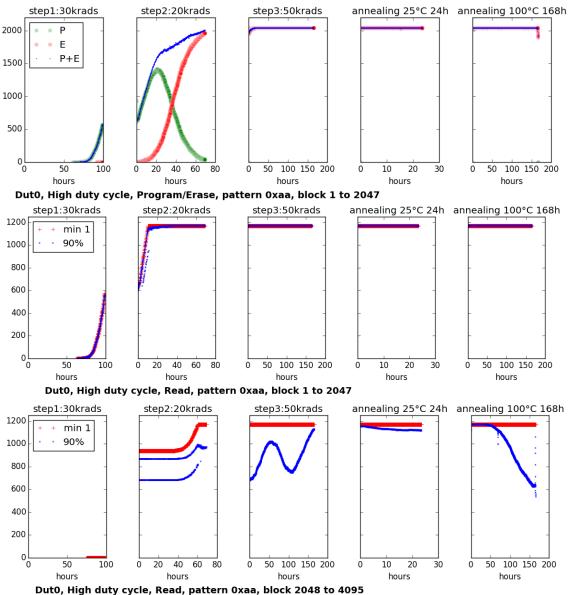

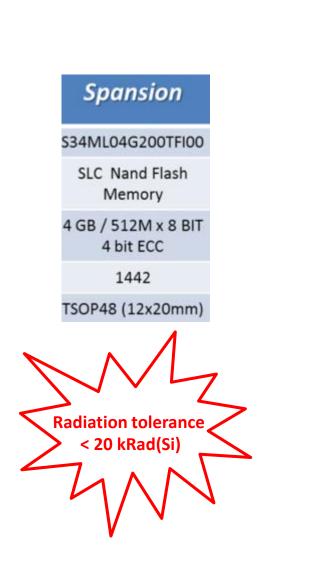

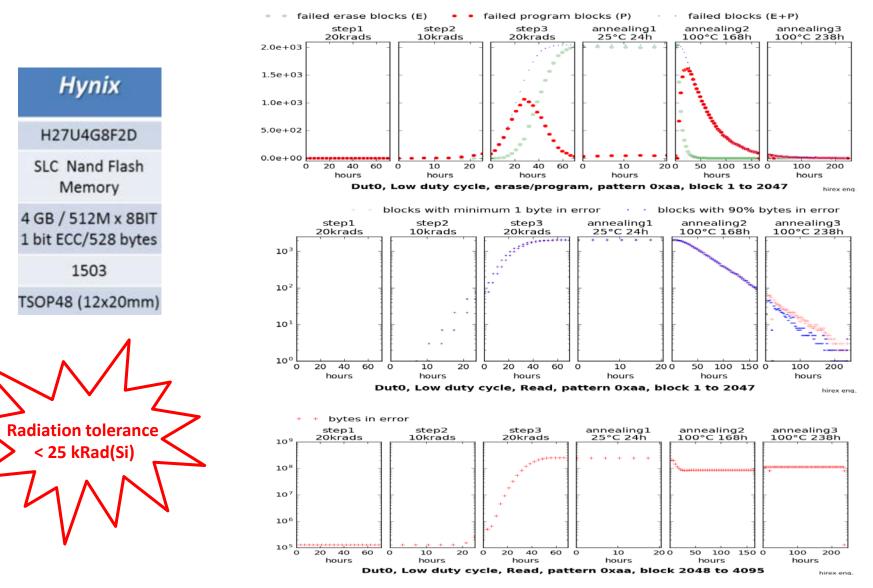

### In situ: HDC non selected references results

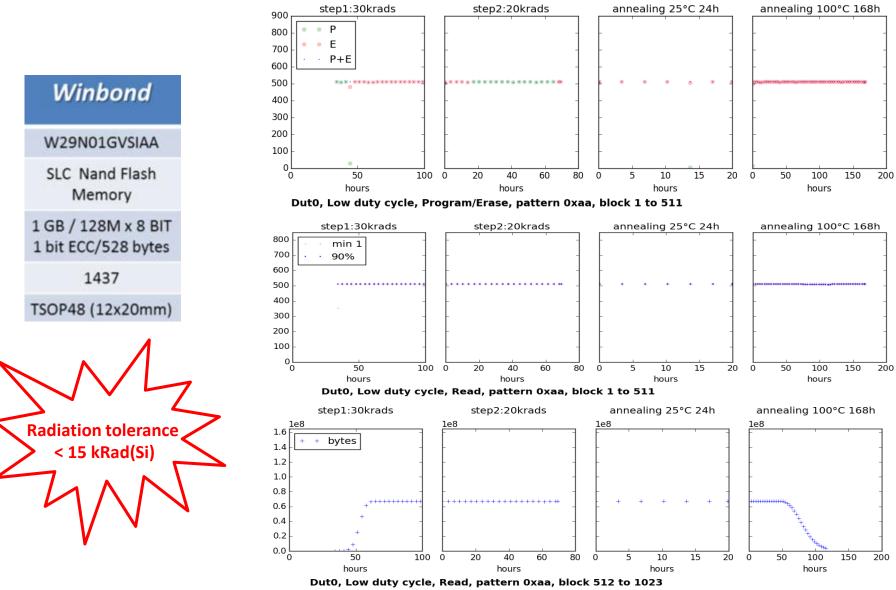

### In situ: LDC non selected references results

#### Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

21

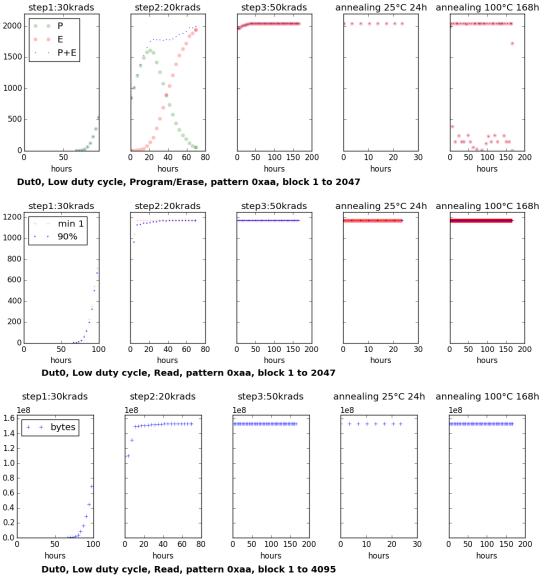

### In situ: HDC non selected references results

#### Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

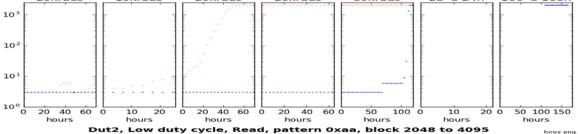

### In situ: LDC non selected references results

### In situ: HDC non selected references results

### In situ: LDC non selected references results

#### HIREX ENGINEERING ATE: HDC and LDC non selected references results

|              |                  |                              |                    | BIAS HDC (H                  | IGH DUTY CYCLE)    |                              |                    |                             |                    |                            |                 |

|--------------|------------------|------------------------------|--------------------|------------------------------|--------------------|------------------------------|--------------------|-----------------------------|--------------------|----------------------------|-----------------|

| Manufacturer | Product          | DC                           |                    | Power Supply                 |                    | AC (timing                   | AC (timings)       |                             | Functional         |                            |                 |

|              |                  | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                       | Annealing 24h/168h |                            |                 |

| Winbond      | W29N01GVSIAA     | 30 kRad(Si)                  | Complete           | 50 kRad(Si)                  | Complete           | 30 kRad(Si)                  | Complete           | 30 kRad(Si)                 | Complete           |                            |                 |

| Spansion     | S34ML04G200TFI00 | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | 30 kRad(Si)                  | No Recovery        | 30 kRad(Si)                 | No Recovery        |                            |                 |

| Hynix        | H27U4G8F2D       | 30 kRad(Si)                  | Partial            | No Failure up to 50kRad(Si)  | Complete           | 30 kRad(Si)                  | Partial            | 30 kRad(Si)                 | Partial            |                            |                 |

|              |                  |                              |                    | BIAS LDC (L                  | OW DUTY CYCLE)     |                              |                    |                             |                    |                            |                 |

| Manufacturer | Product          | DC                           |                    | Power Sup                    | ply                | AC (timings)                 |                    | Functional                  |                    |                            |                 |

|              |                  | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                       | Annealing 24h/168h |                            |                 |

| Winbond      | W29N01GVSIAA     | 30 kRad(Si)                  | Complete           | 50 kRad(Si)                  | Complete           | 30 kRad(Si)                  | Complete           | 30 kRad(Si)                 | Complete           |                            |                 |

| Spansion     | S34ML04G200TFI00 | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | 30 kRad(Si)                  | No Recovery        | 30 kRad(Si)                 | No Recovery        |                            |                 |

| Hynix        | H27U4G8F2D       | 30 kRad(Si)                  | Partial            | No Failure up to 50kRad(Si)  | Complete           | 30 kRad(Si)                  | Partial            | 30 kRad(Si)                 | Partial            |                            |                 |

|              |                  |                              |                    | BI                           | AS OFF             |                              |                    |                             |                    |                            |                 |

| Manufacturer | Product          | DC                           |                    | Power Sup                    | ply                | AC (timing                   | gs)                | Functional                  |                    | Retention                  |                 |

|              |                  | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                       | Annealing 24h/168h | Steps                      | Annealing 24h/1 |

| Winbond      | W29N01GVSIAA     | No Failure up to 50kRad(Si)  | Complete           | 50 kRad(Si)                  | Complete           | No Failure up to 50kRad(Si)  | Complete           | No Failure up to 50kRad(Si) | Complete           | No Failure up to 50kRad(Si | ) Complete      |

| Spansion     | S34ML04G200TFI00 | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | 100 kRad(Si)                 | No Recovery        | 100 kRad(Si)                | No Recovery        | 50 kRad(Si)                | No Recovery     |

| Hynix        | H27U4G8F2D       | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | 100 kRad(Si)                | Partial            | 100 kRad(Si)               | No Recovery     |

| 1            |                  |                              |                    |                              |                    |                              |                    |                             |                    |                            |                 |

PLACH DUTY CYCLE

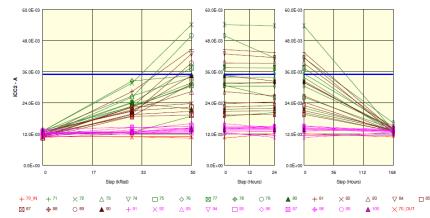

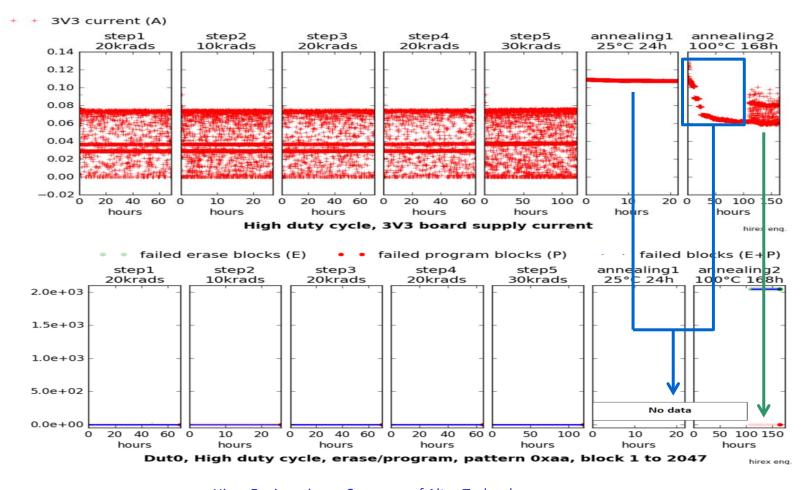

#### Parameter : Operating Current. Program : ICC2

Test conditions :

Unit : A

Spec Limit Max : 35.0E-03

Spec limits are represented in bold lines on the graphic.

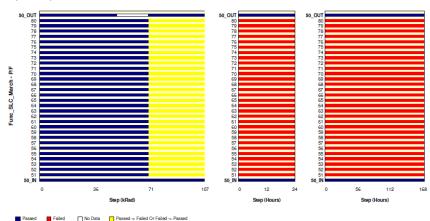

#### Parameter : SLC-March : Func\_SLC\_March

Test conditions : Erase memory Write . Read with SLC March Algorithm Block#0 Unit : Pass/Fail No spec limit specified.

#### Passed Failed No Data Passed -> Failed Or Failed -> Passed

#### **Examples: Winbond ICC and SLC\_March functional test**

A 86

#### Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

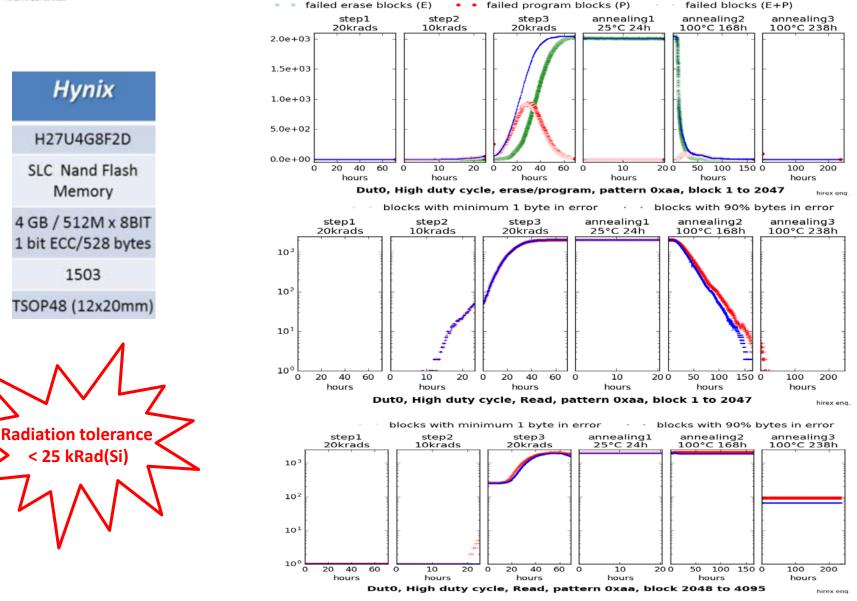

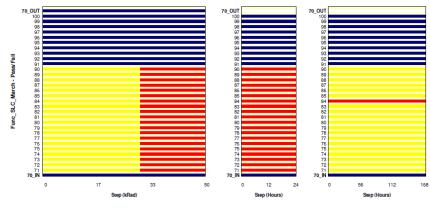

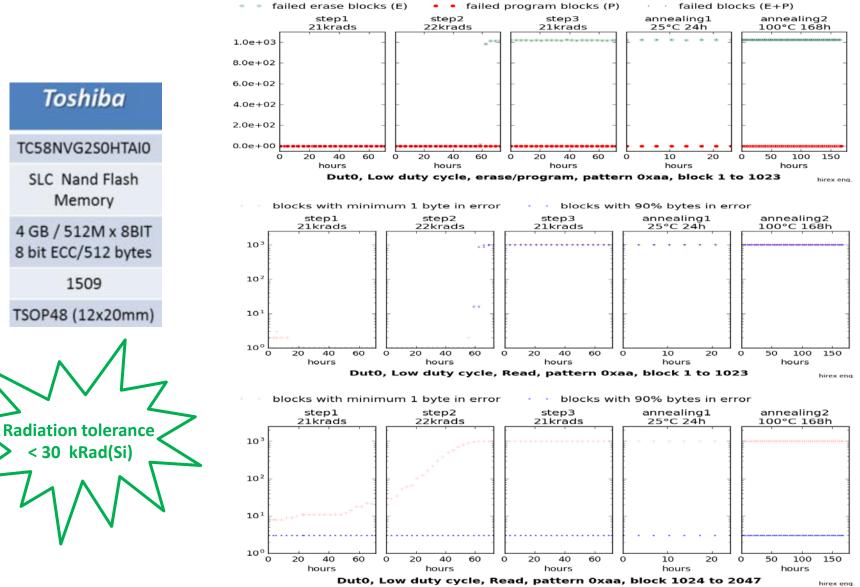

### In situ: HDC selected references results

### In situ: LDC selected references results

#### Hirex Engineering a Company of Alter Technology

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

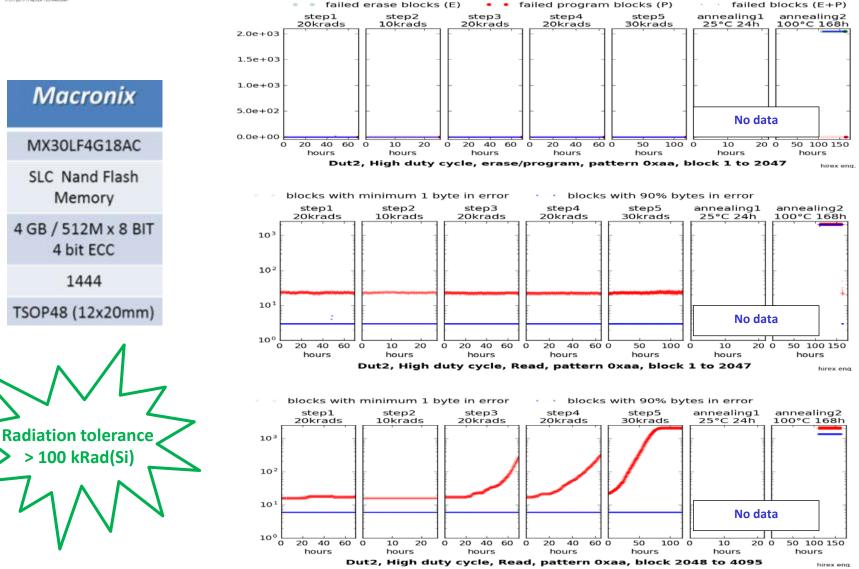

### In situ: HDC selected references results

March 2017

### In situ: LDC selected references results

### **ATE: HDC and LDC selected references results**

|              | BIAS HDC (HIGH DUTY CYCLE) |                              |                    |                              |                    |                              |                    |                              |                    |             |                                       |

|--------------|----------------------------|------------------------------|--------------------|------------------------------|--------------------|------------------------------|--------------------|------------------------------|--------------------|-------------|---------------------------------------|

| Manufacturer | Product                    | DC                           |                    | Power Supp                   | ply                | AC (timing                   | ζs)                | Functiona                    | al                 |             |                                       |

|              |                            | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | h Steps                      | Annealing 24h/168h | -           | ļ                                     |

| Toshiba      | TC58NVG2S0HTAI0            | No Failure up to 200kRad(Si) | Complete           | No Failure up to 200kRad(Si) | Complete           | 50 kRad(Si)                  | No Recovery        | 30 kRad(Si)                  | No Recovery        | 1           | , , , , , , , , , , , , , , , , , , , |

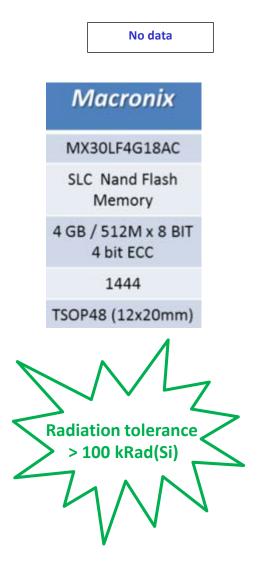

| Macronix     | MX30LF4G18AC               | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | No Recovery        | No Failure up to 100kRad(Si) | No Recovery        | 1           | ļ                                     |

| 1            |                            |                              |                    | BIAS LDC (L                  | OW DUTY CYCLE)     |                              |                    |                              |                    |             | ļ                                     |

| Manufacturer | Product                    | DC                           |                    | Power Supp                   | ply                | AC (timing                   | {s)                | Functiona                    | al                 |             | , j                                   |

|              |                            | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | h Steps                      | Annealing 24h/168h |             |                                       |

| Toshiba      | TC58NVG2S0HTAI0            | No Failure up to 200kRad(Si) | Complete           | No Failure up to 200kRad(Si) | Complete           | 50 kRad(Si)                  | No Recovery        | 50 kRad(Si)                  | No Recovery        | 1           | ļ                                     |

| Macronix     | MX30LF4G18AC               | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | No Recovery        | No Failure up to 100kRad(Si) | No Recovery        | 1           | ļ                                     |

| 1            |                            |                              |                    | BI                           | IAS OFF            |                              |                    |                              |                    |             |                                       |

| Manufacturer | Product                    | DC                           |                    | Power Supp                   | ply                | AC (timing                   | s))                | Functiona                    | al                 | Reten       | ition                                 |

| l            |                            | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | Steps                        | Annealing 24h/168h | h Steps                      | Annealing 24h/168h | Steps       | Annealing 24h/168h                    |

| Toshiba      | TC58NVG2S0HTAI0            | No Failure up to 200kRad(Si) | Complete           | No Failure up to 200kRad(Si) | Complete           | 150 kRad(Si)                 | Complete           | 100 kRad(Si)                 | Partial            | 50 kRad(Si) | No Recovery                           |

| Macronix     | MX30LF4G18AC               | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | Complete           | No Failure up to 100kRad(Si) | No Recovery        | No Failure up to 100kRad(Si) | No Recovery        | 30 kRad(Si) | No Recovery                           |

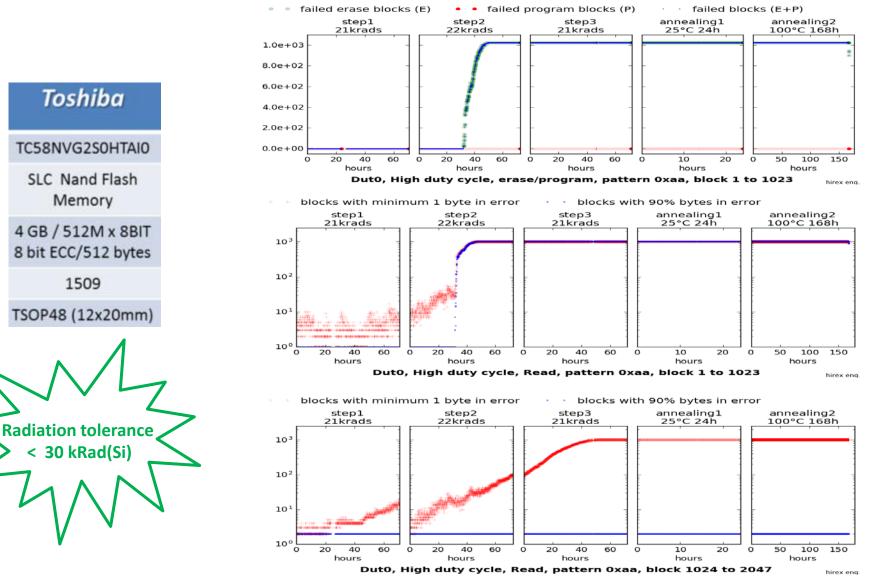

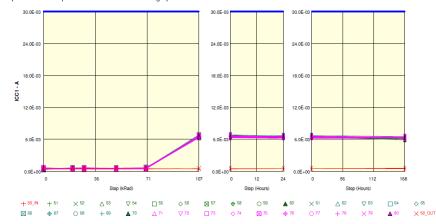

Spec Limit Max : 30.0E-03 Spec limits are represented in bold lines on the graphic.

No spec limit specified.

#### **Examples: Macronix ICC and SLC\_March functional test**

# Lessons Learning forces for further investigations

March 2017

### Lessons Learning forces For further investigations

- We have observed that after a certain cumulated dose rate (#100 kRad(Si), the power reset (ON/OFF) has an influence on the device functionality (MACRONIX).

- > This phenomenon is detected during the continuous BIAS current monitoring along the irradiation and annealing steps.

### 2<sup>nd</sup> irradiation campaign description

- > Performed on MACRONIX selected part for heavy ion test.

- 20 additional parts have been irradiated.

- 10 parts using HDC (High Duty Cycle) bias.

- 10 parts using LDC (Low Duty Cycle) bias.

- No Power ON/OFF.

- 1 single irradiation step followed by 24h @ 25°C and 168h @ 100°C:

- From 0 kRad(Si) up to 150 kRad(Si) for the MACRONIX parts.

- A cycle of READ/WRITE will be performed at each "virtual irradiation" steps (each 20 kRad(Si).

- Electrical measurements performed at the end of the irradiation steps and after each annealing.

|      | Campaign<br>Macronix - 2ème essai |                |          |                  |          |                  |            |      |                   |  |  |

|------|-----------------------------------|----------------|----------|------------------|----------|------------------|------------|------|-------------------|--|--|

|      |                                   |                |          |                  |          |                  |            |      |                   |  |  |

| Step | Dose Rate (Rad/H)                 | Dose (Rad(Si)) | St       | art Date         | Ei       | nd Date          | Total Dose | Step | Comment           |  |  |

| #1   | -                                 | -              | Jeudi    | 02/02/2017 16:00 | Jeudi    | 02/02/2017 16:00 | -          | Init | Installation      |  |  |

| #2   | 300                               | 20100          | Jeudi    | 02/02/2017 16:00 | Dimanche | 05/02/2017 11:00 | 20100      | R/W  |                   |  |  |

| #3   | 300                               | 21600          | Dimanche | 05/02/2017 11:00 | Mercredi | 08/02/2017 11:00 | 41700      | R/W  |                   |  |  |

| #4   | 300                               | 21600          | Mercredi | 08/02/2017 11:00 | Samedi   | 11/02/2017 11:00 | 63300      | R/W  |                   |  |  |

| #5   | 300                               | 21600          | Samedi   | 11/02/2017 11:00 | Mardi    | 14/02/2017 11:00 | 84900      | R/W  |                   |  |  |

| #6   | 300                               | 21600          | Mardi    | 14/02/2017 11:00 | Vendredi | 17/02/2017 11:00 | 106500     | R/W  |                   |  |  |

| #7   | 300                               | 21600          | Vendredi | 17/02/2017 11:00 | lundi    | 20/02/2017 11:00 | 128100     | R/W  |                   |  |  |

| #8   | 300                               | 22500          | Lundi    | 20/02/2017 11:00 | Jeudi    | 23/02/2017 14:00 | 150600     | 150K | Out for Annealing |  |  |

| #9   | 24                                | -              | Jeudi    | 23/02/2017 16:00 | Vendredi | 24/02/2017 16:00 | Room/24H   | 24H  |                   |  |  |

| #10  | 166                               | -              | Vendredi | 24/02/2017 18:00 | Vendredi | 03/03/2017 16:00 | 100°C/168H | 168H | End RVT           |  |  |

Macronix 2<sup>nd</sup> TID campaign

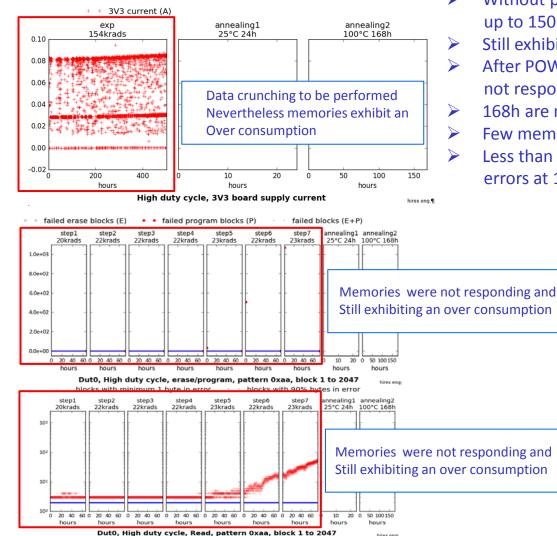

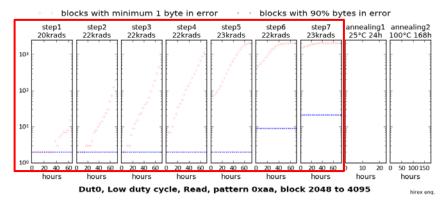

### 2<sup>nd</sup> irradiation campaign HDC results

### Erase/Program Read pattern :

- Without power ON/OFF memories are functional up to 150 kRad(Si).

- Still exhibiting an over consumption after the POWER OFF.

- After POWER OFF same phenomenon, memories are not responding.

- 168h are not enough to allow memories to recover.

- Few memory errors occur around 100 kRad(Si).

- Less than 100 blocks are concerned with these memory errors at 150 Krad(Si)

#### Hirex Engineering a Company of Alter Technology

hirex eng

This document is the property of Hirex Engineering, it cannot be reproduced or communicated without its authorization

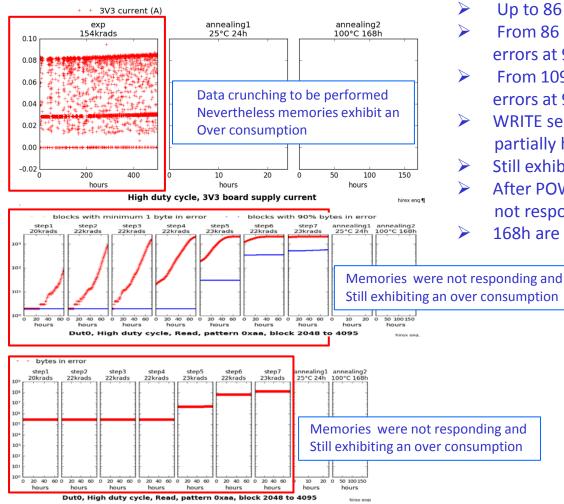

### 2<sup>nd</sup> irradiation campaign HDC results

### Read pattern :

- Without power ON/OFF memories are functional up to 150 kRad(Si).

- > Up to 86 krad(Si) no major block errors at 90%.

- From 86 kRad(Si) up to 109 kRad(Si) less than 50 block errors at 90%.

- From 109 kRad(Si) up to 154 kRad(Si) less than 600 block errors at 90%.

- WRITE sequence after each 20 kRad(Si) allows to partially heal the memory errors.

- Still exhibiting an over consumption after the POWER OFF.

- After POWER OFF same phenomenon, memories are not responding.

- 168h are not enough to allow memories to recover.

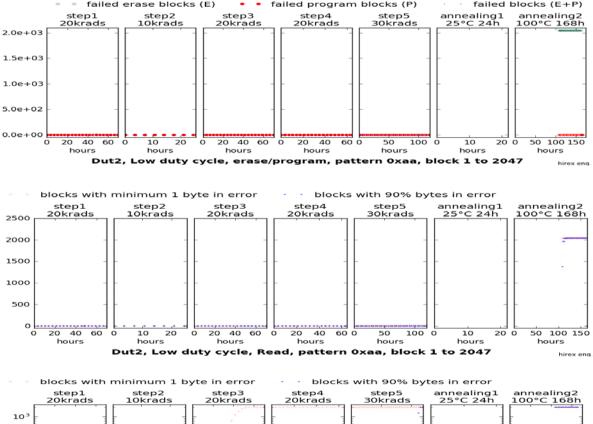

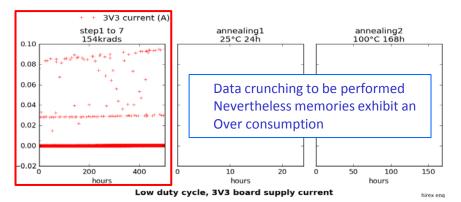

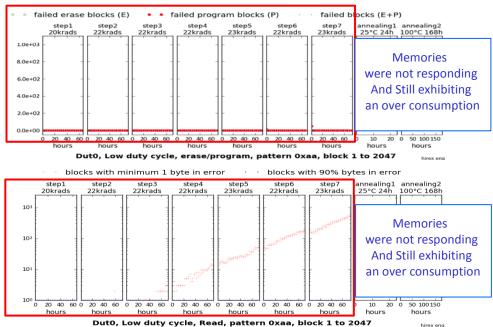

### 2<sup>nd</sup> irradiation campaign LDC results

### Erase/Program Read pattern :

#### Read pattern :

#### **Erase/Program Read pattern :**

- Without power ON/OFF memories are functional up to 150 kRad(Si).

- Still exhibiting an over consumption after the POWER OFF.

- After POWER OFF same phenomenon, memories are not responding.

- 168h are not enough to allow memories to recover.

- Memory block errors occur around 86 kRad(Si).

- Less than 600 blocks are concerned with these memory errors at 150 Krad(Si)

#### **Read pattern :**

Same behavior as the HDC Read pattern but with much less block errors (150 kRad(Si) → less than 10 blocks in error at 90%.

#### Hirex Engineering a Company of Alter Technology

# Conclusions

- Despite the fact that technologies are similar, radiation tolerance across the 5 selected NAND FLASH is different.

- Charge pump block seems to be the critical element for all the memories except MACRONIX as it's involved in ERASE/PROGRAM operation.

- One out of the 5 selected devices seems suitable for JUICE mission (MACRONIX) at least for Total dose radiation.

- > POWER ON/OFF has an impact on total dose radiation tolerance.

- Much less memory errors when ERASE/PROGRAM cycles are implemented periodically compare to the READ only test sequence.

- For the READ only test, number of errors is related to number of reads (more reads, more errors)

# **Proposed Next Steps**

- For MACRONIX device extend the 168h @ 100°C annealing to check if memory reach a complete recovery.

- After partial or complete recovery, read memory erroneous bytes and check the number of bits in error per byte to verify how much ECC is able to correct erroneous data.

- Perform a failure analysis to understand if the over consumption issue is related to a specific element/area or if it's spread across the full die.

# **Backup Slides**

# **Company Overview**

## **TÜV NORD Group main areas**

**ENERGY**

MOBILITY

**HEALTH AND NUTRITION**

NATURAL RESOURCES

**AEROSPACE & ELECTRONIC**

# Aerospace & Electronic Business Unit

Alter technology group: with 30 years experience in the sector.

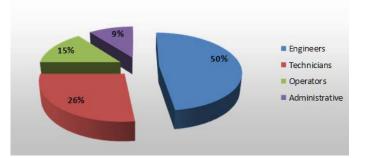

## **Hirex Profile**

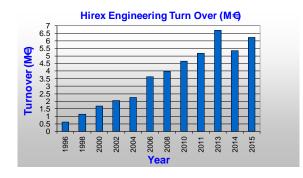

- Hirex Engineering founded in January 1993.

- Hirex Engineering joined ALTER Technology Group in January 2007.

- ATN based in Madrid, Seville, Roma, Portsmouth and Shanghai.

- ATN employees 230 as of today.

- ATN Turn-over 65 M€.

- 100% Privately owned by TÜV NORD since 29th June 2011.

- Hirex Engineering :

- Based in Toulouse.

- 48 employees as of today.

- 1800 m<sup>2</sup> Facility.

- Certified ISO 9001, EN 9100 and ISO 14001.

44

**Expertise & Activities**

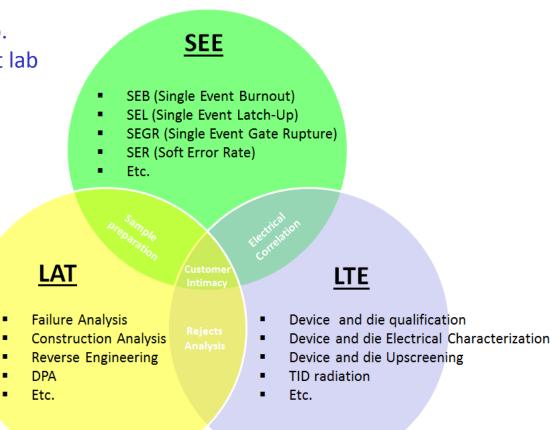

## **3 labs for a focused organization:**

- SEE: Radiation lab.

- LAT: Semiconductor Technology lab.

- LTE: Electrical & environmental test lab

Hirex Engineering a Company of Alter Technology