# MICROCHIP Aerospace & Defense BU

**Radiation Characterization**

ATMX150RHA Rad-Hard Platform The solution for mixed-signal ASIC

Project supported by CNES

June 20, 2018

# ATMX150RHA PD-SOI 150nm Technology

- □ Funded by CNES (Centre National d'Etudes Spatiales)

- Evaluation and Qualification of ATMX150RHA ASICs offer

- Radiation Evaluation of LDMOS: TID and SEB/SEGR

CNES CONTRACT n° 4500037909 / DCT094 of 2011.09.27

CNES CONTRACT n° 4500044431 / DCT094 of 2013.10.24

Radiation Characterization of other devices (HV, MOS 5V, Bipolars & Capacitors) :

TID and SEB/SEGR

CNES CONTRACT n° 4500053131 / DCT094 of 26.08.2016

Microchip ATMX150RHA Rad-Hard CMOS 150nm cell-based ASIC family Radiation Characterization Test Report - Total Dose (TID) and Single Event Effects (SEE)

eric.leduc@microchip.com severine.furic@microchip.com david.truyen@microchip.com david.dangla@cnes.fr

# **ATMX150RHA – GENERAL FEATURES**

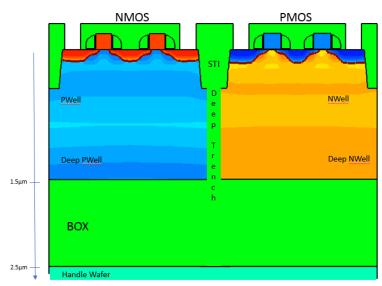

#### □ 150nm SOI CMOS process

- □ 5 Level Metals + Thick Metal AlCu / 1.8V core supply

- □ Life time 20 years at Tj=110°C

- Dual deep-well for SEL immunity

- Deep Trench option

#### Hardened Library

- Logic std cells and DFF

- □ Hardened I/Os 5V, 3.3V & 2.5V, LVDS, PCI

- High Voltage Devices

- 25V, 45V LDMOS

- A catalog of pre-qualified analog blocks

- □ Regulators/ PLL/ RC-Oscillator/ BandGap/ Comparator/ Analog-MUX/DAC-ADC...

- □ Virage compiler of SRAM/DPRAM/ROM

- □ Qualification of Hardened ASICs (-55°C to 125°C) up to 22MGates equivalent NAND2

- Standard Evaluation Circuit (SEC) with 44M transistors

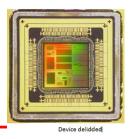

View of ATMX150RHA technology

# **ATMX150RHA – PDK Devices Content**

| Device<br>type | Domain | Device<br>Name                 | 77KRHA<br>1.8V/3.3V<br>5V 250Å | 77K9RHA<br>1.8V/3.3V<br>5V 250Å oxide<br>HVEE-NVM |

|----------------|--------|--------------------------------|--------------------------------|---------------------------------------------------|

|                |        |                                | 37 masks                       | 47 masks                                          |

|                | 1.8V   | Nfet - Pfet                    | •                              | •                                                 |

|                |        | Nfethvt - Pfethvt              |                                | •                                                 |

|                | 3.3V   | Nfetox3 - Pfetox3              | •                              | •                                                 |

|                |        | Pfetox3hw                      | •                              | •                                                 |

|                |        | Nfetox3de                      | •                              | •                                                 |

|                |        | Nfetox3de_esd                  | •                              | •                                                 |

|                |        | Nfetox3_ring                   | •                              | •                                                 |

|                |        | Nfetox3de_ring                 | •                              | •                                                 |

|                | 5V     | Nfetox5 - Pfetox5              | •                              | •                                                 |

| N/P MOS        |        | Nfetox5de -<br>Pfetos5de       | •                              | •                                                 |

|                |        | Nfetox5de_esd<br>Pfetox5de_esd | •                              | •                                                 |

|                |        | Nfetox5_ring                   | •                              | •                                                 |

|                |        | Nfetox5de_ring                 | •                              | •                                                 |

|                | HV     | nwhvfet                        |                                | •                                                 |

|                |        | nmvfet                         |                                | •                                                 |

|                |        | nmvafet                        |                                | •                                                 |

|                |        | nhvfet/phvfet                  |                                | •                                                 |

|                |        | nhvfet_ring                    |                                | •                                                 |

|                |        | phvafet                        |                                | •                                                 |

|                | 25V    | Idnfet25 / Idpfet25            |                                | •                                                 |

| LDMOS          | 45V    | Idnfet45 / Idpfet45            |                                | •                                                 |

|                |        | pnp_vert_b                     | •                              | •                                                 |

| BIPOLAR        |        | Inpn                           | •                              | •                                                 |

# **ATMX150RHA – PDK Devices Content**

| Device<br>type | Domain | Device<br>Name  | <u>77KRHA</u><br>1.8V/3.3V<br>5V 250Å | 77K9RHA<br>1.8V/3.3V<br>5V 250Å<br>HVEE-NVM |

|----------------|--------|-----------------|---------------------------------------|---------------------------------------------|

|                |        | dfreew_esd      |                                       | •                                           |

|                |        | dfreew120_esd   |                                       | •                                           |

| DIODE          |        | dz_6p2          |                                       | •                                           |

|                |        | dz_6p2_esd      |                                       | •                                           |

|                |        | nd3p3_esd       | •                                     | •                                           |

|                |        | schottky        | •                                     | •                                           |

|                |        | cmim34          | •                                     | •                                           |

|                |        | Momcap – Moscap | •                                     | •                                           |

| CAPACITOR      |        | moscapox3       | •                                     | •                                           |

|                |        | Moscaphv        | •                                     | •                                           |

|                |        | P2bncap         |                                       | •                                           |

|                |        | Rplow – Rphigh  | •                                     | •                                           |

| RESISTOR       |        | Rpolysh         | •                                     | •                                           |

| KESISTOR [     |        | Rpolyhigh       | •                                     | •                                           |

|                |        | Rnsd - Rpsd     | •                                     | •                                           |

| OTUED          |        | Fuse            | •                                     | •                                           |

| OTHER          |        | hwc             |                                       | •                                           |

#### PDK 2.8 delivered with

- Radiation Characterization report

- Generic and Aerospace design rules

- Generic and Hardened Pcell library with associated electrical models (Spectre, Hspice, Eldo)

# **ATMX150RHA – Total Ionizing Dose**

Tests in compliance with ESCC 22900 & MIL-Std 883 TM1019

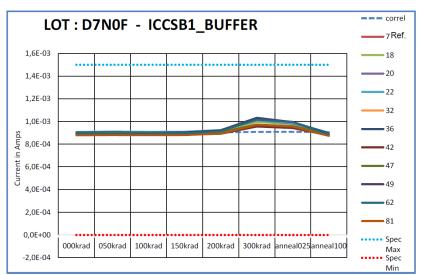

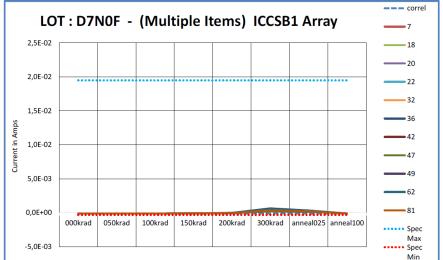

# Total Ionizing Dose (TID) - Digital offer qualification

- 1.8V and 3.3V devices (Standard Evaluation Circuit SEC)

- Successfully tested up to 300krad(Si) with ELT \* 3.3V devices

3.3V IOs buffer Stand-by current vs cumulative dose Specification=1.5E-3 A

1.8V Core Stand-by current vs cumulative dose Specification = 2E-2 A

QML-RHA level R Qualified up to 100 krad(Si) RHA

# **ATMX150RHA – Total Ionizing Dose**

Tests in compliance with ESCC 22900 & MIL-Std 883 TM1019

# Total Ionizing Dose (TID) - Digital offer qualification

#### 1.8V elementary devices - NMOS

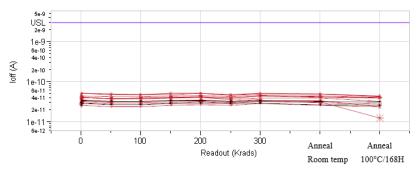

Threshold Voltage and Subthreshold current of NMOS 1.8V vs Cumulated Dose

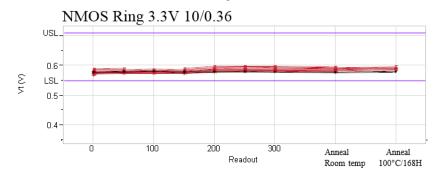

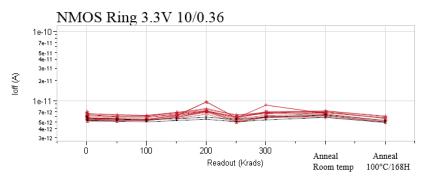

#### □ 3.3V elementary devices - NMOS

Threshold Voltage and Subthreshold current of NMOS 3.3V ELT vs Cumulated Dose

#### TID supply conditions

| Devices | Drain | Source | Gate | Body | HWC | NB |

|---------|-------|--------|------|------|-----|----|

| NMOS    | 0V    | 0V     | 3.6V | 0V   | 0V  | 0V |

# **ATMX150RHA – Total Ionizing Dose**

Tests in compliance with ESCC 22900 & MIL-Std 883 TM1019

# Total Ionizing Dose (TID) - Digital offer qualification

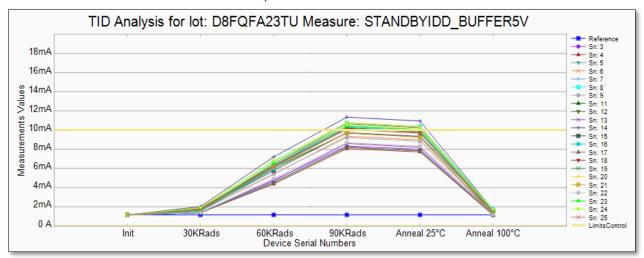

- 5V devices (Standard Evaluation Circuit SEC) : IO5V

- TID sensitivity increased due to 250 Å oxide (same as HV devices)

- Successfully tested up to 60 krad(Si) with ELT\* layout

5V IOs buffer Stand-by current vs cumulative dose Specification=10 mA

QML-RHA level P

up to 30 krad(Si) RHA

# **ATMX150RHA – Single Events**

Tests in compliance with ESCC 25100 & MIL-Std 883 TM 1020

# Single Event Effects Digital offer qualification

- ☐ Single Event Latch-up @ Vcc<sub>max</sub>, 125°C

- ☐ Full SEL Immunity by Deep trench

- ☐ Dual Deep Well solution for high integration

- $\rightarrow$  SEL LET<sub>th</sub>> 78MeV.cm<sup>2</sup>/mg

Standard Evaluation Circuit of ATMX150RHA

# ATMX150RHA — Single Event Upset Tests in compliance with ESCC 25100 & MIL-Std 883 TM 1020

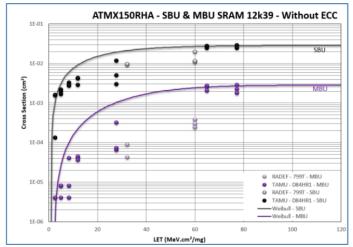

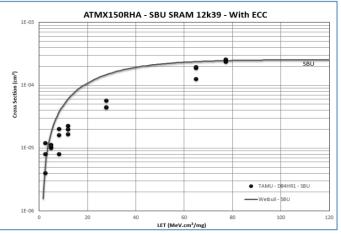

# Single Events Upset (SEU): RAM Virage compiler

MBU/SEU Hardening by Scrambling and ECC

| Memory     | LET threshold | SEU Xs              | Weibull        | param. |

|------------|---------------|---------------------|----------------|--------|

| type       | (MeV.cm²/mg)  | (cm²/dev)           | W              | S      |

| SRAM16k32  | 1             | 3.61E-2             | 24             | 1.2    |

| SRAM12k39  | 1             | 2.85E-2             | 24             | 1.2    |

| DPRAM6k39  | 1             | 1.95E <sup>-2</sup> | 22             | 1.0    |

| DPRAM2k8   | 1             | 1.15E-3             | 25             | 0.9    |

| TPRAM 1k16 | 1             | 5.55E-4             | 30             | 0.8    |

| SRAM12k39  | 1             | 2.56E-4             | 30             | 1.3    |

| with ECC   | •             | 2.502               | 30             | 1.5    |

| DPRAM6k39  | 3.3           | 1.30E-5             | 28             | 1.2    |

| with ECC   |               |                     | ***            |        |

| Memory     | LET threshold | MBU Xs              | Weibull param. |        |

| type       | (MeV.cm²/mg)  | (cm²/dev)           | W              | S      |

| SRAM16k32  | 2             | 1.74E <sup>-3</sup> | 40             | 1.8    |

| SRAM12k39  | 2             | 2.84E <sup>-3</sup> | 40             | 1.8    |

| DPRAM6k39  | 2             | 2.43E <sup>-3</sup> | 34             | 1.4    |

Summary of the SBU/MBU Weibull parameters (LET<sub>th</sub>, cross section, W & S) for main RAMs Virage

SBU/MBU cross section vs LET -12k39mux16 SRAM with/without ECC

# ATMX150RHA — Single Event Upset Tests in compliance with ESCC 25100 & MIL-Std 883 TM 1020

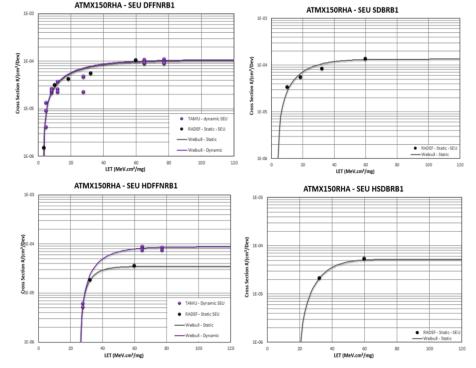

# Single Events Upset (SEU): Register files

#### HDFF LET > 26 MeV.cm<sup>2</sup>/mg

| Memory                       | LET threshold             | SEU Xs              | Weibull param. |     |  |

|------------------------------|---------------------------|---------------------|----------------|-----|--|

| type                         | (MeV.cm <sup>2</sup> /mg) | (cm²/dev)           | $\mathbf{W}$   | S   |  |

| DFFNRB1                      | 3.0                       | 1.08E <sup>-4</sup> | 22             | 1.0 |  |

| DFFNRB2                      | 3.6                       | 1.14E <sup>-4</sup> | 22             | 1.0 |  |

| SEU hard.<br>DFFNRB1         | 26                        | 8.70E <sup>-5</sup> | 16             | 1.2 |  |

| SEU hard.<br>DFFNRB2         | 26                        | 1.06E <sup>-4</sup> | 16             | 1.2 |  |

| Scan Std DFF<br>SDBRB1       | 3.6                       | 1.34E <sup>-4</sup> | 20             | 1.3 |  |

| Scan Std DFF<br>SDBRB2       | 3.6                       | 1.06E <sup>-4</sup> | 20             | 1.1 |  |

| Scan SEU hard.<br>DFF SDBRB1 | 18.5                      | 5.25E <sup>-5</sup> | 20             | 1.7 |  |

| Scan SEU hard.<br>DFF SDBRB2 | 18.5                      | 4.00E <sup>-5</sup> | 22             | 1.7 |  |

Summary of the SBU/MBU Weibull parameters (LET<sub>th</sub>, cross section, W & S) for main Register Files

SEU cross sections of shift registers in cm<sup>2</sup>/device a device is a chain of 1024 DFF

# **ATMX150RHA – SER synthesis**

# **RAM Virage compiler**

| SRAM - GEO mission pr | MTBF       |        |        |         |

|-----------------------|------------|--------|--------|---------|

|                       | SER        | Device | Word   | bit     |

|                       | (/dev/day) | (day)  | (year) | (year)  |

| SEU 16k x 32          | 4.59E-01   | 2.18   | 98     | 3129    |

| SEU 12k x 39          | 3.47E-01   | 2.88   | 97     | 3784    |

| SEU 12k x 39 w ECC    | 6.99E-04   | 1431   | 48163  | 1878347 |

| MBU 16k x 32          | 1.16E-03   | 862    | 38696  |         |

| MBU 12k x 39          | 2.06E-03   | 485    | 16343  |         |

| DPRAM - GEO mission | MTBF       |        |        |          |

|---------------------|------------|--------|--------|----------|

|                     | SER        | Device | Word   | bit      |

|                     | (/dev/day) | (day)  | (year) | (year)   |

| SEU 6k x 39         | 4.22E-01   | 2.37   | 40     | 1556     |

| SEU 2k x 8          | 2.64E-02   | 37.88  | 213    | 1700     |

| SEU 6k x 39 w ECC   | 2.27E-05   | 44053  | 741536 | 28919920 |

## **DFF**

| DFF - GEO mission profile | MTBF       |         |

|---------------------------|------------|---------|

|                           | SER        | Device  |

|                           | (/DFF/day) | (year)  |

| DFF drive 1               | 7.81E-07   | 3508    |

| Scan DFF drive 1          | 6.40E-07   | 4281    |

| Hardened DFF D1           | 3.75E-09   | 730594  |

| Hardened Scan DFF D1      | 2.50E-09   | 1095890 |

#### **Environmental Conditions**

using OMERE Solar Min Z=1 to 92 Aluminum shielding of 1g/cm<sup>2</sup>

# **ATMX150RHA - LDMOS 25V & 45V**

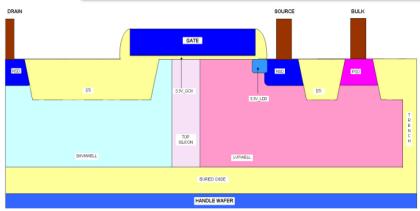

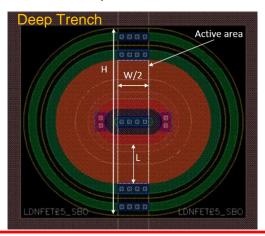

# **LDMOS Characterization**

high voltage lateraly diffused LDMOS

LDNMOS 25V with SBO configuration schematic cross section

#### □ 3.3V Gate oxide

- Enables to pass up to 45V on Drain

- Long diffused Drain to increase R<sub>ON</sub>

- Ring layout enclosed by Deep Trench : Full SEL immunity

# **ATMX150RHA – LDMOS 25 & 45V**

#### ☐ Cumulated Dose on LDMOS

Supply conditions during irradiation

| Devices | H<br>(µm) | Drain | Source | Gate | Body | HWC | NB | Read outs<br>krad(Si) |

|---------|-----------|-------|--------|------|------|-----|----|-----------------------|

| LDNMOS  | 10.76     | 0V    | 0V     | 3.6V | 0V   | 0V  | 0V | 30, 60, 90            |

| LDPMOS  | 10.36     | 0V    | 25V    | 25V  | 25V  | 0V  | 0V | 30, 60, 90            |

|         |           |       |        |      |      |     |    |                       |

| Devices | Н         | Drain | Source | Gate | Body | HWC | NB | Read outs             |

|         | (µm)      |       |        |      |      |     |    | krad(Si)              |

| LDNMOS  | 12.76     | 0     | 0      | 3.6V | 0    | 0V  | 0V | 30, 60, 90            |

| LDPMOS  | 13.56     | 0V    | 45V    | 45V  | 45V  | 0V  | 0V | 30, 60, 90            |

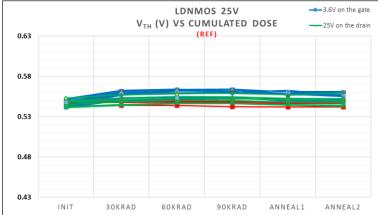

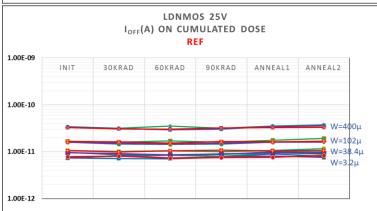

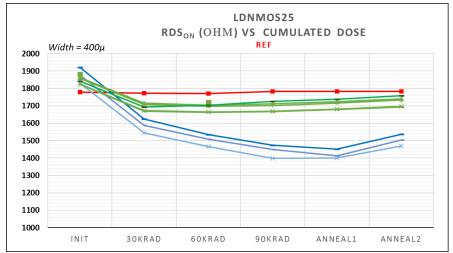

- No drift up to 90krad(Si)

- Threshold voltage (Vt)

- Saturation current (I<sub>ON</sub>)

- Subthreshold leakage current (I<sub>OFF</sub>)

- Drift with dose on Drain/Source On resistance (Rds<sub>on</sub>)

- No gate rupture

- □ Post radiation model @30krad(Si) for LDMOS 25V & 45V

# ATMX150RHA – LDMOS 25V

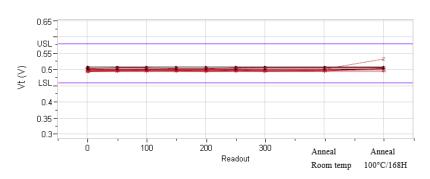

#### ■ LD NMOS 25V on cumulated dose

- LDMOS 25V & 45V Evaluation

- Threshold voltage (Vt)

- Subthreshold current (I<sub>OFF</sub>)

Radiation electrical model

@ 30krad(Si) RHA

- On Resistance (RDS<sub>ON</sub>)

- Major drift managed by Gate supply

→ 3.6V on the gate

---25V on the drain

# **ATMX150RHA – LDMOS 25 & 45V**

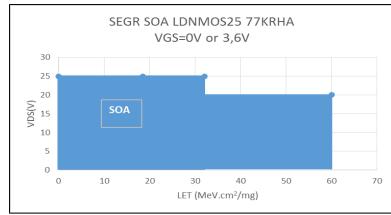

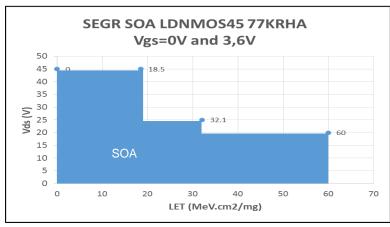

# Single Event Burnout (SEB) & Single Event Gate Rupture (SEGR) on LDMOS

#### □ SEL immune by Deep Trench

####

No SEB encountered up to 60 MeV.cm²/mg at Vcc<sub>max</sub>, 25°C, 1E7#/cm²

#### SEGR LDPMOS:

■ No SEGR up to a LET of 60MeV.cm²/mg at Vcc<sub>max</sub>, 25°C, 1E7#/cm²

#### SEGR LDNMOS

- No SEGR up to a LET of 60MeV.cm²/mg @ VGSmax and VDS=0V (25°C, 1E7#/cm²)

- SEGR encountered when drain supply: Safe Operating Area (SOA) (25°C, 1E7#/cm²)

# **ATMX150RHA – Conclusion**

### Further Works

- Cumulated dose Characterization

- HV devices (15V oxide)

- Capacitors

- Bipolar transistors

- → Associated electrical model after TID

- → PDK delivery

- SEB / SEGR Characterization

- HV devices (15V oxide)

- Capacitors

- Bipolar transistors

- → Associated Radiative SOA

© 2018 Microchip Corporation.

Microchip@, Microchip logo and combinations thereof, Enabling Unlimited Possibilities@, and others are registered trademarks or trademarks of Microchip Corporation or its subsidiaries. ARM@, ARM Connected@ logo and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be the trademarks of others.

Disclaimer: The information in this document is provided in connection with Microchip products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Microchip products, EXCEPT AS SET FORTH IN THE Microchip TERMS AND CONDITIONS OF SALES LOCATED ON THE Microchip ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL Microchip BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF Microchip HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Microchip makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Microchip does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Microchip products are not suitable for, and shall not be used in, automotive applications. Microchip products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.