### ON-BOARD COMPLEX IMAGE PROCESSING BASED ON FPGA ACCELERATION FOR AUTONOMOUS NAVIGATION IN SPACE

OBDP 2019 ESTEC 27/02/2019

Paul Băjănaru – Avionics and On-Board Software Engineer GMV Innovating Solutions SRL Contact : pbajanaru@gmv.com

David González Arjona – Avionics and On-Board Software Engineer GMV Aerospace and Defence SAU Contact : dgarjona@gmv.com

**ም BLOG f ະ** ጸ ነ መ እ

CAMPHORVNAV : Project, Image Processing Approach

Visual Based Navigation Camera Baseline

Model-in-the-loop

Breadboard Validation

Features & Performances

Camera Optical Unit : Characterization & Corrections

Optical Testbech & Robotic Testbench

Conclusions

# CAMPHORVNAV at OBDP2019

- Project within MREP Program

- □ Part of Phobos Sample Return Mission (PhSR)

- Vision-Based Navigation Camera (VBNC) providing three modules:

- COU BB (Camera Optical Unit)

- IPB EM (Image Processing Board)

- Image Processing algorithms Firmware

- □ VBNC used in the Descent & Landing Phase to Phobos

□ TRL6

- Extended with lessons learned from QUEENS-FPGA

- Quality assessment Evaluation of European NanoXplore SW for brave FPGA

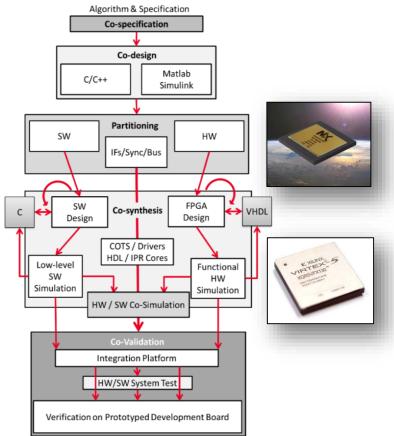

## IMAGE PROCESSING HW ACCELERATION

- Used in the D&L Phase

- HW/SW Co-design approach

- GNC implemented in LEON4

- Image Processing Board

- □ 2 FPGAs: Virtex5 and NG-MEDIUM Rad-Hard FPGAs

- □ Based on Feature Tracking HW-acceleration

- □ Algorithm control & commands in LEON4

- □ Camera and OBC Interfaces Management in FPGA

Page 4

# CAMPHORVNAV at OBDP2019

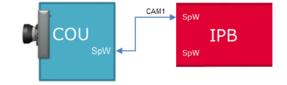

- SpaceWire I/F with the IPB  $\rightarrow$  CCSDS/PUS Tailoring to allow re-use compatibility

- Design Based on CMV4000 → 2048x2048 pixels of 8-12bits

- CNES radiation tests campaigns available

- Same detector as in PILOTB+ Lunar Lander scenario (Requirement established by ESA in the ITT)

- COU is used for two scenarios, scientific and navigation, with trade-off decisions to better fulfill their different requirements:

- For QSO Operations cropping Center 1024x1024 pixels provide a 10 degrees FoV

- For Descent & Landing Binning the 2048x2048 to 1024x1024 provides 20 degrees FoV

- ProAsic3 FPGA implements read-out, transmission and low-level image pre-processing

- Bias/Gain Frame correction

- Bad Pixel Correction

- Binning/Cropping

- GMV Demonstration on NG-MEDIUM inside IPB

- COTS Optics used of 35 mm

- TRL5 for the Cameral Optical Unit Breadboard implemented by MCSE partner

Page 5

#### CAMPHORVNAV at OBDP2019 IMAGE PROCESSING BOARD

- Processing FPGA: Image Processing HW IP-core (high-performance & high-density SRAM-based FPGA)

- Virtex-5 VFX130T

- Memory controllers

- Hosts RelNav IP

- Data Acquisition and Synchronization

- □ FPGA-FPGA parallel communication

- Interfaces FPGA:

- In NG-Medium

- □ Image Pre-Processing Capabilities (Camera corrections)

- Deals with the interfaces of the IPB to the external world (smaller Flash-based FPGA)

Interfaces FPGA (IPB-IFF) Processing FPGA (IPB-PRF) RST COU-BB SpW nower CAM-1 Programming power SpW SpW Ctrl & clock Relative Navigation Image clock Managemnt SpW HW IP-core Ctrl OBC SpW NVRAM SDRAM Flash SDRAM Ctrl Ctrl M/TC 8 IPB-IFF TM/ TC & Managemnt IPB-PR MRAM NVRAM MRAM Mana gemnt Flash Ctrl Ctrl EGSE ctrller EGSE HPC\_A FPGA-FPGA I/F FPGA-FPGA I/F HPC B

27/02/2019

Page 6

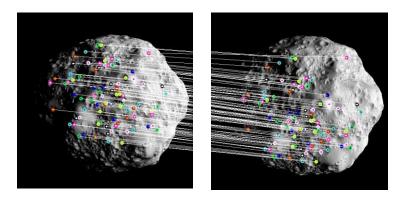

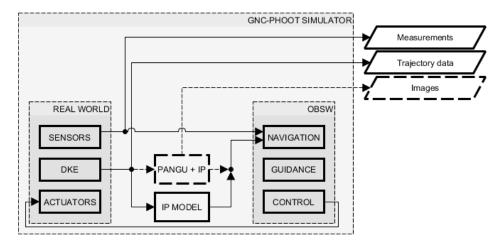

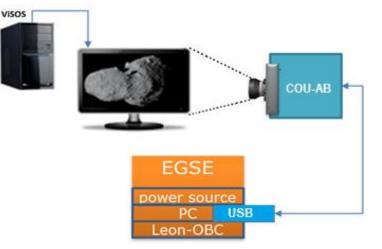

### CAMPHORVNAV at OBDP2019 MIL & IMAGES GENERATION

- **Simulink model** Developed within the scope of *GNC for* Phootprint Descent and Landing project.

- New version of PANGU 4 that includes updated model of Phobos. Note that image rendering is very demanding (powerful PC is needed)

- Medium-Fidelity (performance model) vs High fidelity (PANGU + IP implementation in SW)

- Autocodeble models for GNC algorithms (Used in Leon2, updated and verified for Leon4)

- Simulator is used to obtain the relevant trajectory data, measurements and PANGU images to verify and validate the implemented IP algorithms.

- Optical facility (ViSOS) will use a database for the trajectory data obtained using the Simulator in the medium/high fidelity, including the set of PANGU generated images of the trajectory.

- In case of ViSOS or platform-ART tests only trajectory and measurements data are used, therefore, no PANGU is required

Input model of Phobos with selected landing site area (left); Enhanced DEM with craters rendered by PANGU (right).

Page 7

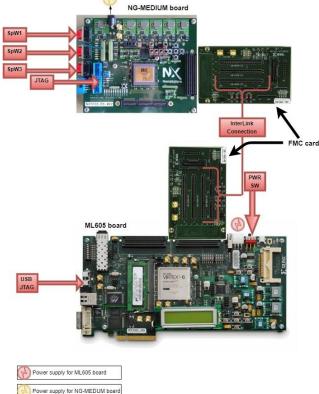

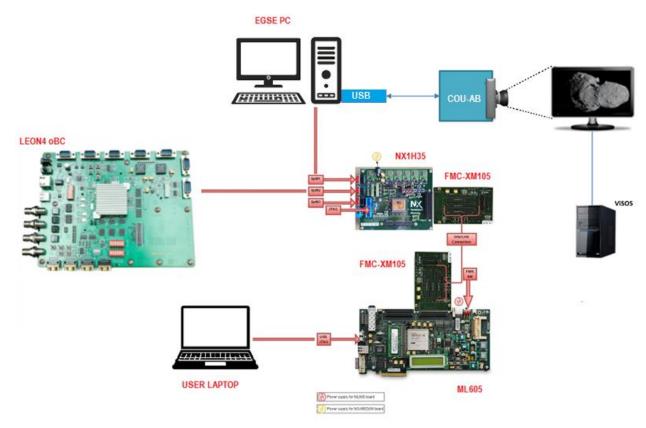

### CAMPHORVNAV at OBDP2019 IPB BB: INTERMEDIATE STEP

IPB BB includes:

- □ NG-Medium DevKit2

- □ Xilinx ML605 Board

- □ 2 x FMC-XM105

- Wiring and SpW interfacesGMVScope FPGA debugger

Virtex-6 suitable breadboard demonstrator for Virtex-5:

- $\square$  Over-constraining the IPB-PRF clock at x1.15

- □ USE DPORT set to False for DSP48E1

- □ FMC Boards for I/O standard matching

- □ Over-constraining external memory (Burst Chop 4 mode)

- □ System Monitor (SYSMON)

CAMPHORVNAV at OBDP2019 IPB BB VALIDATION

#### **Tests performed:** EGSE PC Housekeeping Services Verification □ Debug (Memory W/R) HILLING -□ Full Navigation Verification LEON4 oBC NX1H35 Features FMC-XM105 10 10 AL 14 Track New X Tracked FMC-XM105 Lost 7777711111111 **USER LAPTOP** MI 60 Point wash for NO-MEDUN board

**gm**/

ON-BOARD COMPLEX IMAGE PROCESSING BASED ON FPGA ACCELERATION FOR AUTONOMOUS NAVIGATION IN SPACE

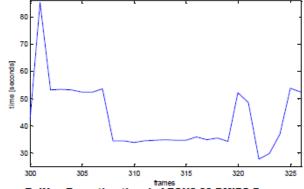

### **FEATURES & PERFORMANCES**

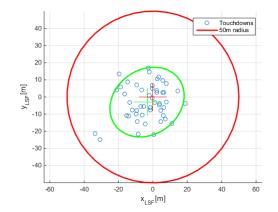

- Landing Accuracy : better than 50 meters

- Pre-Processing functionalities implemented in the Interfaces FPGA

- Feature Tracking Algorithm implemented in the Processing FPGA

- GNC algorithm running in SW in the LEON4 On-Board Computer

- RelNav Processing Time in FPGA : 120 150 ms

**RelNav Execution time in LEON2 86 DMIPS Processor**

| GNC       | Horizontal Position<br>Error [m] | Horizontal<br>Velocity<br>[cm/s] | Vertical<br>Velocity<br>[m/s] | Final thrust<br>altitude [m] | Attitude<br>error<br>[deg] |

|-----------|----------------------------------|----------------------------------|-------------------------------|------------------------------|----------------------------|

| Minimum   | 0.748                            | 0.534                            | -0.860                        | 46.721                       | 0.141                      |

| Maximum   | 39.891                           | 3.813                            | -0.785                        | 54.712                       | 0.264                      |

| Mean      | 4.536                            | 1.611                            | -0.823                        | 51.408                       | 0.214                      |

| Std. Dev. | 14.830                           | 1.095                            | 0.017                         | 1.627                        | 0.025                      |

ON-BOARD COMPLEX IMAGE PROCESSING BASED ON FPGA ACCELERATION FOR AUTONOMOUS NAVIGATION IN SPACE

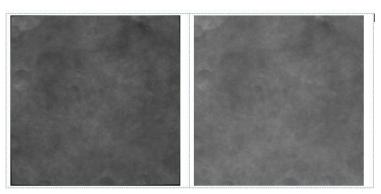

### **COU CHARACTERIZATION**

#### **Image Correction & Calibration**

Bright/Dark Field (Bias/Gain Tables Needed)

□ Bad Pixels (Bad Pixels Map Needed)

Lens Distortion (Intrinsic Matrix Needed)

#### **Image Comparison**

□ Structural Similarity Index Matrix (SSIM)

□ Peak Signal to Noise Ratio (PSNR)

□ Mean Square Error (MSE)

|                 | SSIM<br>[%] | PSNR<br>[dB] | MSE<br>[Pix Value] | Exposure<br>Time<br>[ms] |

|-----------------|-------------|--------------|--------------------|--------------------------|

| Limit<br>Values | 95.11       | 34.60        | 22.52              | 15                       |

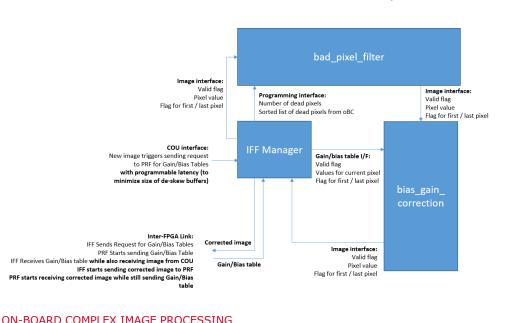

### LOW-LEVEL IMAGE PRE-PROCESSING

Page 12

#### **Image Correction & Calibration**

Bias/Gain Correction – Implemented in NG-Medium before RelNav Processing

Bad Pixel Correction – Implemented in NG Medium before RelNav Processing

Camera Distortion Correction – Software Implemented in EGSE PC

undistorted

BASED ON FOGA ACCELERATION FOR AUTONOMOUS NAVIGATION IN SPACE 27/02/2019

### **OPTICAL FACILITY VALIDATION**

**gmv**°

ON-BOARD COMPLEX IMAGE PROCESSING BASED ON FPGA ACCELERATION FOR AUTONOMOUS NAVIGATION IN SPACE

27/02/2019 Page 13

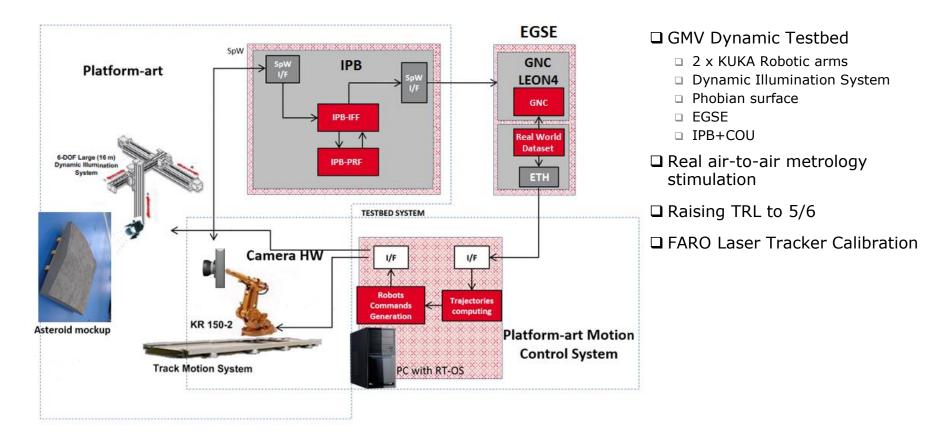

### platform-art© VALIDATION

- 2 space-graded FPGAs architecture for Image Processing Board, validated by means of breadboard integration with 2 commercial FPGA development kits.

- □ Image Pre-Processing functionality tested and validated using BRAVE FPGA.

- Capability of NG-Medium to deal with multiple high data-rate interfaces was demonstrated (spacewire routing of up to 4 links with redundandcy scheme).

- Reliable and accurate navigation solution achieved through complex image processing and through distributed on-board highly computationally capable chain (NG-Medium, Virtex-5(6), LEON4).

- Real-Time performance achieved by means of HW acceleration of the Feature Tracking algorithm (Feature tracking algorithm accelerated from average 43 seconds in LEON2 to average 130 milliseconds in FPGA).

GMV Speaker: Paul Bajanaru

*GMV: David Gonzalez-Arjona Paul Bajanaru Ruben Domingo Florin-Adrian Stancu Andrei Alexe Dragos Gogu Sergiu Sincan*

# THANK YOU

ESA TOs: Olivier Dubois-Matra Jorge Alves Sanjay Vijendran

Strain の BLOG f ヒ ぷ 識 in ふ

Alexand De