### Teledyne e2v

### Radiation Tolerant COTS+ Space Microprocessors

De-risking the introduction of ARM based solutions

#### Mikaël BALL

Project Leader – Space Processors Data Processing Solutions +33 7 77 36 01 75 mikael.ball@teledyne-e2v.com

#### **Thomas GUILLEMAIN**

Marketing & Business Development

Data Processing Solutions

+33 6 84 21 15 20

thomas.guillemain@teledyne-e2v.com

## T-e2v Space Processors Semiconductor Division

Page 2

<u>High Performance</u>, <u>High Reliability</u> Semiconductor solutions Addressing Critical functions of the complete signal chain in **<u>Demanding Applications</u> Specific Qualified versions** of many standard products Strategic Partnerships (NXP, ...) **Te2v Microprocessors Key Figures 30+ years experience** in up screening processors ~45 products launched during the last 20 years 10s to 100s of kunits shipped per year in Aerospace & Defense 100s of units shipped per year in Space Markets

Teledyne e2v current COTS+ Radiation Tolerant Microprocessors

Teledyne e2v Space Qualification Flows & Radiation Testing

Next steps: de-risking the introduction of ARM based solutions for Space

# Teledyne e2v COTS+ Microprocessors Space Offering

February 2019

## Commercial Space Dilemna What our customers are saying

### "Commercial Space dilemma"

Perform always more complex and powerful data processing into space Ensuring a decent level of radiation tolerance Reduced payload SWaP (Size, Weight & Power) Use devices with significant space heritage **Faster TTM** At an aggressive price if possible

#### **Rationale (non exhaustive)**

- Direct on board data processing

- Increased on board data processing requirements

- Higher level of data selection

- Higher accuracy level of data to be transmitted

- Increased Quality Of Service

- Increased autonomy

- Increased observation capabilities

- ....

Page 6

### **COTS** (Commercial off the shelf) components

Parts designed for **commercial applications** where the **manufacturer or vendor establishes** and **controls** the **specifications** for performance, configuration & reliability with no additional, external requirements.

## **COTS / COTS+ in Space applications**

**COTS can be used in Space**, but the **key points** will be to ensure they are **reliable for Space**

This is what Teledyne e2v brings & warrants in Space Microprocessors This is what our customers are requesting

## Teledyne e2v Space Microprocessors COTS+ Radiation Tolerant - Current Portfolio

Page 7

### **ORGANIC** package solutions

Ruggedized radiation tolerant technology Standard plastic package Device selection and lot validation

- PowerArchitecture®

- Dual Core Microprocessors

- 1.2-1.5 GHz

- 45nm SOI

- ECSS / NASA Grades Qualification

### **CERAMIC Non-Hermetic FlipChip**

Ruggedized radiation tolerant technology Advanced packaging on ceramic Standardized quality grade

- PowerArchitecture®

- Single Core Microprocessors

- 1.2 GHz

- 90nm SOI

- QML-Y Qualification

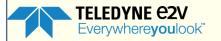

# Teledyne e2v Space Processors Where to find us?

P2020

Page 8

PC8548

## Teledyne e2v Space Qualification Flow

February 2019

## Organic Package Solutions ECSS / NASA Qualification Flow Purpose

Page 10

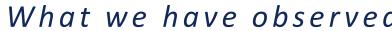

## Remove infant failures

Minimize risks of corner lots & corner parts

Assess the quality of the process

## ECSS / NASA Qualification Flow What Teledyne e2v puts in place

Page 11

Remove infant failures

Burn In

Minimize risks of corner lots & corner parts

Single Lot Date Code

100% Inspection

Assess the quality of the process

DPA

Destructive Physical Analysis

## ECSS / NASA Qualification Flow What we have observed

Page 12

We have observed rejected parts after 120 hours of Burn In!

> We have observed large variants from lot to lot!

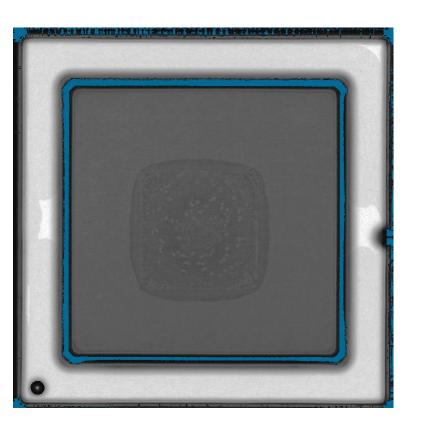

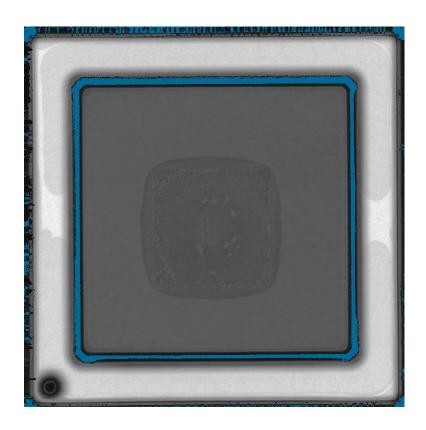

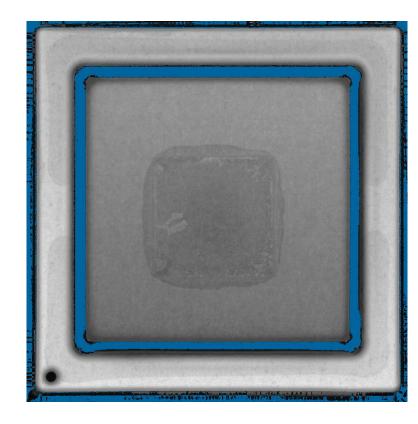

## **C-SAM Inspections**

Example

Page 13

### Worst case (FM lot)

Defect area: ~20%

Distributed small defects

### Best case (FM lot)

Defect area: ~3%

Few small defect near die center

#### Standard case (prototype lot)

Defect area: ~6.9%

Few larger defects on die edges

C-SAM: Confocal Scanning Acoustic Microscopy

# ECSS / NASA Qualification Flow High Level

## Space Up Screening

## Lot by Lot Qualification

# External visual & serialization Temperature cycling X-Ray

- 4. C-SAM inspection

- 5. Initial electrical meas. (pre-burn-in)

- 6. Engineering review

- 7. Static burn-in test @ 125°C (or max. temperature)

- 8. Post static burn in electrical meas. @ 25°C

- 9. Dynamic burn-in test @ 125°C (or max. temperature)

- 10. Post Dynamic burn in electrical meas. @ 25°C

- 11. Defective percentage calculation

- 12. Extreme temperature range electrical tests

- 13. Physical dimension controls

- 14. External visual

- 15. Packing & CoC

| 1. Baseline C-SAM                                        | Parts in Subgroup 1 only                                  |

|----------------------------------------------------------|-----------------------------------------------------------|

| 2. Preconditioning                                       | Moisture soak                                             |

|                                                          | SMT devices<br>Reflow simulation                          |

|                                                          | Through hole devices, Resistance to soldering temperature |

| 3. Electrical measurements                               | Per device specification                                  |

| 4. Life testing<br>Subgroup 1                            | HTOL, 125°C                                               |

|                                                          | Electrical measurement                                    |

| 5. Temperature cycling<br>Subgroup 1                     | Temperature cycling                                       |

|                                                          | Electrical measurement                                    |

|                                                          | C-SAM                                                     |

| 6. Highly accelerated stress<br>test (HAST) - Subgroup 2 | Biased HAST                                               |

|                                                          | Unbiased HAST                                             |

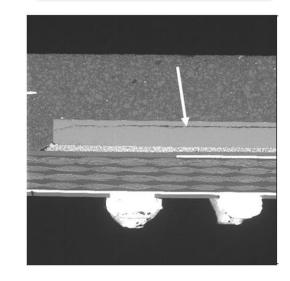

### DPA

(Destructive Physical Analysis)

#### **Targets**

- Integrity of the package (cracks)

- Quality of assembly (Void issues)

- Defects in the silicon die (cracks)

# Ceramic Non-Hermetic FlipChip Purposes of QML-Y Qualification

Page 15

Remove infant failures

Minimize risks of corner lots & corner parts

**Additional Quality** & Robustness level for **Space**

Assess the manufactured die quality

# Teledyne e2v QML-Y Space FLow High Level

Page 16

## Screening

| 1. Wafer lot Acceptance                     |  |

|---------------------------------------------|--|

| 2. Wafer sawing                             |  |

| 3. Die Visual selection                     |  |

| 4. Cust. or Teledyne e2v intern. inspection |  |

| 5. Die attach                               |  |

| 6. Die shear                                |  |

| 7. Underfill dispense & cure                |  |

| 8. SMD attach                               |  |

| 9. SMD visual inspection                    |  |

| 10. Substrate serialization                 |  |

| 11. Underfill CSAM                          |  |

| 12. Solder ball attach                      |  |

| 13. Precap                                  |  |

| 14. Heat sink attach                        |  |

| 15. Temperature cycling                     |  |

| 16. PIND Test                               |  |

| 17. Marking & serialization                 |  |

| 18. SMD X-Ray                                     |

|---------------------------------------------------|

| 19. Heat sink CSAM                                |

| 20. Visual inspection                             |

| 21. Initial (pre-burn-in) electrical meas.        |

| 22. Engineering review                            |

| 23. Dynamic Burn-In test                          |

| 24. Post dynamic BI electrical meas. @ 25°C       |

| 25. Static burn-in test                           |

| 26. Post Static BI electrical meas. @ 25°C        |

| 27. Calculate percent defective                   |

| 28. Extreme temperature range electrical test     |

| 29. Column attach (if applicable)                 |

| 30. Physical dimension control                    |

| 31. External visual                               |

| 32. Post column attach elec. test (if applicable) |

| 33. Customer or Teledyne e2v final inspection     |

| 34. Packing & CoC                                 |

## QCI

Group A

Group B

Group C

Group D1

Group D2

Group D3

Group D4

Group D5

Group D8

Group D9

## <u>Initial</u> <u>Qualification</u>

Group C

Solderability

Die shear

Resistance to solvents

SMD shear test

Ball shear

Column pull test

MSL3 + temperature

cycling + CSAM

MSL3 + THB + CSAM

MSL3 + Mech. Shocks & vibrations + CSAM

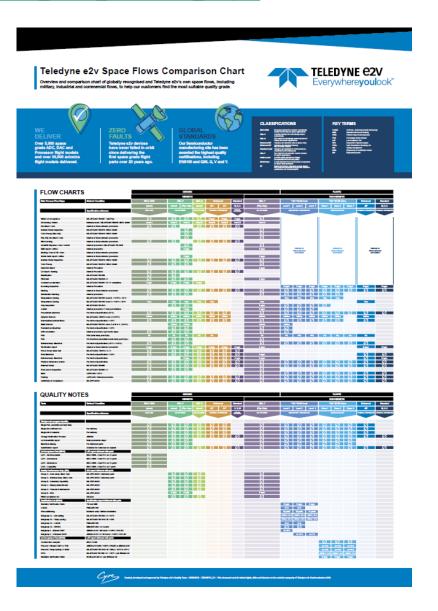

## Qualification Flow Poster

https://www.e2v.com/content/uploads/2018/07/Space Flows Comparison Chart TE2VSFCC V1.pdf

Page 17

Poster detailing the qualification flow and QCI implemented by Teledyne e2v following the below standards and guidelines:

Order a free printed poster from the link below or contact your local sales. <a href="https://www.e2v.com/products/semiconductors/space-semiconductors/">https://www.e2v.com/products/semiconductors/</a>

## Radiation Testing Key Highlights

## Teledyne e2v Space Microprocessors are all tested in Radiation

# Radiation Testing & Mitigation are mandatory

## T-e2v Space Processors Radiation Information

Page 19

#### **ORGANIC** package solutions

Ruggedized radiation tolerant technology Standard plastic package Device selection and lot validation

#### P2020

- SEU<sup>\*</sup> 53 LET

- **SEL** No LU at 63 LET

- 100 krad (Si)

Source: NASA JPL, Space Micro

### P5020

#### Commercial Space Grade by Te2v

- SEU<sup>\*</sup> 14 LFT

- **SEL** No LU expected (Tested until 14 LET)

- TID On Customer request

Source: NASA JPL

### **CERAMIC Non-Hermetic FlipChip**

Ruggedized radiation tolerant technology Advanced packaging on ceramic Standardized quality grade

#### PC7448

- SEU<sup>\*</sup> 62 LET

- No LU till 62 LET

- 100 krad (Si) TID

Source: EADS Nucletudes

### PC8548

### **QML-Y Microprocessors**

- SEU<sup>\*</sup> 86 LET

- SEL No LU till 86 LET

- 100krad (Si)

Source: Teledyne e2v

SEU\*: Data available up to xx LET

# Teledyne e2v New Space COTS Products Introduction

February 2019

## What's next @ Teledyne e2v New Product Introductions

## What challenges for New Space Microprocessors?

Perform more complex and powerful data processing in space

Reduced payload SWaP (Size, Weight & Power)

Good Level of radiation tolerance

Significant space heritage

## Teledyne e2v Space Compute Intensive solutions will follow our Space Qualification Flow

- Heavy Space Qualification

- Radiation Testing & Mitigation

## What's next @ Teledyne e2v New Product Introductions

LS1046-Space

## Performances, Ecosystem & Optimized Power

Quad 64-bit Arm® Cortex®-A72 cores

Qormino<sup>®</sup> QLS1046-Space

### <u>Performances, Ecosystem</u> <u>Optimized Power,</u> <u>Modularity, Faster TTM</u>

Quad 64-bit Arm® Cortex®-A72 cores

4GB DDR4 memory (72 bits, incl. 8 bits ECC)

Obsolecence Program

## What's next @ Teledyne e2v New Product Introductions

LS1046-Space

#### **Preliminary Radiation Results**

LS1046: Q3 2019

Qormino<sup>®</sup> QLS1046-Space

### **Preliminary Radiation Results**

4GB DDR4 Memory : Q3 2019

Qormino Solution : H1 2019

## Teledyne e2v Space Microprocessors COTS+ Radiation Tolerant Portfolio

Page 24

### **ORGANIC** package solutions

Ruggedized radiation tolerant technology Standard plastic package Device selection and lot validation

### **CERAMIC Non-Hermetic FlipChip**

Ruggedized radiation tolerant technology Advanced packaging on ceramic Standardized quality grade

**TBD**

## Teledyne e2v Space Processors Conclusions

- Supplier of Advanced & Powerful Space Microprocessors

- GHz+ class processors for Compute intensive applications

- Complementing Worldwide Space Offering

- Space Microprocessor Portolio with Flight Heritage

- Existing, mature, proven COTS H/W platforms & Strongest S/W ecosystem in Avionics & Space

Mastering Radiation Tolerant Space Qualification Flows

De-Risking the Introducing of ARM Cortex A72 based Solutions