## Advanced Verification for FPGAs

Simone Catenacci

Application Engineer IC Verification Solutions

April 9, 2018

- Industry Trends and Challenges for FPGA Development

- Staying competitive with Advanced Verification

- Final Thoughts

## INDUSTRY TRENDS AND CHALLENGES FOR FPGA DEVELOPMENT

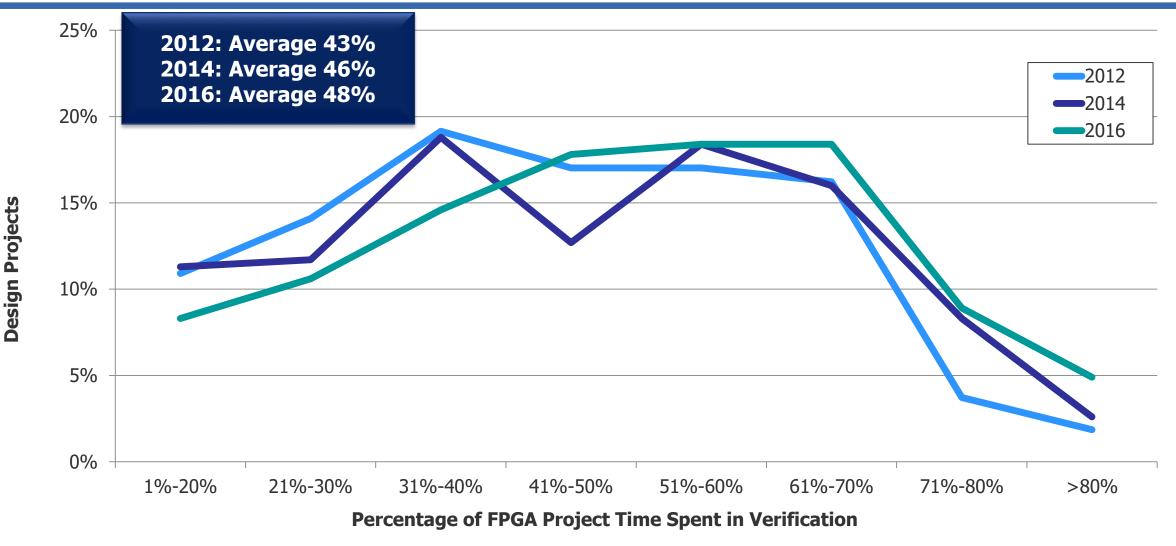

## **FPGA Verification Project Time**

FPGA verification consumes majority of project time

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

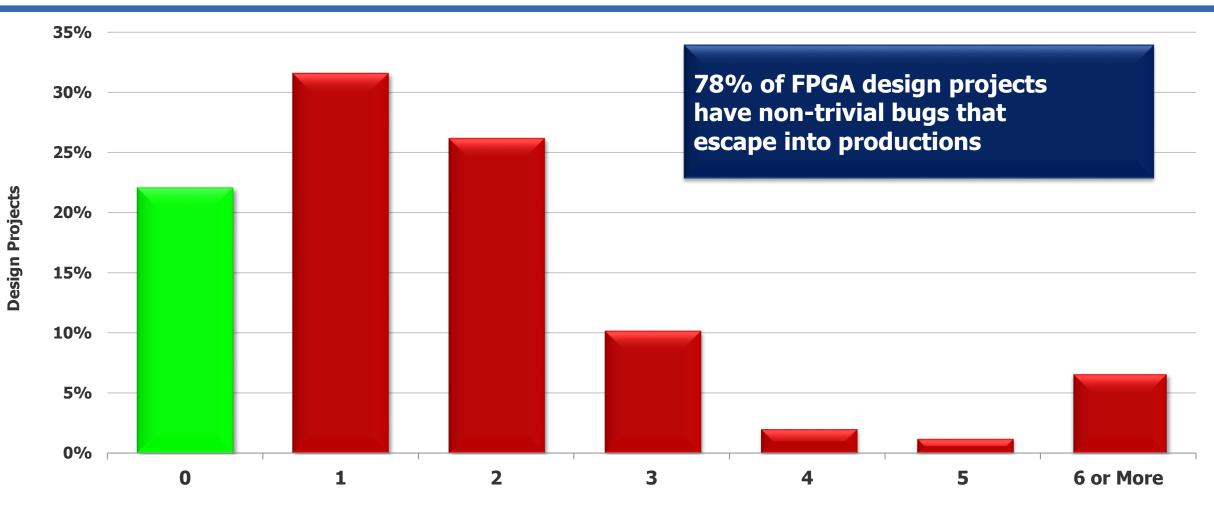

#### **Number of FPGA Bug Escapes to Production**

Bugs found late in the development cycle are exponentially more expensive

#### **2016 FPGA Non-Trivial Bug Escapes to Production**

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

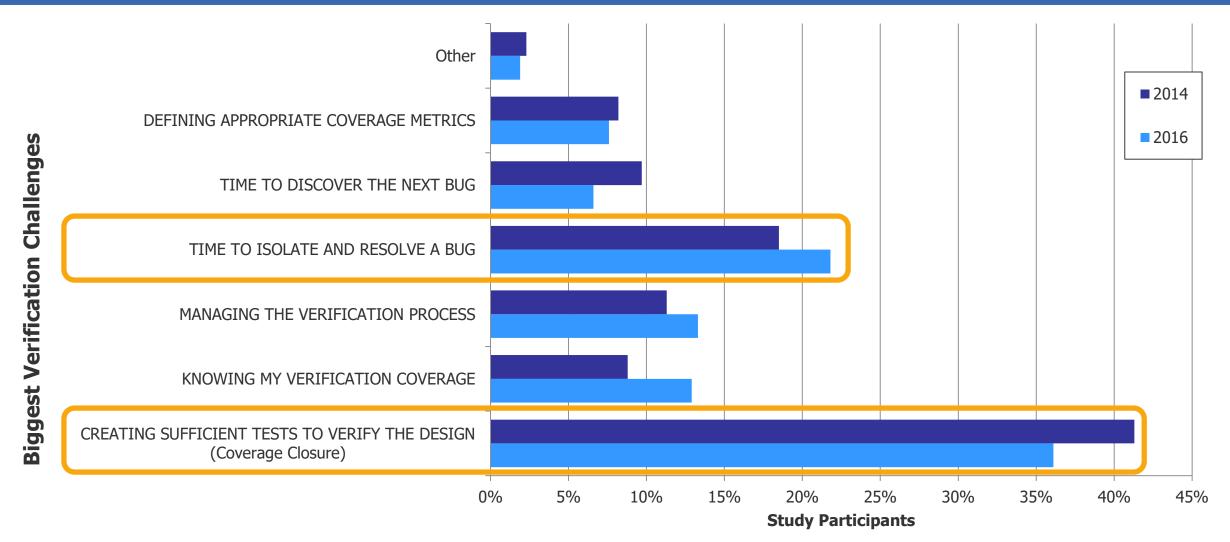

#### **Biggest FPGA Verification Challenges**

Sufficient testing and improving debug efficiency are the biggest challenges

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

Copyright C 2018 Mentor, A Siemens Business All Rights Reserved

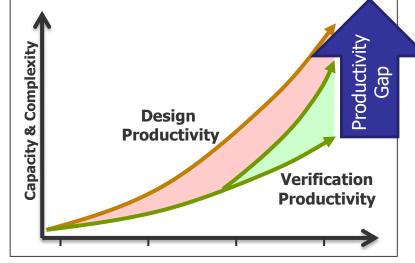

## **FPGA Productivity Gap**

Verification must evolve to keep pace with design innovations

- FPGA vendors continue with design innovations

- Hardened blocks Reuse 🚳

- IP Reuse 🤷

- SOC Reuse 🛛 🐯

- Graphical system builders Automation

- HLS Abstraction

- "Design Productivity" alone ≠ faster "Time to Market"

- Designs must also work and be of high quality to gain adoption

- TTM depends on maximizing design and verification productivity

- Verification must similarly evolve to keep pace

- Maximize reuse 🥸

- Improve automation

- Raise the level of abstraction

## STAYING COMPETITIVE WITH ADVANCED VERIFICATION

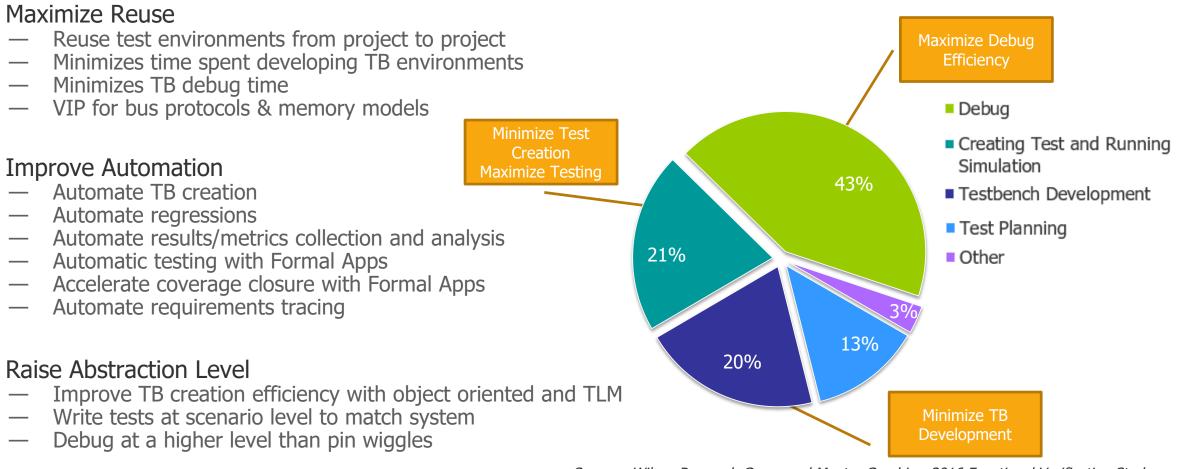

## How Do You Improve Verification Productivity?

Reuse, automation and abstraction to the rescue

#### Where do spend your time for FPGA verification?

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

200

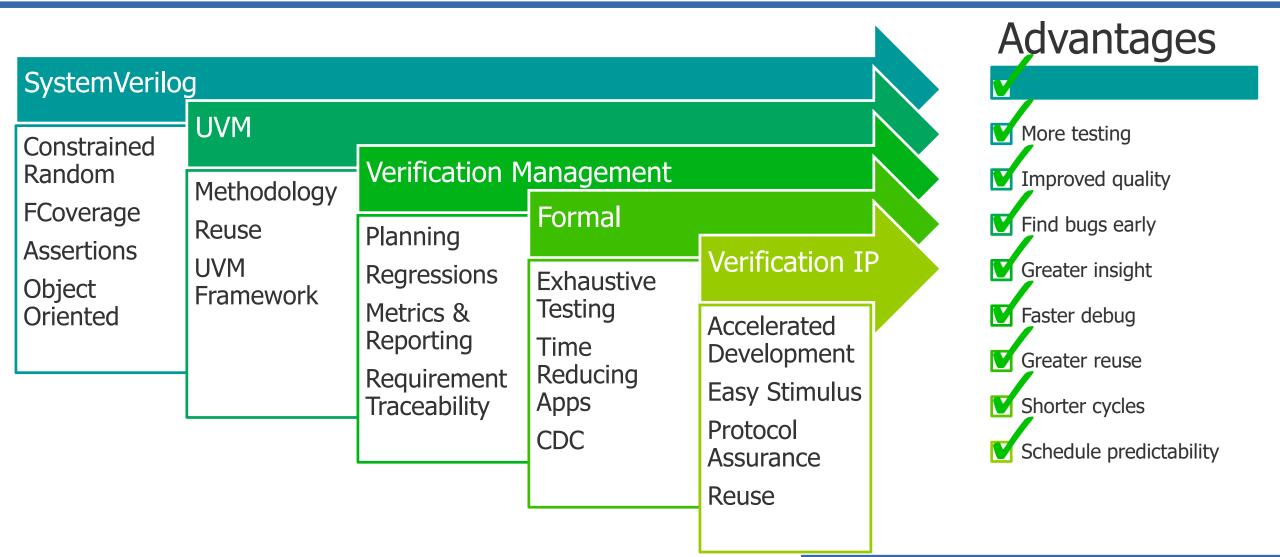

## **Improving with Advanced Verification**

From the lab to the modern age for better quality and productivity

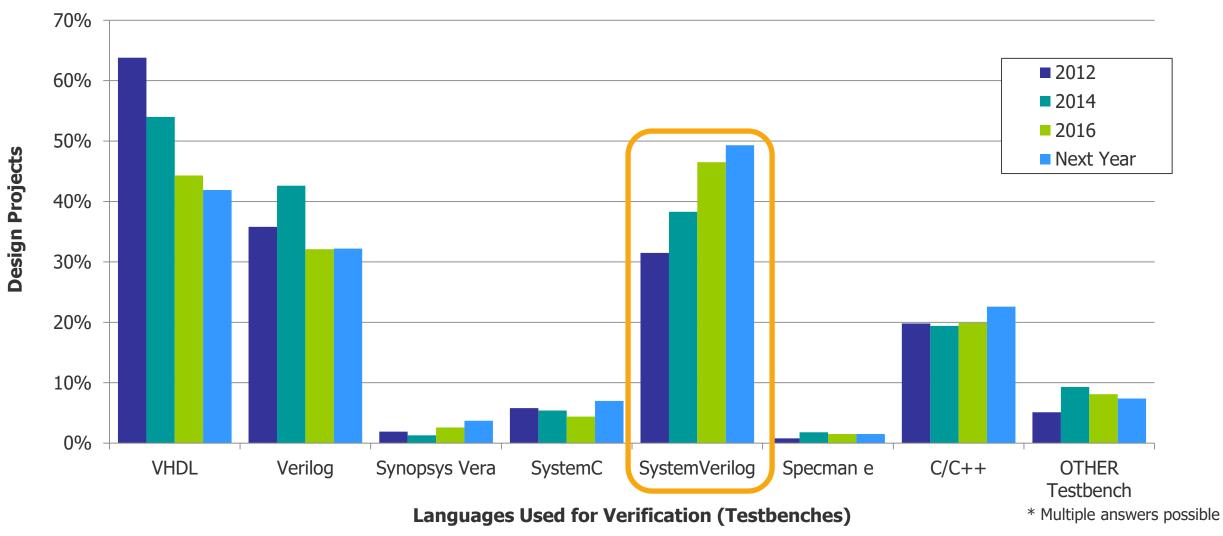

#### **FPGA Verification Language Adoption Trends**

SystemVerilog is now the leading FPGA verification language

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

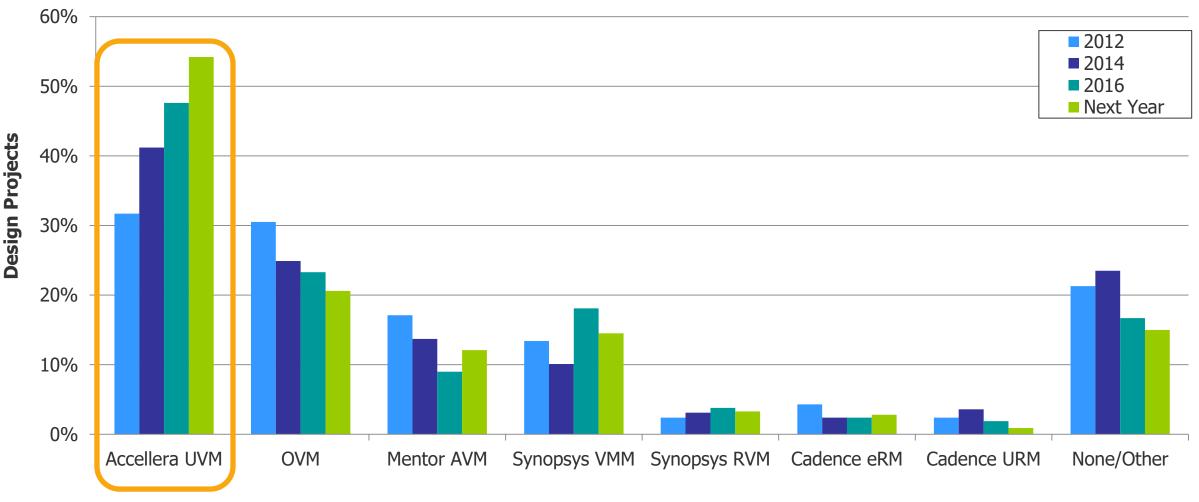

#### **FPGA Testbench Methodology Adoption Trends**

UVM is the clear leader in FPGA testbench methodologies

#### **FPGA Methodologies and Testbench Base-Class Libraries**

\* Multiple answers possible

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

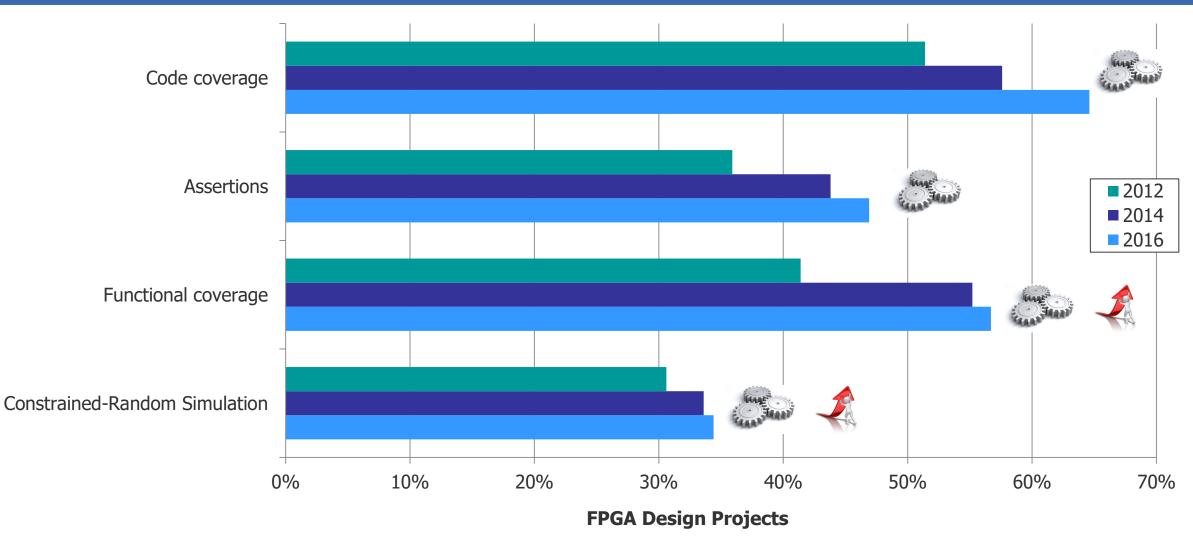

#### **FPGA Dynamic Verification Adoption Trends**

Adoption of advanced verification techniques continue to grow for FPGA verification

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

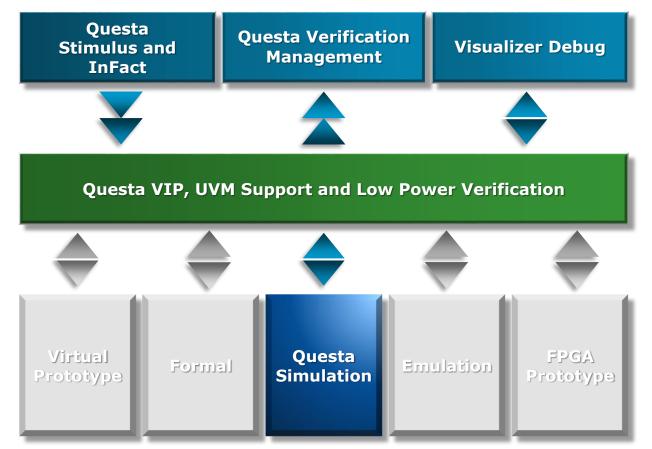

## **Questa Simulation**

Verification Productivity with High Performance Simulation at its Core

- Complete Solution with Mentor Enterprise Verification Platform

- Most Comprehensive Support of Methodologies for Increased Verification Productivity

- Assertion-Based Verification

- SV-UVM

- Coverage/Plan Driven Verification

- Regression Creation and Management

- Test Bench Automation

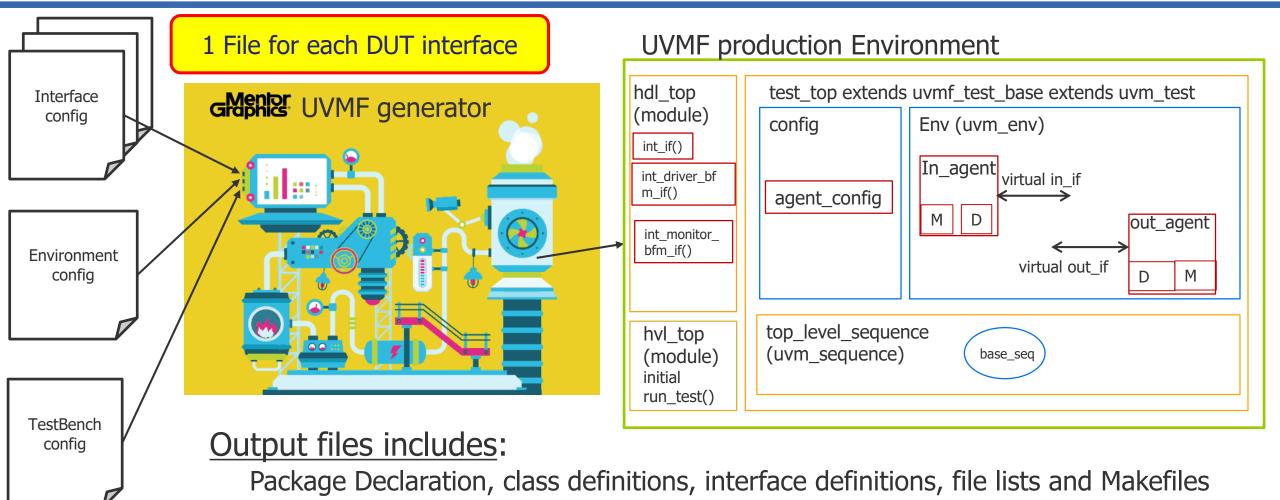

## Mentor UVM Framework (UVMF) for Easier UVM

Making the transition to UVM possible

#### UVM Jumpstart

• Immediately productive while learning UVM

- Layer on top of UVM that hides UVM details

- Allows team to focus on verifying product features

- Promotes reuse increasing productivity

#### UVM Testbench Generators

Code generators to create a UVM testbench in minutes

Saves 3-4 weeks of effort on every project

UVMF is open source and no cost – Delivered in Questa

#### Helped over 40 companies adopt UVM

- 75% are FPGA customers

- Over half are in mil-aero industry

- Majority use VHDL for design and have no SystemVerilog experience

#### **UVMF-Generator Flow**

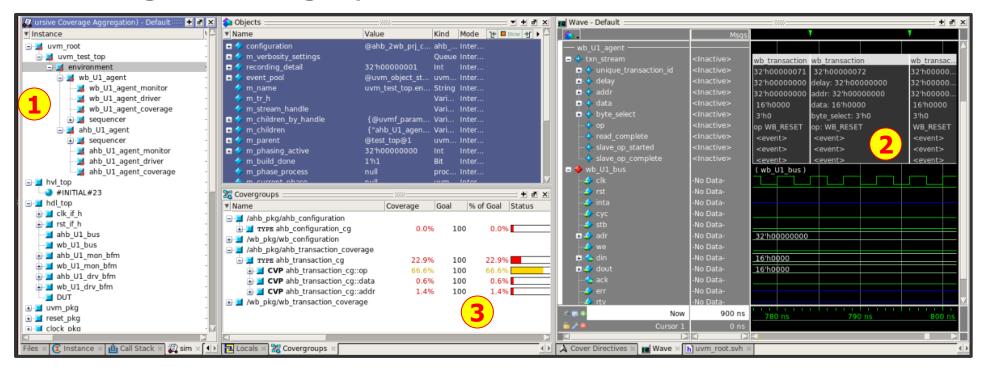

## **Working Simulation Out Of The Box**

#### • 'make debug' to bring up interactive simulation

- 1. Complete Dual Top UVM environment compiles & simulates

- 2. Monitor transactions automatically added to the wave window

- 3. Covergroups automatically created and collect coverage

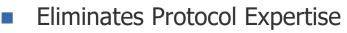

#### **Verification IP Enables Rapid Testbench Development**

Enabling verification of your custom application without deep protocol expertise or effort

<sup>18</sup> SC, Advanced Verification for FPGAs, SEFUW, April 2018

#### **Verification IP: Off The Shelf Protocol Test Environments**

"Protocol Expertise" Reduces Time, Effort & Risk for IP Centric Designs

- What is Verification IP?

- Reusable test environments

- Built around standard protocols

- Reduces Verification Effort

- Provides completed TB at standard interfaces

- Provides functionality to create and run tests

- Less time creating TB and more time testing

- Deep protocol knowledge not needed for TB creation

- Provides out of the box protocol stimulus and checking

- Enhanced debug productivity with transactions and assertions

#### VIP Reduces Risk

- Re-usable VIP building blocks

- Common design architectures & protocols

- Complete protocol assurance

## **A Complete VIP Solution for FPGA Designs**

Mentor Graphics Questa Verification IP Library

| Questa VIP Protocols |                  |                    |               |                  |                  |                   |                      | Questa Memory Library |                 |                     |

|----------------------|------------------|--------------------|---------------|------------------|------------------|-------------------|----------------------|-----------------------|-----------------|---------------------|

| AMBA ®<br>Family     | PCle ®<br>Family | Ethernet<br>Family | USB<br>Family | MIPI ®<br>Family | Serial<br>Family | Display<br>Family | Automotive<br>Family | DRAM<br>Family        | Flash<br>Family | Mil-Aero<br>Family  |

| ACE                  | NVMe             | 200/400G           | 3.1 Pipe      | I3C              | JTAG             | CEC               | CAN                  | LPDDR4                | SDCard 4.2      | Spacewire           |

| AXI4                 | AHCI             | 25/50G             | 3.1 Serial    | UFS              | SmartCard        | HDCP              | CAN-FD               | LPDDR3                | SDIO 4.1        | 1553b               |

| AXI3                 | RMMI             | 100G               | USB PD        | Unipro           | I2C              | HDMI 2.1          | LIN                  | LPDDR2                | eMMc 5.1        | PCI                 |

| AHB5                 | MRIOV            | 40G                | SSIC          | LU               | I3C              | HDMI 1.4          | 5G Family            | DDR4                  | ONFI 4.0        | SRIO<br>AMBA 5      |

| AHB                  | МРНҮ             | 10G                | оНСІ          | CSI-2 / CSI-3    | I2S              | HDMI 1.3          |                      | DDR3                  | Toggle          |                     |

| APB3                 | PCle 4.0         | 2.5/5G             | xHCI          | DSI              | SPI              | DisplayPort       | CPRI                 | DDR2                  | UFS             | CHI 5               |

|                      | PCle 3.1         | 1G                 | МРНҮ          | DigRF            | SPI 4.2          | eDP               | JESD204B             | WIDEIO                | ParalleINOR     | Hyperbus            |

|                      | PCle 2.1         | 100M               | eHCI          | MPHY             | UART             | V-by-One          | Storage              | DFI                   | Serial NOR      | Hyperram            |

|                      | PCle 1.1         | 10M                | USB 3.0       | HSI              |                  |                   | Family               | НМС                   |                 | Hyperflash          |

|                      | PIPE 4.3         | Automotive         | USB 2.0       | СРНҮ             |                  |                   | SATA                 | HBM2                  |                 |                     |

|                      | PIE8             | Interlaken         | USB 1.1       | DPHY             |                  |                   |                      | DIMM                  |                 | NVMe over<br>Fabric |

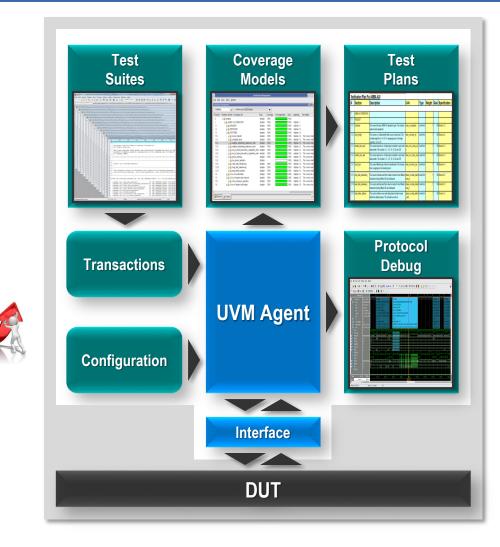

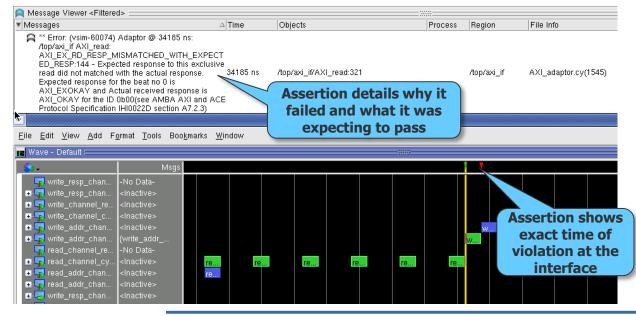

## **Debug Faster with Questa Verification IP**

QVIP Improves debug abstraction and automation to boost productivity

Transaction recording

- Debug at a higher level with integrated transactions

- Quickly understand and analyze bus activity

- Automatically links transactions to signals

Integrated assertions automate protocol checking

Protocol assertions

- Protocol assertions immediately pinpoint source of failure

- Quickly understand integration of your design with IP

Copyright © 2018 Mentor, A Siemens Business All Rights Reserved

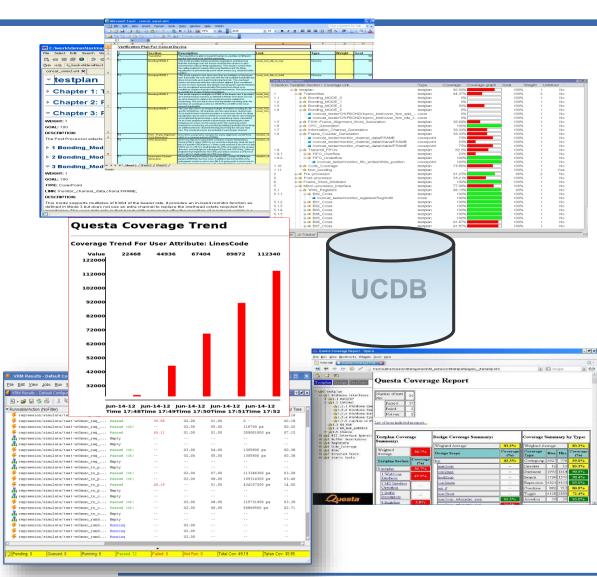

#### **Questa Verification Management**

Productivity in Tool Execution, Data Management, Analysis and Tracking

- Test Plan Tracking

- Lifts the lid on simulation, formal, CDC

- See progress day by day

- Have I done enough testing?

- Am I ready to freeze the RTL?

- Trend Metrics

- Monitor progress throughout the project

- Mitigate verification risks

- Help improve future project timescale estimations

- Results Analysis

- Quickly Identify and Organize Results

- Improve debug turn-around time

- Verification Run Manager

- Automate all regression tasks and reporting

- One interface to control all

Copyright © 2018 Mentor, A Siemens Business All Rights Reserved

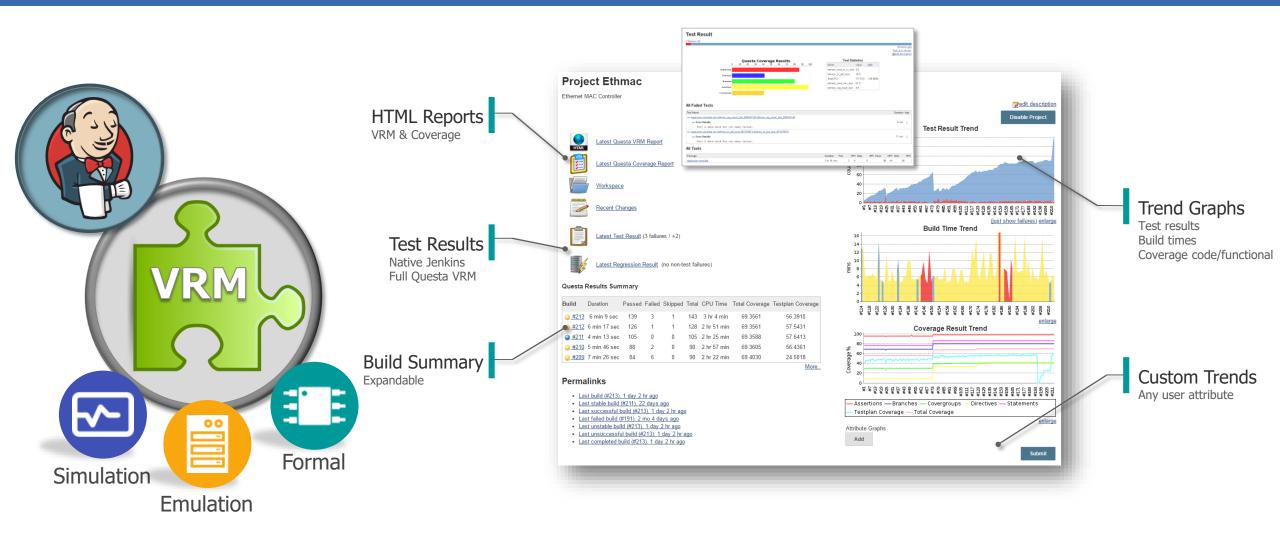

#### **Jenkins & Questa Verification Run Management**

Continuous integration and reporting for advanced regressions management

## FINAL THOUGHTS

#### **Proven Benefits from Advanced Verification**

FPGA customers realize the benefits of evolving their verification methodologies

## SystemVerilog UVM/UVMF

- Constrained random for better testing

- Functional coverage for better insight

- Consistent methodology

- Promotes Reuse

#### Verification IP

Protocol expertiseReduces TB development effortRisk reduction

#### Formal

- Find bugs at design time

- Identify unreachable code

- Exhaustive testing

## FPGA Customer Success Stories

Increased business due to shorter design cycles

400% ROI after adopting UVM and VIP

5 straight FPGA's without a bug

Zero bugs found in lab since moving to UVM

3x Speed up verification cycle with Formal Apps

Higher quality code

#### Where Can You Go To Learn More?

#### Verification Academy

- <u>https://verificationacademy.com/</u>

- Most comprehensive verification resource in industry

- Free online courses, verification cookbooks, discussion forums

- More than 40,000 members

#### Functional Verification at www.mentor.com

- <u>https://www.mentor.com/products/fv/</u>

- Learn more about tools to enable methodologies

- Simulation, SV/UVM, Formal, Verification IP

- Training catalog

- Success Stories

- <u>https://www.mentor.com/products/fv/success/</u>

# A Siemens Business

www.mentor.com