### www.FrontierDevelopmentLab.org

KICK OFF WORKSHOP ESA ESRIN, ROME 25th - 29th June '18

RESEARCH SPRINT

30th June - 17th August

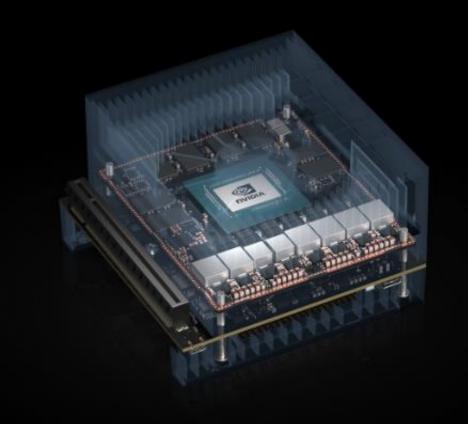

# **TESLA V100 32GB**

5,120 CUDA cores

640 NEW Tensor cores

7.5 FP64 TFLOPS | 15 FP32 TFLOPS

### 120 Tensor TFLOP

20MB SM RF | 16MB Cache | 32GB HBM2 @ 900 GB/s 300 GB/s NVLink

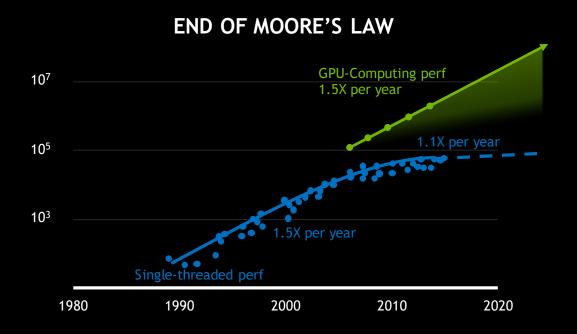

### THE RISE OF GPU COMPUTING

### Big Data Needs Algorithms and Compute That Scales

CPU vs. GPU

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten Newplot and data collected for 2010-2015 by K. Rupp

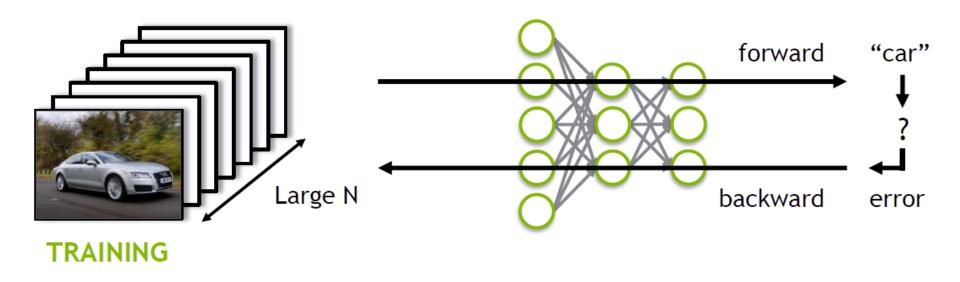

### TRAINING VS INFERENCE

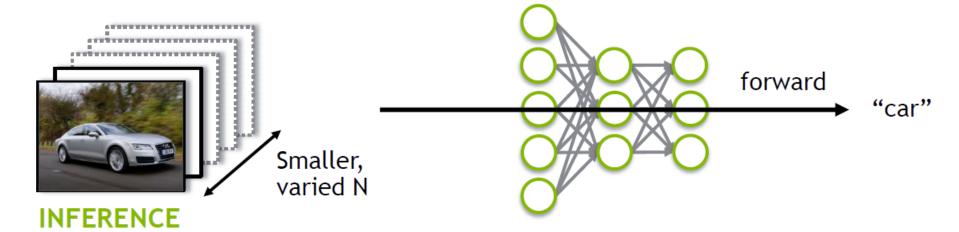

### **ROBOTS**

# **NVIDIA RESEARCH**

**NVIDIA** Research Al Autoencoder

NVIDIA Research / Remedy

**NVIDIA Research** Audio-driven Facial Animation Semantic Manipulation with GANs

**NVIDIA** Research Progressive GAN

NVIDIA Research / AIVA RNNs for Music

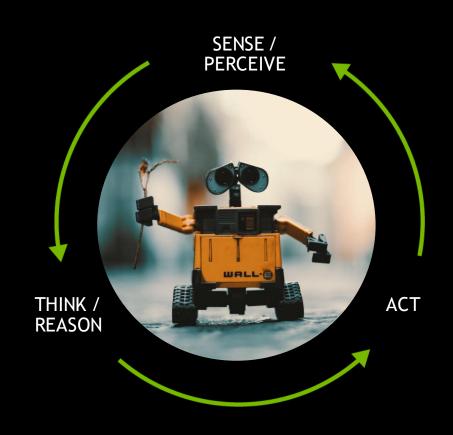

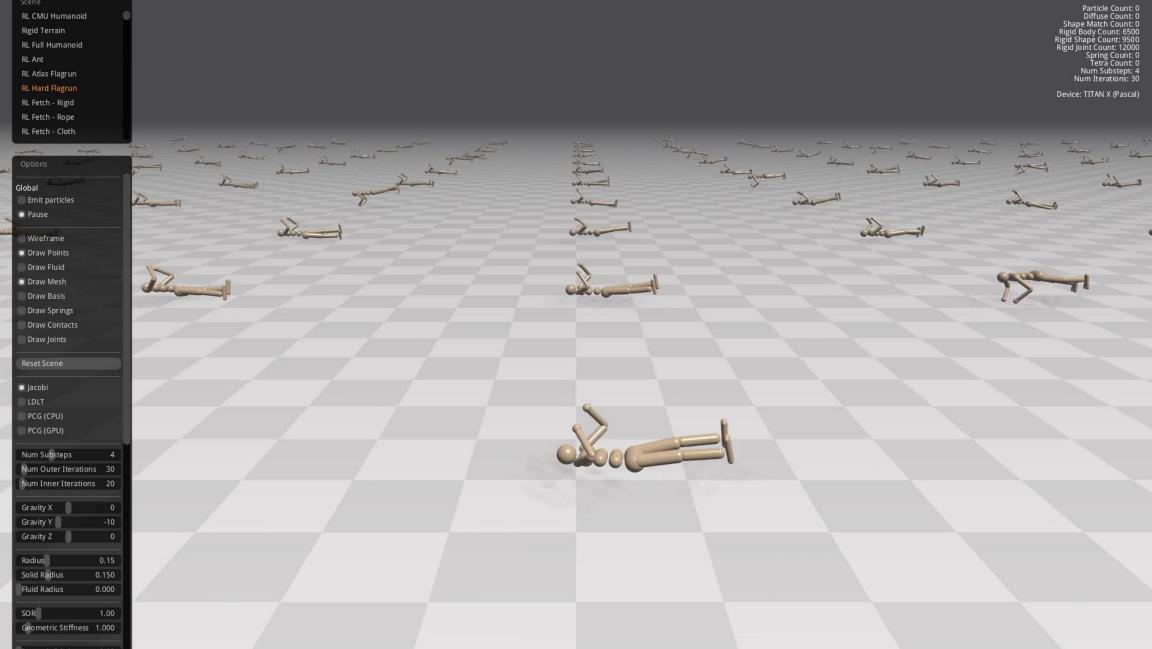

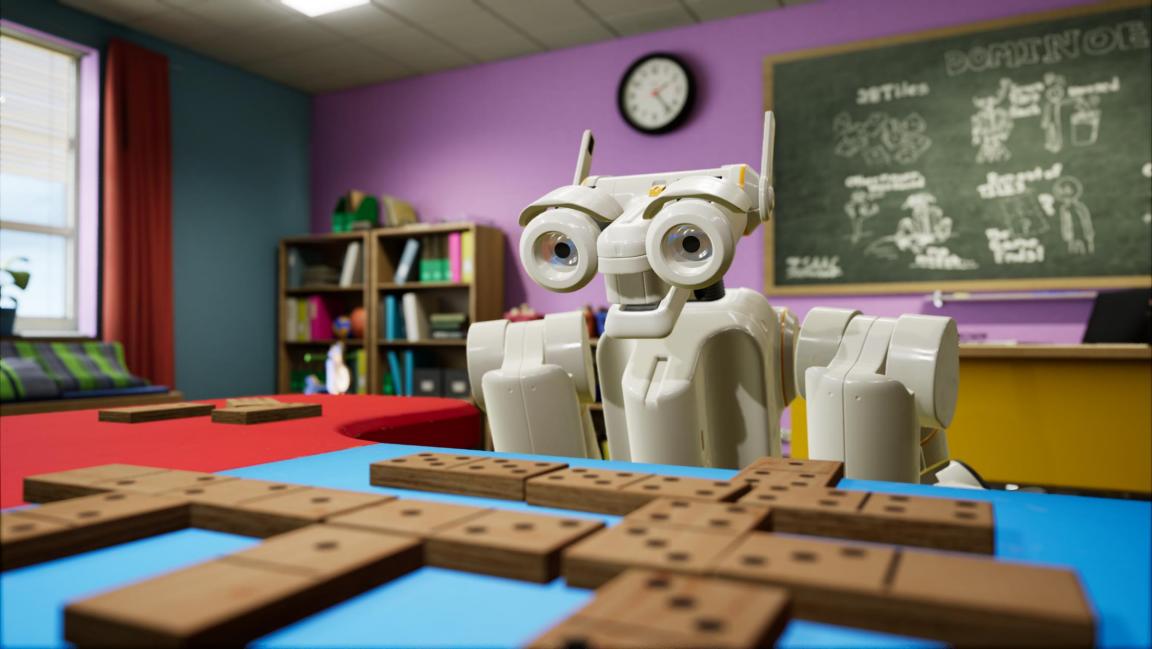

### **ISAAC**

### **Simulate**

### **Develop**

**Deploy**

World model Warehouse · Office

· Store · Home

Robot model Carter · URDF loader

### **Simulation Engine**

Photo-realistic Graphics · Physics · Soft bodies · · Procedural Generation · Massive parallelism

Virtual Sensors

Virtual Actuators

Navigation

Behaviors

Perception

Isaac Framework

Manipulation

Interactions

with humans

#### **Drivers**

Lidar · Camera · IMU · Robot Base · ...

**Jetson**

Fully integrated with X2 and Xavier

Codelets · Behaviors · 3D Poses · Distributed · Messaging · Synchronization · Record & Replay Unreal Engine 4 / Unity 3D · Configuration · Visualization

Sensor Processing

ML

TensorRT · CUDA

· Tensorflow · ...

**Actuator Control**

Gems

Optimizers · Algebra

· EKFs · Depth · ...

#### **Unified Message API**

Use the same messages for simulation, actual hardware and across all apps

**HW Sensor**

**HW Actuator**

12 **NVIDIA**

### CUDA DEVELOPMENT ECOSYSTEM

**GPU Users**

Domain **Specialists**

Problem **Specialists**  New Algorithm Developers and **Optimization Experts**

**Applications**

**Frameworks**

Libraries

Directives and **Standard Languages**

Languages

Ease of use

Specialized Performance -

CUDA: Programming Model, GPU Architecture, System Architecture

### **CUDA 10 - TURING**

Inference Accelerated, Graphics Reinvented, Volta's Programmability

### NVIDIA DEEP LEARNING SDK UPDATE

# GPU-accelerated DL Primitives

cuDNN 7.3

Support for Turing

Optimizations for RNNs

Leading frameworks support

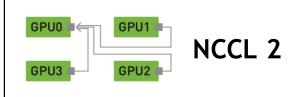

# Multi-GPU & Multi-node

Multi-node distributed training (multiple machines)

Leading frameworks support

# High-performance Inference Engine

TensorRT 5

TensorFlow model reader

Object detection

**INT8 RNNs support**

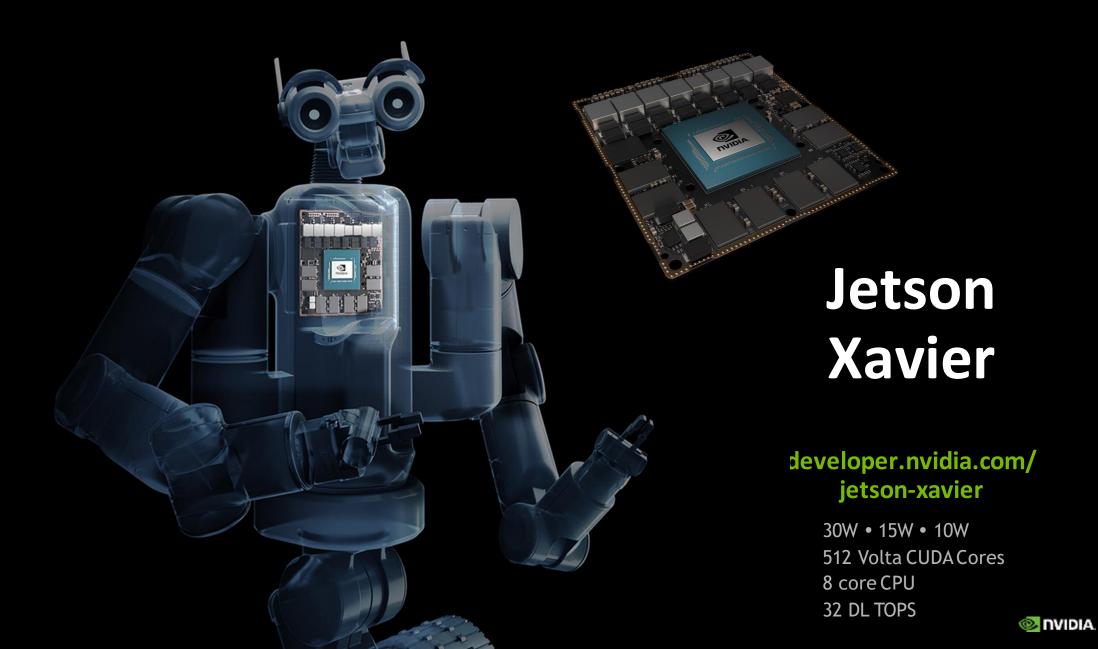

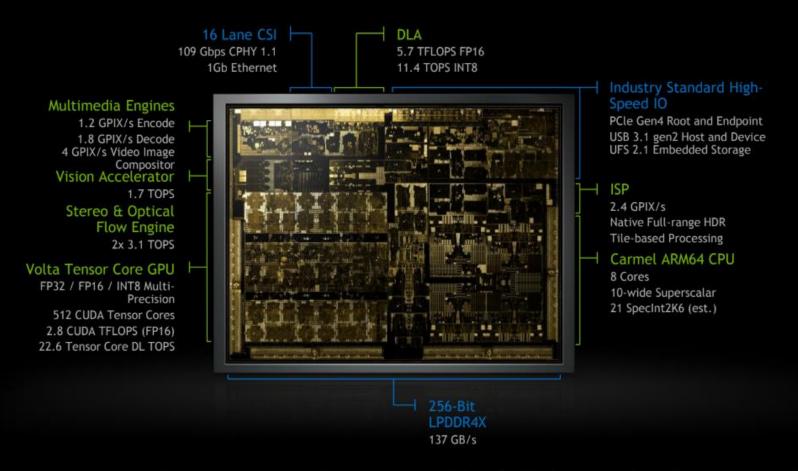

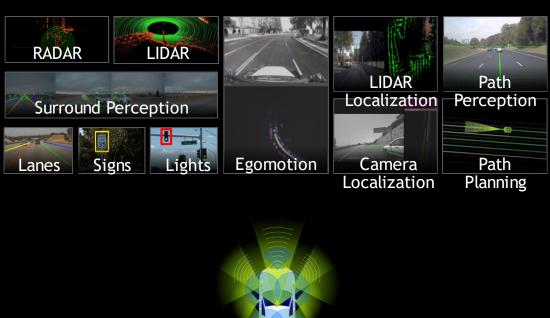

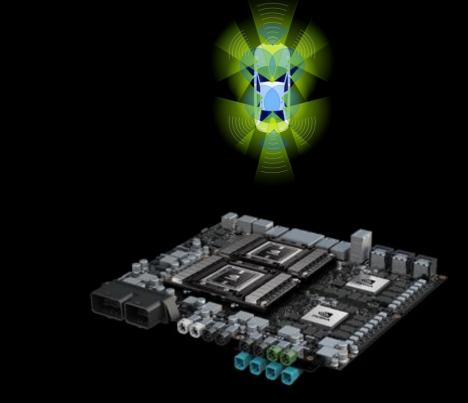

### **XAVIER**

### World's First Autonomous Machines Processor

Most Complex SOC Ever Made | 9 Billion Transistors, 350mm<sup>2</sup>, 12FFN | ~8,000 Engineering Years

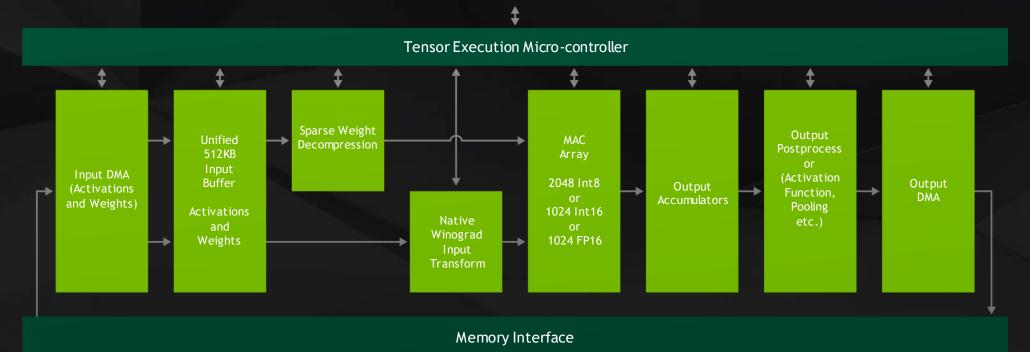

# XAVIER DLA NOW OPEN SOURCE

Command Interface

WWW.NVDLA.ORG

# JETSON XAVIER DEVELOPER KIT

\$1299 (pre-order only)

Available from distributors WW

Early access August 2018

# JETSON XAVIER DEVELOPER KIT

### TensorRT SUPPORTS Xavier

Optimized Inference on the World's Most Powerful SoC

Deploy deep learning inference on Xavier platforms through NVIDIA DRIVE AI Platforms

Import models in any framework (including TensorFlow, Caffe and Torch) through ONNX, Universal Framework Format or custom C/C++ API

Optimize CNN, RNN and novel neural network layers and deploy reduced precision on Tensor Cores

Download for development or host environment today

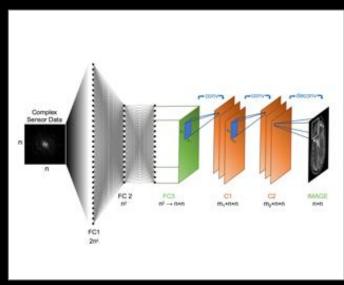

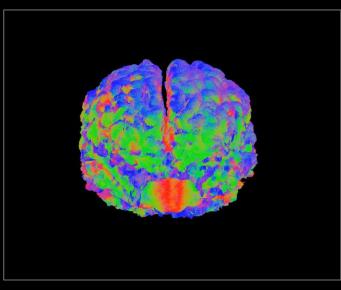

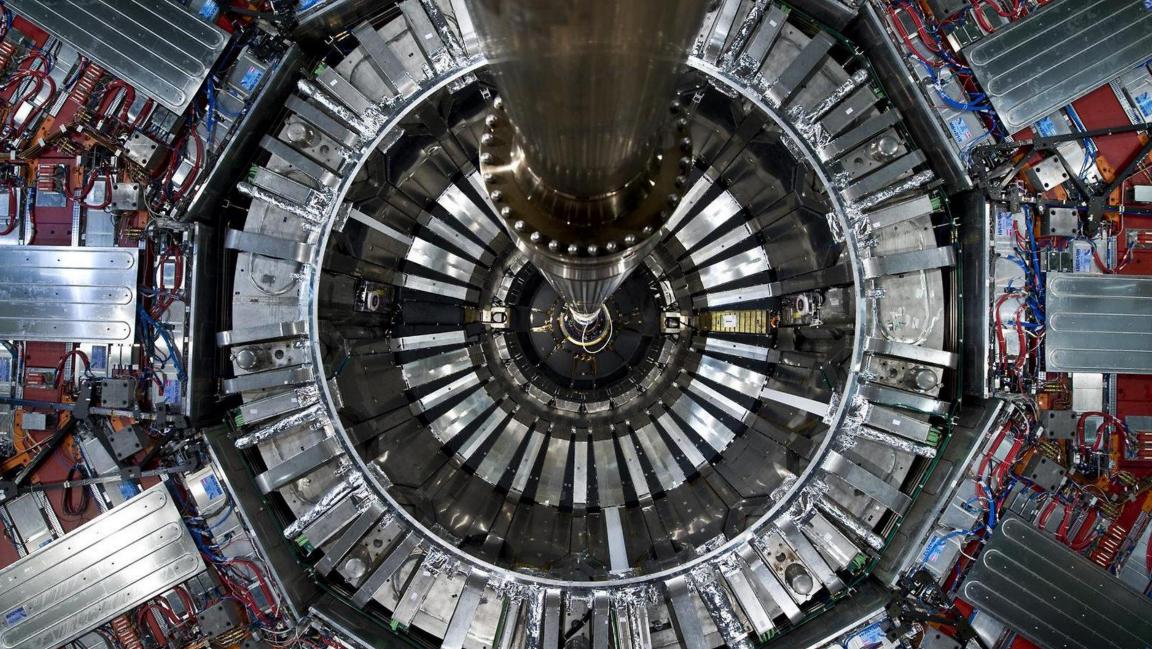

# AI IS THE FUTURE OF INTELLIGENT INSTRUMENTS

**AUTOMAP RECONSTRUCTION**

Source: https://arxiv.org/pdf/1704.08841.pdf

**ANATOMY DETECTION**

Source: GE Healthcare

INTELLIGENT RENDERING

Source: GE Healthcare

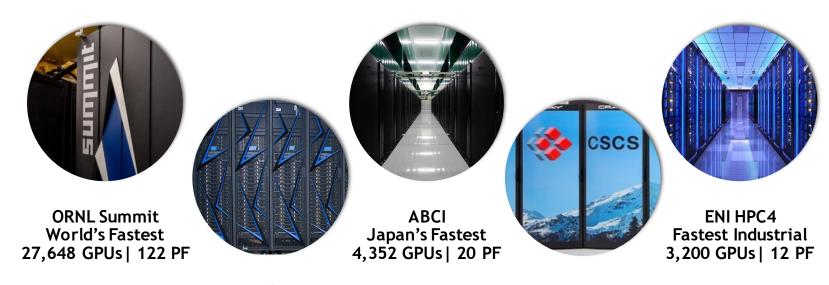

# NVIDIA POWERS FASTEST SUPERCOMPUTERS IN US, EUROPE, JAPAN, INDUSTRY

17 of World's 20 Most Energy-efficient Supercomputers

LLNL Sierra US 2<sup>nd</sup> Fastest 17,280 GPUs | 72 PF Piz Daint Europe's Fastest 5,320 GPUs | 20 PF

#### **NVIDIA SDK**

The Essential Resource for GPU Developers

#### **NVIDIA SDK**

### developer.nvidia.com

# DEEP LEARNING Deep Learning SDK High-performance tools and libraries for deep learning

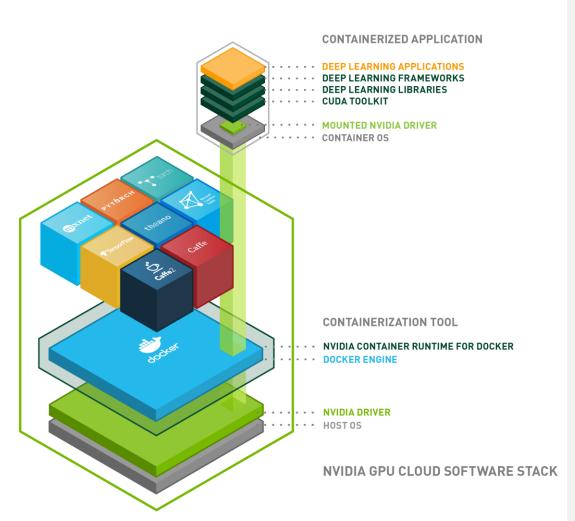

### WHY CONTAINERS?

### **Benefits of Containers:**

Simplify deployment of GPU-accelerated software, eliminating time-consuming software integration work

Isolate individual deep learning frameworks and applications

Share, collaborate, and test applications across different environments

To learn more:

nvidia.com/ngc

To sign up:

ngc.nvidia.com

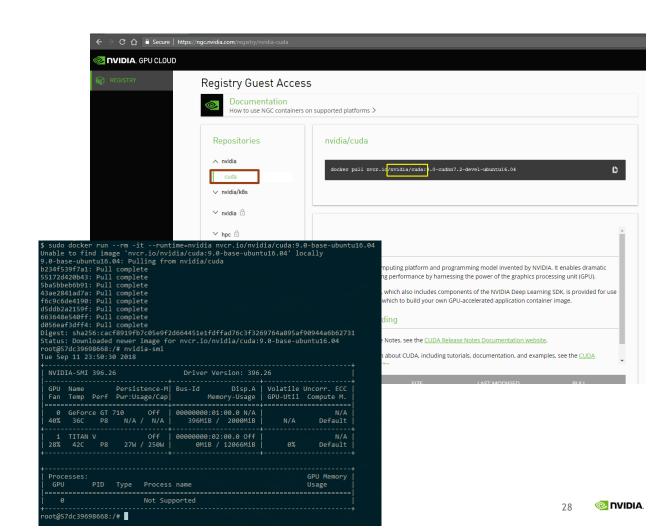

### CUDA CONTAINERS ON NVIDIA GPU CLOUD

CUDA containers available from NGC Registry at nvcr.io/nvidia/cuda

Three different flavors:

#### **Base**

Contains the minimum components required to run CUDA applications

#### **Runtime**

Contains base + CUDA libraries (e.g. cuBLAS, cuFFT)

#### Devel

Contains runtime + CUDA command line developer tools. Some devel tags also include cuDNN

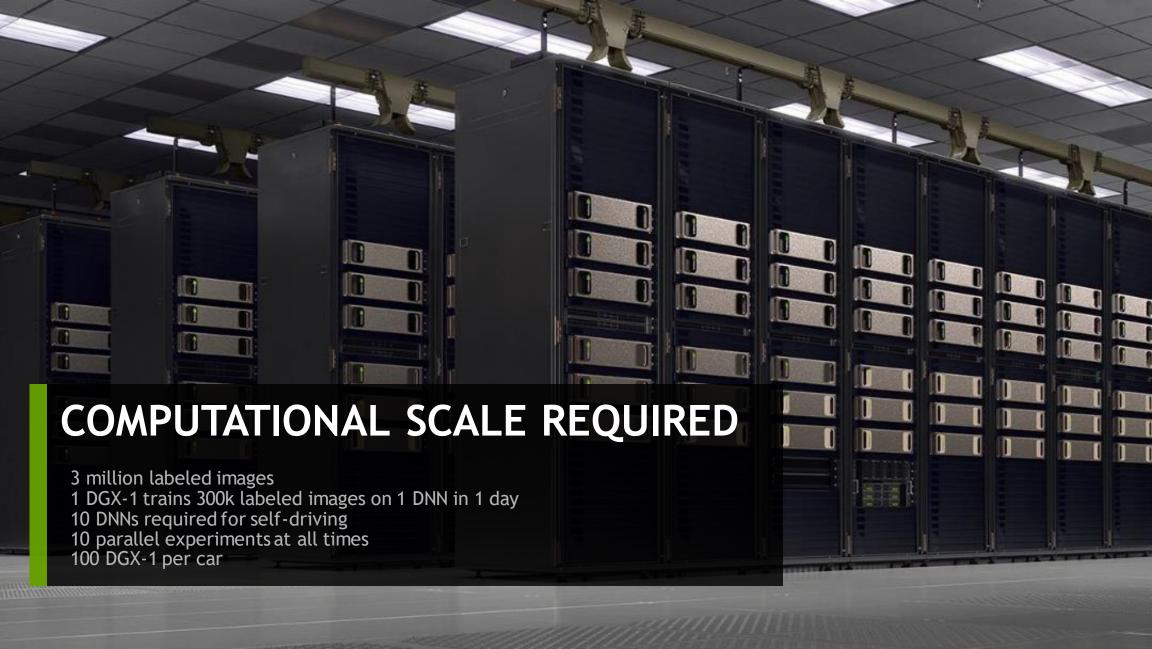

# DGX POD ARCHITECTURE

a single data center rack containing up to 9x NVIDIA DGX-1 servers, storage, networking & NVIDIA AI software

Nine DGX-1 servers

12 storage servers

10 GbE (min) storage & management switch

Mellanox 100 Gpps intra-rack high speed network switches.

# **NVIDIA DGX-2**

### THE LARGEST GPU EVER CREATED

# **NEXT STEPS**

GTC Munich | October 9-11 2018 www.nvidia.com/en-eu/gtc/ 25% discount: NVALOWNDES

NVIDIA Deep Learning Institute www.nvidia.com/en-us/deep-learning-ai/education

NGC www.nvidia.com/en-us/gpu-cloud

### the esa earth observation φ-week

EO Open Science and FutureEO

12-16 November 2018 | ESA-ESRIN | Frascati (Rome), Italy