# **STAR-Dundee**

20 Years of Spacecraft Networking Innovation

# SpaceFibre IP Cores for the Next Generation of Radiation-Tolerant FPGAs

Alberto Gonzalez Villafranca, Albert Ferrer Florit, Marti Farras Casas, Steve Parkes

www.star-dundee.com @STAR\_Dundee

#### **Introduction - SpaceFibre**

Spacecraft Networking Innovation

- Compatible with SpaceWire packet and network level

- Because it transfers SpaceWire packets

- Supports any packet length

- Provides data integrity and reliable data delivery

- Automatically recovers from transient errors in less than 2 µs

- Lane is automatically reinitialised if BER is worse than 10<sup>-5</sup>

- Multiple concurrent data flows over the same link with QoS

- VCs have priority, bandwidth allocation and scheduling QoS

- Low latency broadcast messages (< 1 µs)

- Broadcasted to all nodes in a network

- Guaranteed that same message is not received twice

- Multi-lane capabilities

- Arbitrary number of lanes with graceful degradation when a lane fails.

- Warm redundancy recovers from a lane failure in less than 80 µs

- Hot redundancy recovers from a lane failure in less than 3 µs

#### New Generation FPGAs for Space

- Microchip RTG4

- 65 nm

- Flash-based Non-volatile

- Radiation-hardened by design

- 24x SerDes @ 3.125 Gbit/s

- Xilinx Kintex UltraScale

- 20 nm

- SRAM-based Volatile

- Radiation-tolerant

- 32x SerDes @ 12.5 Gbit/s

# New Generation FPGAs for Space

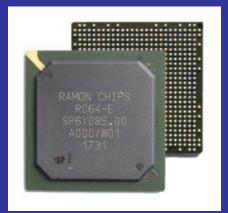

- NanoXplore BRAVE family (NG-Large / NG-Ultra)

- 65 / 28 nm FD-SOI

- SRAM-based Volatile

- Radiation-hardened by design

- 4x SerDes @ 6 Gbit/s / 32x SerDes @ 12.5 Gbit/s

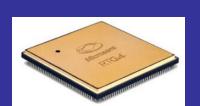

- Microchip RTG4

- 65 nm

- Flash-based Non-volatile

- <u>Radiation-hardened</u> by design Radiation-tolerant

- 24x SerDes @ 3.125 Gbit/s

- Xilinx Kintex UltraScale

- 20 nm

- SRAM-based Volatile

- Radiation-tolerant

- 32x SerDes @ 12.5 Gbit/s

- Microchip PolarFire

- 28 nm

- SONOS-based Non-volatile

- 24x SerDes @ 10 Gbit/s

- Xilinx Versal

- 7 nm FinFET

- SRAM-based Volatile

- Radiation-tolerant

- 44x SerDes @ 25 Gbit/s

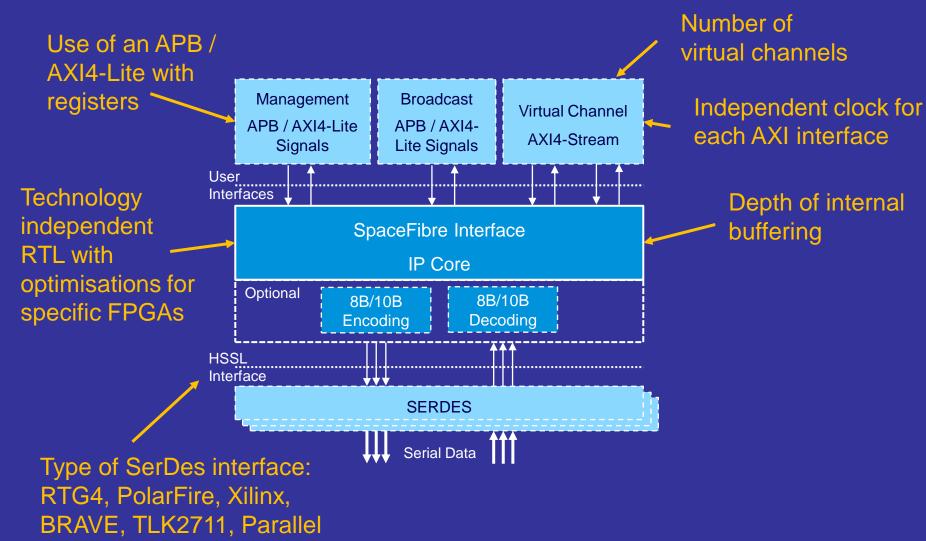

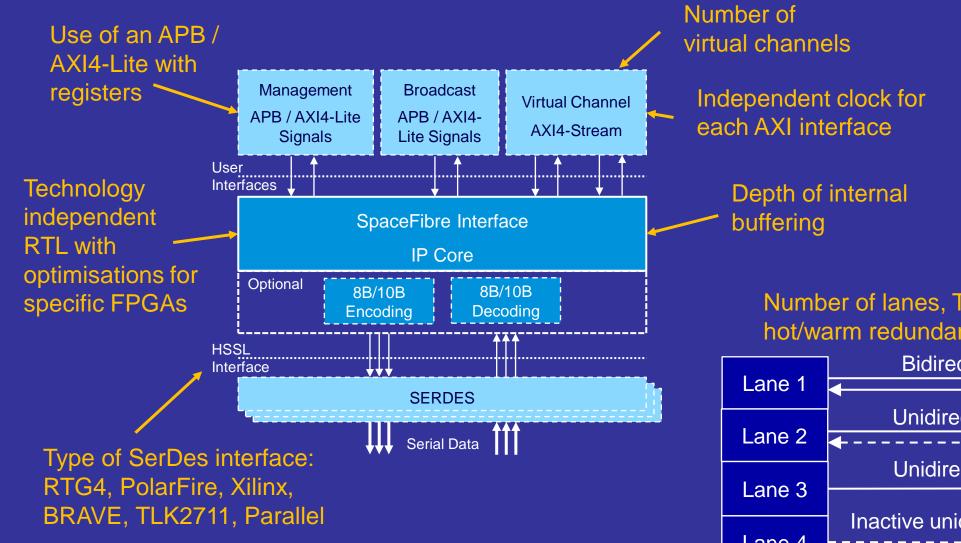

# SpaceFibre IP Cores General Features

- Configurable

- Number of lanes, virtual channels, ports

- Type of SerDes and configuration interface

- High performance

- Optimised for radiation hardened FPGAs

- Low latency

- Easy to use

- AXI4-Stream interface for each VC

- Reference designs for RTG4, PolarFire, KUS, Versal, BRAVE...

- ASIC-ready

#### Safe

- Extensive verification and validation

- Tested in radiation environment

## SpaceFibre IP Cores General Features

- Use of EDAC protection in memories

- Guaranteed, straightforward, timing closure

- Lane rate only limited by Serdes (e.g. up to 3.125 Gbps on RTG4)

- For the whole temperature and voltage range (i.e. fast & slow corners)

- With EDAC and SET filters

- Does not require specific placement or timing constraints.

- Even with more than 80% FPGA utilisation

- Low latency

- Less than 400 ns for Broadcasts (including 250ns due to SerDes latency)

- Streaming frame sending option

- Compact design

#### SpaceFibre IP Interfaces

#### SpaceFibre IP Interfaces

Number of lanes, Tx/Rx unidirectional lanes, hot/warm redundancy

# SpaceFibre IP @ BRAVE

20 Years of Spacecraft Networking Innovation

STAR-Dundee

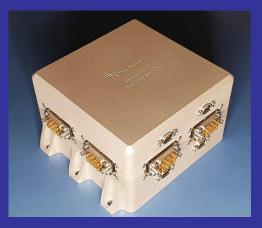

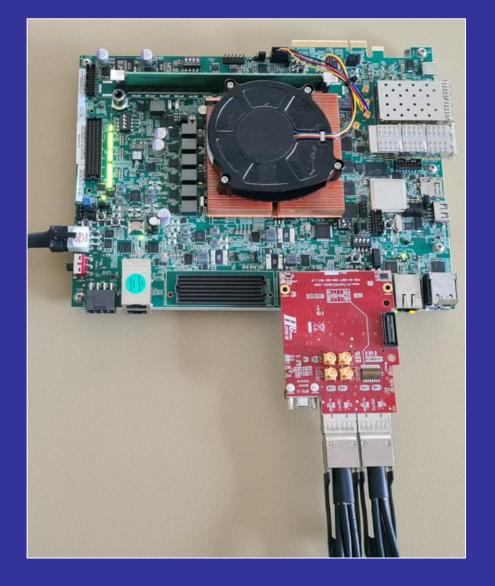

- Successful link connection established with STAR-Fire unit

- Correct data transmission <u>without any</u> <u>data errors</u>

- Retry events periodically appear  $\overline{\mathfrak{S}}$

- Currently debugging this problem in collaboration with NanoXplore

- The final validation of the IP to be completed soon

- Reference design with SerDes configuration, clock scheme details, memory instantiation (EDAC), etc. provided with IP

# SpaceFibre Single-Lane Interface IP Resources

|     |      | RTG4 | 4     | XQRKU060 * |      |        |

|-----|------|------|-------|------------|------|--------|

|     | LUT  | DFF  | LSRAM | LUT        | DFF  | RAMB36 |

| 1   | 3316 | 2365 | 4     | 1823       | 2346 | 4      |

| VC  | 2.2% | 1.6% | 1.9%  | 0.5%       | 0.4% | 0.4%   |

| 2   | 3960 | 2946 | 6     | 2162       | 2969 | 6      |

| VCs | 2.6% | 1.9% | 2.9%  | 0.7%       | 0.4% | 0.6%   |

| 4   | 5389 | 4114 | 10    | 2960       | 4214 | 10     |

| VCs | 3.5% | 2.7% | 4.8%  | 0.9%       | 0.6% | 0.9%   |

|     | H    | RTPF50 | 0T *  | X    | QRVC1902 * |        |  |

|-----|------|--------|-------|------|------------|--------|--|

|     | LUT  | DFF    | LSRAM | LUT  | DFF        | RAMB36 |  |

| 1   | 2796 | 2226   | 8     | 1687 | 2272       | 2      |  |

| VC  | 0.6% | 0.5%   | 0.5%  | 0.2% | 0.1%       | 0.2%   |  |

| 2   | 3400 | 2801   | 12    | 1985 | 2824       | 3      |  |

| VCs | 0.7% | 0.6%   | 0.8%  | 0.2% | 0.2%       | 0.3%   |  |

| 4   | 4653 | 3972   | 20    | 2796 | 3923       | 5      |  |

| VCs | 1.0% | 0.8%   | 1.3%  | 0.3% | 0.2%       | 0.5%   |  |

#### SpaceFibre Single-Lane Interface IP Resources

- TMR in PolarFire

- DFF ~ x 2.8

- LUT ~ x 2

## SpaceFibre Single-Lane Interface IP Resources

- NG family share the same type of fabric resources

- IP implementation expected to use the same resources in NG-Large and NG-Ultra

- In terms of % of resource usage for the SpFi IP Core

- NG-Large is equivalent to the RTG4

- NG-Ultra is equivalent to the PolarFire

|     | Ν    | NG-Larg | ge    | NG-Ultra |      |      |

|-----|------|---------|-------|----------|------|------|

|     | LUT  | DFF     | RAM   | LUT      | DFF  | RAM  |

| 1   | 2703 | 2496    | 8     | 2703     | 2496 | 8    |

| VC  | 2.0% | 1.9%    | 4.2%  | 0.5%     | 0.5% | 1.2% |

| 2   | 3275 | 3068    | 12    | 3275     | 3068 | 12   |

| VCs | 2.4% | 2.4%    | 6.3%  | 0.6%     | 0.6% | 1.8% |

| 4   | 4350 | 4220    | 20    | 4350     | 4220 | 20   |

| VCs | 3.2% | 3.3%    | 10.4% | 0.8%     | 0.8% | 3.0% |

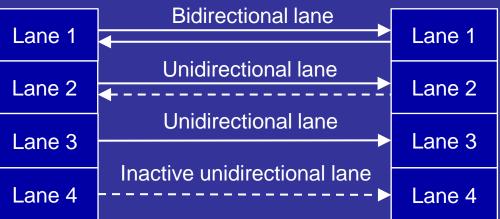

## SpaceFibre Multi-Lane Interface IP Core

- Multi-Lane is an optional capability of the SpFi standard

- Allows several physical lanes to behave as a single logical link

- Higher throughput

- Redundancy

- Hot (< 3 μs) & Warm (< 80 μs)</p>

- Lanes can be operated independently

- Any number of lanes supported

- Unidirectional lanes supported

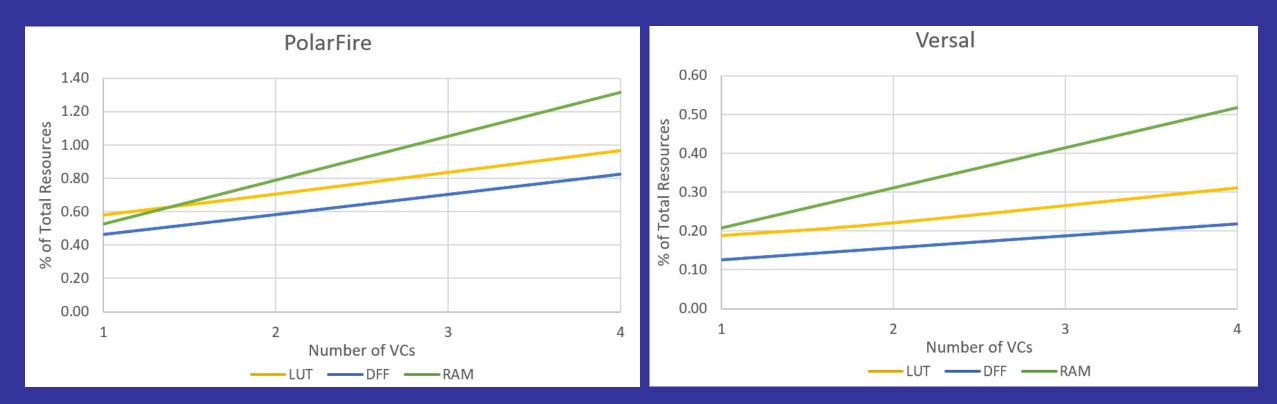

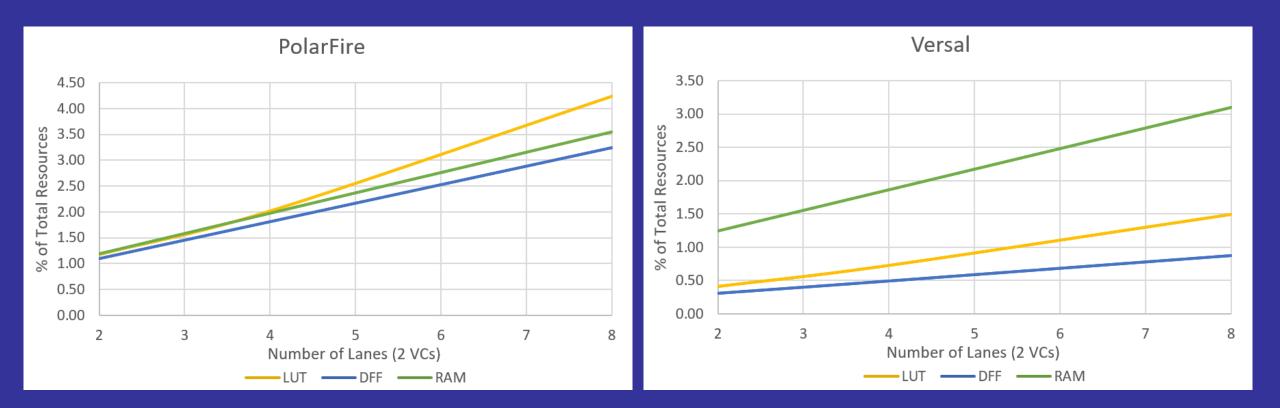

#### SpaceFibre Multi-Lane Interface IP Resources

Values for different configurations (2/4/8 Lanes and 1/2/4 VCs) available the paper

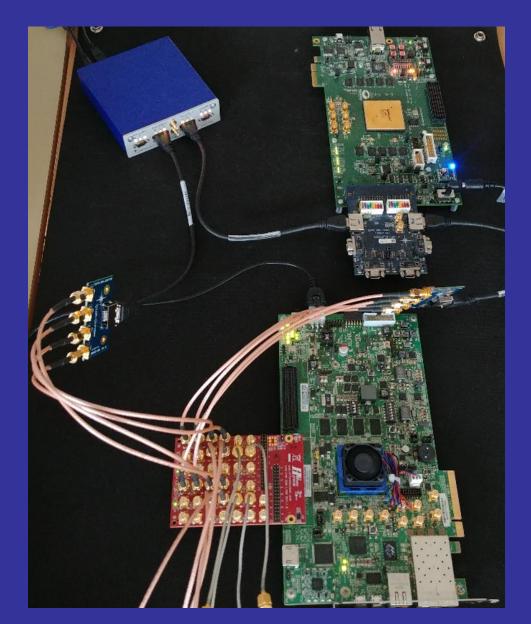

#### SpaceFibre Multi-Lane Interface IP Implementation

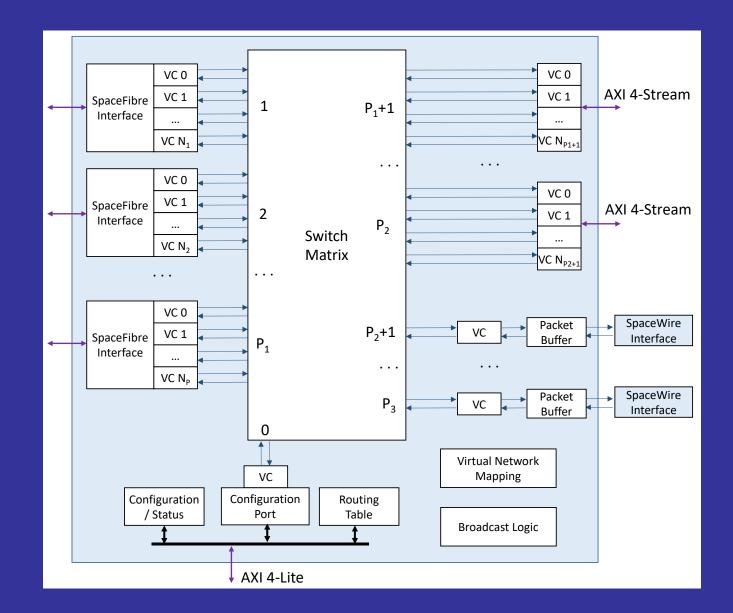

# SpaceFibre Routing Switch IP Core

#### Full non-blocking switch matrix

- Fully configurable

- Port type

- SpaceFibre  $\rightarrow$  Number of lanes, VCs

- AXI4-Stream Internal  $\rightarrow$  Number of VCs

- SpaceWire

- Target technology

- Deterministic low latency switching

- Supports path, logical addressing and group adaptive routing

# SpaceFibre Routing Switch IP Core

- Each virtual channel of each port can be configured to belong to any virtual network.

- Configuration port with RMAP protocol

- Isolates each virtual network using priority, scheduling and bandwidth reservation QoS.

- Within the same virtual network:

- There is packet by packet round robin arbitration for packets going to the same output port

- Automatic packet spill on timeout event caused by unexpected packet blocking, using a configurable virtual channel time-out period.

- Additional timeout timers to detect a babling node

## SpaceFibre Routing Switch IP Core

## SpaceFibre Single-Lane Routing Switch IP Resources

- SpFi Interface IP Cores are <u>included</u>

- Additional Configuration port and RMAP target is also included

- Port count includes 1x internal AXI4-Stream (2 VCs) and 1x SpW ports

|         | RTG4  |       |       | XQRKU060 * |       |        |

|---------|-------|-------|-------|------------|-------|--------|

|         | LUT   | DFF   | LSRAM | LUT        | DFF   | RAMB36 |

| 6 Port  | 31782 | 27393 | 47    | 17984      | 28090 | 48     |

| 2 VCs   | 20.9% | 18.0% | 22.5% | 5.4%       | 4.2%  | 4.4%   |

| 10 Port | 98540 | 76035 | 127   | 55917      | 78051 | 128    |

| 4 VCs   | 64.9% | 50.1% | 60.8% | 16.9%      | 11.8% | 11.9%  |

|         | R     | TPF5007 | *     | <b>XQRVC1902</b> * |       |        |

|---------|-------|---------|-------|--------------------|-------|--------|

|         | LUT   | DFF     | LSRAM | LUT                | DFF   | RAMB36 |

| 6 Port  | 29938 | 26943   | 93    | 17098              | 27652 | 48     |

| 2 VCs   | 6.2%  | 5.6%    | 6.1%  | 1.9%               | 1.5%  | 5.0%   |

| 10 Port | 93526 | 75905   | 253   | 53800              | 75867 | 128    |

| 4 VCs   | 19.4% | 15.8%   | 16.6% | 6.0%               | 4.2%  | 13.2%  |

## SpaceFibre Single-Lane Routing Switch IP Resources

- SpFi Interface IP Cores are <u>included</u>

- Additional Configuration port and RMAP target is also included

- Port count includes 1x internal AXI4-Stream (2 VCs) and 1x SpW ports

|         |       | RTG4  |       | XQRKU060 * |       |        |

|---------|-------|-------|-------|------------|-------|--------|

|         | LUT   | DFF   | LSRAM | LUT        | DFF   | RAMB36 |

| 6 Port  | 31782 | 27393 | 47    | 17984      | 28090 | 48     |

| 2 VCs   | 20.9% | 18.0% | 22.5% | 5.4%       | 4.2%  | 4.4%   |

| 10 Port | 98540 | 76035 | 127   | 55917      | 78051 | 128    |

| 4 VCs   | 64.9% | 50.1% | 60.8% | 16.9%      | 11.8% | 11.9%  |

|         | R     | <b>TPF500</b> | *     | <b>XQRVC1902</b> * |       |        |

|---------|-------|---------------|-------|--------------------|-------|--------|

|         | LUT   | DFF           | LSRAM | LUT                | DFF   | RAMB36 |

| 6 Port  | 29938 | 26943         | 93    | 17098              | 27652 | 48     |

| 2 VCs   | 6.2%  | 5.6%          | 6.1%  | 1.9%               | 1.5%  | 5.0%   |

| 10 Port | 93526 | 75905         | 253   | 53800              | 75867 | 128    |

| 4 VCs   | 19.4% | 15.8%         | 16.6% | 6.0%               | 4.2%  | 13.2%  |

- 6 Port 2 VCs  $\rightarrow$  12 VCs

- 10 Port 4 VCs  $\rightarrow$  36 VCs

- DFF/VC ~ 2200

- LUT4/VC ~ 2600 (RTG4/PF)

- LUT6/VC ~ 1500 (KUS/Versal)

- Easy way to have a ROM of a design from the number of VCs required

## SpaceFibre Multi-Lane Routing Switch IP Core

Presentation coming next about this IP

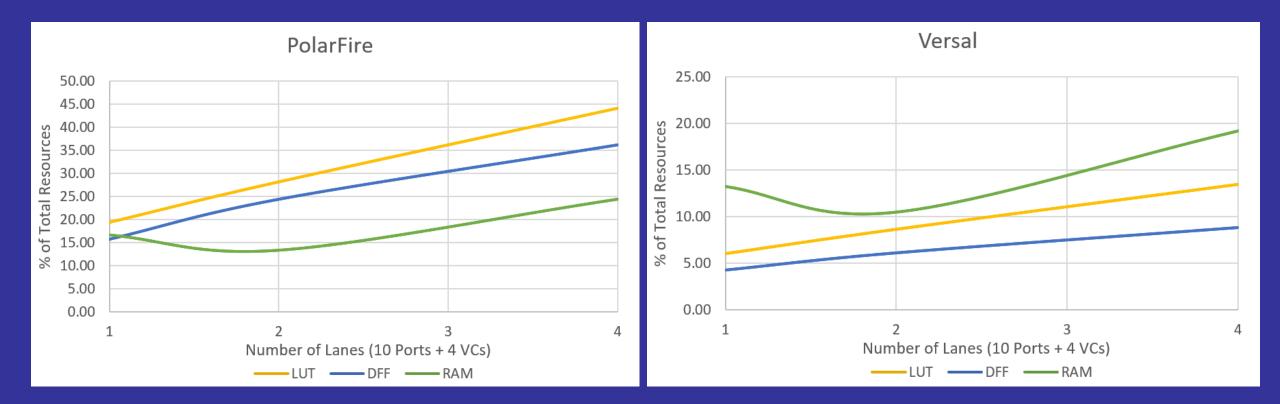

#### SpaceFibre Multi-Lane Routing Switch IP Resources

Values for different configurations (2/4 Lanes and 6 Ports/2 VCs or 10 Ports/4 VCs) available the paper

# SpaceFibre Multi-Lane Routing Switch IP Resources

- Same number of VCs as before

- 6 Port 2 VCs  $\rightarrow$  12 VCs

- 10 Port 4 VCs  $\rightarrow$  36 VCs

- 1-lane Router

- DFF/VC ~ 2200

- LUT4/VC ~ 2600 (RTG4/PF)

- LUT6/VC ~ 1500 (KUS/Versal)

- 2-lane Router

- DFF/VC ~ 3500

- LUT4/VC ~ 3900 (RTG4/PF)

- LUT6/VC ~ 2200 (KUS/Versal)

- 4-lane Router

- DFF/VC ~ 4500-5500

- LUT4/VC ~ 6000 (RTG4/PF)

- LUT6/VC ~ 3500 (KUS/Versal)

- STAR-Dundee provides SpaceFibre Interface and SpaceFibre Routing Switches IP Cores

- Single-Lane and Multi-Lane *flavours* are both available

- The IPs have been designed specifically for space applications

- Designed for the highest performance in RTG4 and other rad-had FPGAs

- A simple SpFi interface only uses 2% of an RTG4 and  $\leq 0.5\%$  of the other FPGAs analysed

- Multi-Lane can be implemented using 4% of an RTG4 and  $\leq$  1% of the other FPGAs

- Exhaustive verification and validation, including radiation testing

#### Conclusions

#### The IPs are easy to implement

- IP Core can be used without knowledge of the internals of the SpaceFibre protocol

- Very simple link management

- Focus on how to process data, not on how it is transferred

- Does not require specific timing or placement constraints

- Reference designs available that show how to interconnect to different SerDes/Transceivers

- End-user support by the same team that designed the IP and contributed to the SpaceFibre standard