# Assessment studies – FPGA Verification Tool - UVVM

**David Merodio Codinachs**

4/12/2019

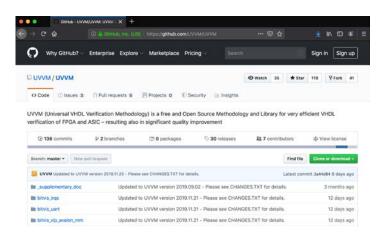

# FPGA Verification Tool - UVVM

- Budget: 210,000 € + 73,463 € (CCN)

- Duration: 18 months (+ 6 months CCN)

- Prime: BITVIS (NO)

- Main Objectives:

- 1. Enable more productive verification by simulation, a key phase in ASICs and FPGAs

- 2. Extend the Universal VHDL Verification Methodology

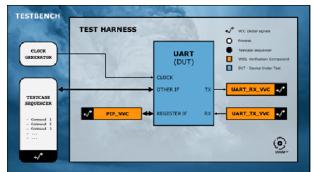

### Universal VHDL Verification Methodology

UVVM is a VHDL testbench infrastructure, Architecture, Library and Methodology for making better VHDL tesbenches. UVVM is used world wide to speed up verification and improve the werall FPGA design quality. Applicable for both FPGAs and ASICs.

**Utility Library**

## Benefits

- Efficient and easy to maintain.

- · Modular, reusable and extendable

- · Vital for FPGA development quality Allows simple control of Constr.Rand. and Func.Cov.

- · Seamless integration with OSVVM Constr.Rand and

- . Modern verification methodology

# FPGA Verification Tool - UVVM

# Extensions within the scope of the activity:

- Scoreboarding

- Monitors

- Controlling randomisation and functional coverage

- Error injection (Brute force and Protocol aware)

- Local sequencers

- Watchdog (Simple and Activity based)

- Controlling property checkers

- Hierarchical VVCs And Scoreboards for these

- Direct Transaction Transfer

- Specification Coverage

Figure 1: UART Testbench in UVVM (courtesy of Bitvis).

TEC-ED & TEC-SW FP Day | 01/12/2019 | Slide 3

ESA UNCLASSIFIED - For Official Use