## LIROC : a Novative RadHard Front-End ASIC for Space Lidar

Julien Fleury,<sup>1\*</sup> Salleh Ahmad<sup>1</sup>, Christophe de La Taille,<sup>2</sup> Stéphane Callier,<sup>2</sup> Ludovic Raux<sup>2</sup>

<sup>1</sup>Weeroc, 4 avenue de la Baltique, 91140 Villebon-sur-Yvette, France ;

<sup>2</sup>Omega, Ecole Polytechnique, Route de Saclay 91128 Palaiseau

\*julien.fleury@weeroc.com

LIDAR is a distance and speed measurement device using reflection characteristics of emitted light. Space industry is using LIDAR to scan planet surfaces before landing missions, to measure distances between spacecraft and for many other applications. Having the most sensitive detector is critical to measure long distances, particularly in space applications. First LIDAR-dedicated silicon photomultipliers are getting on the market among other detectors such as photomultiplier tubes. However, no dedicated electronics is available so far. Main read-out requirement of LIDAR read-out is an excellent timing resolution and a 2ns double-peak separation. None of the ASICs on the market allows such a fast response. Weeroc has designed a LIDAR dedicated multi-channel read-out chip prototype focusing our R&D on bandwidth and fast return to baseline to fulfil LIDAR requirements.

LIROC ASIC is designed in TSMC 130nm CM013G. This technology has been qualified by CERN for its excellent radiation hardness over total irradiation dose. LIROC is a 64-channel front-end ASIC designed to readout silicon photo-multipliers (SiPM) for LIDAR application.

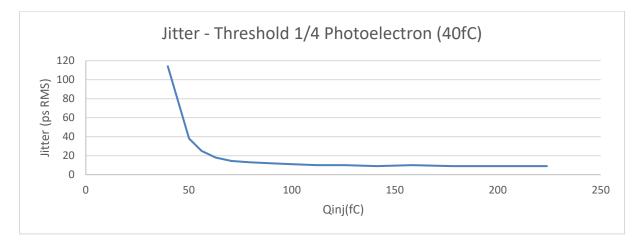

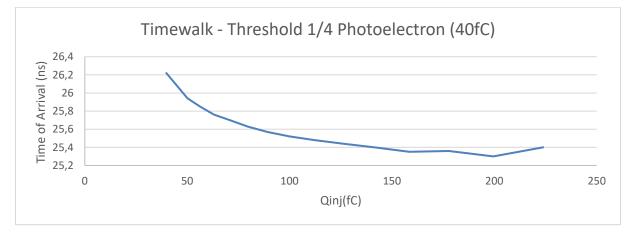

LIROC allows triggering down to 1/3 of photoelectron (50fC) and provides low-voltage differential trigger output for each channel with an excellent timing resolution (better than 20ps FWHM) and excellent double-peak separation (100% efficiency on 5ns separated single photo-electrons). LIROC allows fast single photon counting over 100MHz per channel.

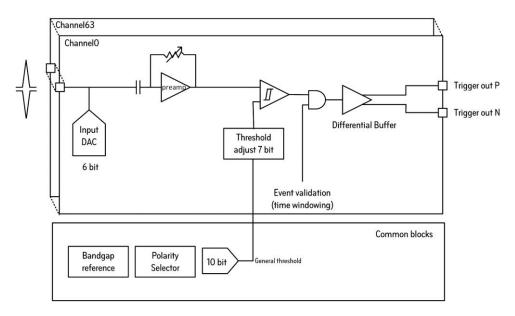

Figure 1 - Liroc block scheme

An adjustment of the SiPM high-voltage (gain) is possible using a channel-by-channel 6-bit DAC connected to the ASIC inputs. Channel-by-channel calibration on the trigger threshold is also possible thanks to 7-bit DACs. LIROC can be calibrated using the dark noise of the SiPM. LIROC features a GHz measurement line composed of an RF preamplifier with pole zero cancellation followed by a fast discriminator and low swing LVDS fast driver. LIROC can be programmed for threshold and several other parameters using a rad-hard I2C interface featuring TMR for SEU detection and correction.

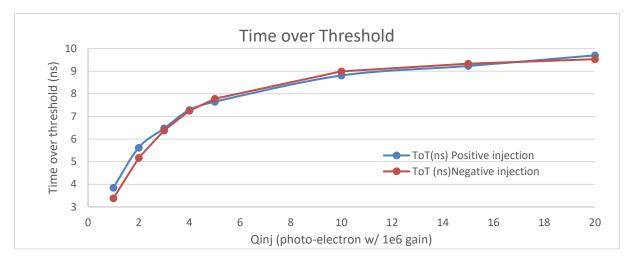

Weeroc measurement shows very good adequation with simulation. Fast photon counting has been validated as well as excellent timing performance and return to baseline to ensure 3ns double peak separation. Liroc can also measure amplitude of incoming signal using a time-over-threshold measurement to have an information on the reflectivity of the target and provide color Lidar images.

Figure 2 - Main Performances of Liroc (Measurement) – Jitter (top), timewalk(middle and time over threshold (bottom)

Liroc can be hooked up to two CERN PicoTDC to build a full LIDAR receiver system capable of large photon counting at few ps timing resolution and single photon sensitivity with an output data rate up to 20Gbps.

| Detector Read-Out                                    | SiPM, SiPM array                                                                                                                                                                                                                          |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of Channels                                   | 64                                                                                                                                                                                                                                        |

| Signal Polarity                                      | Positive or Negative (selectable ASIC-wise)                                                                                                                                                                                               |

| Sensitivity                                          | Trigger on 1/3 of photo-electron                                                                                                                                                                                                          |

| Timing Resolution                                    | Better than 20 ps FWHM on single photo-electron                                                                                                                                                                                           |

|                                                      | Better than 5ns double-peak separation on single photo-electron                                                                                                                                                                           |

| Dynamic Range                                        | Over 100MHz photon counting rate                                                                                                                                                                                                          |

| Packaging & Dimension                                | BGA 20x20 mm <sup>2</sup>                                                                                                                                                                                                                 |

|                                                      | Flip-Chip low inductance packaging technology                                                                                                                                                                                             |

| Power Consumption                                    | 210mW (TBC) – Supply voltage : 1.2 V                                                                                                                                                                                                      |

| Inputs                                               | 64 analogue inputs with independent SiPM HV adjustments                                                                                                                                                                                   |

| Outputs                                              | 64 LVDS triggers                                                                                                                                                                                                                          |

| Internal Programmable Features<br>(I <sup>2</sup> C) | 64 HV adjustment for SiPM (64 x 6 bit), trigger threshold programming<br>(10bits), 64 x 7 bit channel-wise threshold adjustment, ASIC-wise polarity<br>selector, preamp gain adjustment, individual trigger masking and cell<br>powering. |

Liroc features will be presented. Architecture of the different blocks will be described and measurement performed will be shown as well as foreseen applications.