Accomplishing PROMISE, PROgrammable MIxed Signal ASIC Electronics Framework

AMICSA - June 2<sup>nd</sup>, 2022

### Luis Berrojo

Luis-rafael.berrojovalero@thalesaleniaspace.com

100000 PROMISE

# **PROMISE Project** Introduction

European Commission PROMISE

This project has received funding from the EU Horizon 2020 research Horizon 2020 from the EU Horizon 2020 research European Union Funding for Research & Innovation grant agreement No 870358

PROPRIETARY INFORMATION

unec

## **PROMISE** Consortium

- 7 Institutions

- **6 European countries**

- Main user (TAS in France and TAS in Spain)

- Library and IP provider (IMEC)

- Several IP providers (MENTA, IT, VTT and ISD).

- Well balanced:

- 2 Large Enterprises

- 1 Academic partner

- 3 SMEs

- 1 Research center

- One Goal: All-European Mixed-signal ASIC for **Space applications**

Horizon 2020 European European Union funding Commission for Research & Innovation

This project has received funding from the EU Horizon 2020 research and innovation programme under grant agreement No 870358

menta

instituto de

telecomunicações

1

Integrated Systems Development

10010

PROMISE

ISD S.A.

1101101 100000

ThalesAlenia

Space

VTT

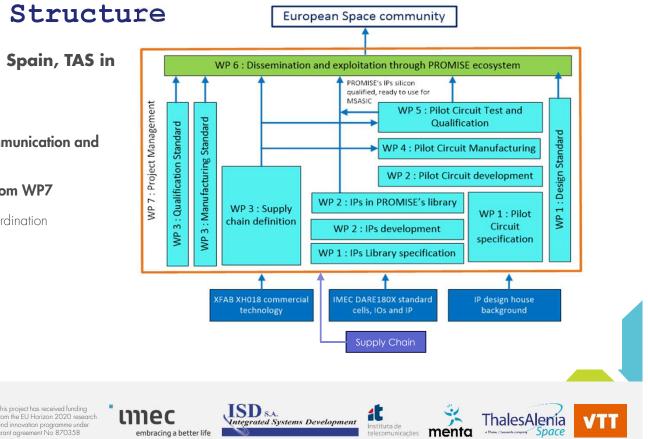

## **PROMISE Project Structure**

- 7 Work Packages led by TAS in Spain, TAS in France, ISD and IMEC

- 5 of them technical

- WP6 dedicated to dissemination, communication and exploitation

- Overall project coordination driven from WP7

- Project management and Technical coordination

- Started in January 2020 -

- Duration: 4 years

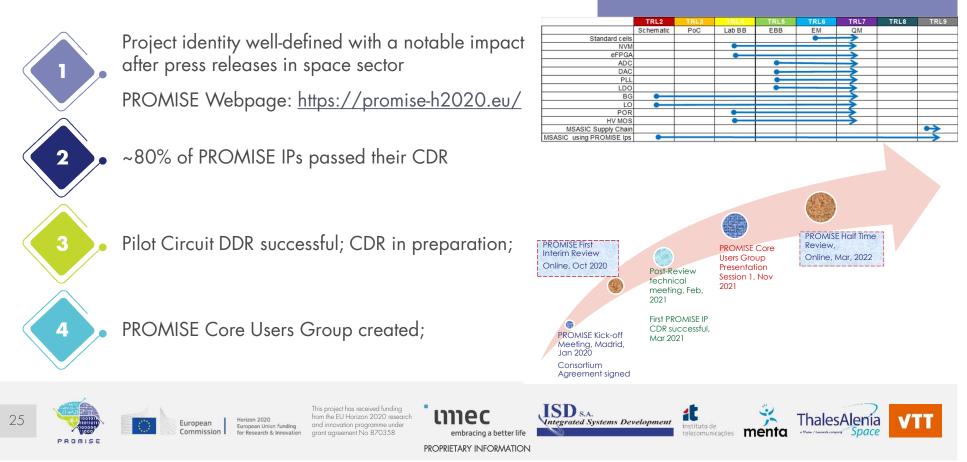

- PROMISE Webpage:

- https://promise-h2020.eu/

## Mission profile

### ✓ Supplies :

- ✓ Low voltage (Digital Core and analog) power supply : 1.8V +/-10%

- ✓ Digital IOs and Analog power supply : 3V3 -5%/+10%

### Junction temperature :

- ✓ TJfuncmin=-40°C and TJfuncmax=125°C

- ✓ TJperfmin=-20°C and TJperfmax=+105°C

European

Commission

### ✓ Life Time :

PROMISE

6

- ✓ Based on XFAB corners and derating curves : 100khours

- ✓ No ageing model available

### ✓ TID :

✓ 100 krad (tested at low dose rate between 36Rad(Si)/h and 360Rad(Si)/h)

### ✓ SEE :

- $\checkmark$  SEL, MBU and SEFI immune up to a LET of 60MeV.cm<sup>2</sup>/mg at the maximum functional temperature

- ✓ SEU rate goal less than 10-8 Ev/day/FF (or memory point)

- $\checkmark$  SET error rate at IP level shall be less than 10-8 Ev/day/block on GEO orbit

1

### HV features

✓ Evaluation for SEGR and SEB safe operating area up to a LET of 60MeV.cm<sup>2</sup>/mg

menta

ThalesAlenia

This project has received funding from the EU Horizon 2020 resear and innovation programme unde arant agreement No 870358

ISD S.A. Integrated Systems Development umec embracing a better life PROPRIETARY INFORMATION

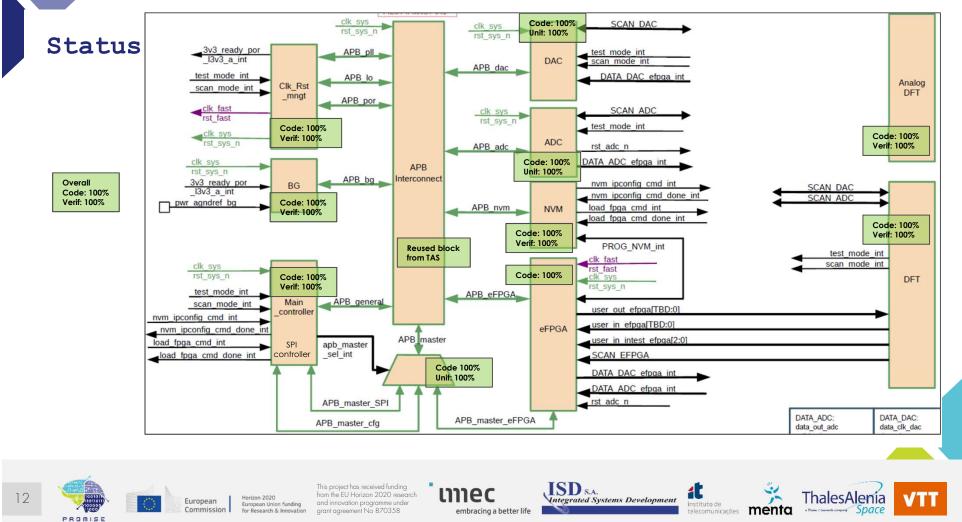

# Pilot Circuit Architecture & Status

European Commission

This project has received funding from the EU Horizon 2020 research Horizon 2020 European Union funding for Research & Innovation grant agreement No 870358

# Pilot Circuit Purpose

- Design a circuit to integrate IPs designed during

PROMISE project

- Support electrical and radiation tests

- $\checkmark$  For design validation

- $\checkmark$  For silicon qualification

- To made qualified and validated IPs available and reusable for the European Space community

menta

ThalesAlenia

VTT

European Horizon 2020 European Unio Commission for Research &

Horizon 2020 European Union funding for Research & Innovation Gran Case of the State of the Stat

PROPRIETARY INFORMATION

1

instituto de

## Top level functionalities

- POR, BG, LDO and LO for safe powerup of the Pilot Circuit.

- Analog ressources : DAC, ADC

- Standard AMBA bus.

- Digital core and PLL

- Analog DFT : monitoring analog by multiplexor accessible through SPI in test mode.

- Pilot Circuit POR eFPGA ADC BG DFT DAC PLL NVM SPI/AMBA Master ADC bus AMBA Bus ADC bus DAC bus SPL Master Slave

- ✓ Hardened Standard Cells (LP and LVT)

- ✓ I/O and Bondpads

### eFPGA + NVM, the core of ASSP

- ✓ HV features test structure

- Specific test structure for LVDS transceivers

3

menta

ThalesAlenia

VTT

- NVM for eFPGA bitstream and configuration.

- Digital DFT (SCAN and JTAG) : covers all digital blocks and eFPGA.

1

instituto de

telecomunicações

| Functional         | modes                              |                | Lest_mode=1' and rst_n=1'                                                                                                                                                   |

|--------------------|------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Inputs                             | 125            | (load_efoga=0' and ip_config=10)                                                                                                                                            |

|                    | Outputs                            | 102            | (vac_enga=o ano p_comg=o) (sReadVVM) (2)                                                                                                                                    |

|                    | Macros                             | 9              |                                                                                                                                                                             |

| EFPGA              | Sequential cells                   | 3050           | p_config_dome='1' and<br>(load efboa='0' or ip_config_config_')                                                                                                             |

|                    | Combinational cells                | 10319          | efpga_control='1' [(bad_efpga='0' or ip_confg_cmd='1']<br>3 [load_efpga='1']                                                                                                |

|                    | Scan Chains (~length)              | 8 (500)        | sEFPGA control control                                                                                                                                                      |

| BG PLL             | Scan Flip-Flops                    | 3002           | 3 (1) [in_config_cmd='1] (1) [ioad_efpga='1' and ]                                                                                                                          |

|                    | ATPG Stuck-at-Faults<br>(coverage) | 86288<br>(95%) | etpga_contol="0"                                                                                                                                                            |

|                    | Clock domains                      | 16             |                                                                                                                                                                             |

| ADC DAC LDO        | Main operating<br>frequency        | 16MHz          | spi_mode = eFPGA control      spi_mode = SPI control      spi_mode = disable        APB_master_sei = eFPGA      APB_master_sei = Command Controller      Spi_mode = disable |

| I_EXTERN_CFG_<1:0> | Mode                               |                | Comments                                                                                                                                                                    |

| 00                 | Normal                             |                | oEPCA IO's are routed to external IO pads                                                                                                                                   |

00 Normal eFPGA IO's are routed to external IO pads External eFPGA configuration 01 eFPGA config signals are routed to external IO pads NVM programming signals are routed to external 10 External NVM programming pads 11 LVDS RX Fail-Safe status Output LVDS RX fail-safe status

European Commission

This project has received funding from the EU Horizon 2020 research Horizon 2020 European Union funding for Research & Innovation grant agreement No 870358

ThalesAlenia

3

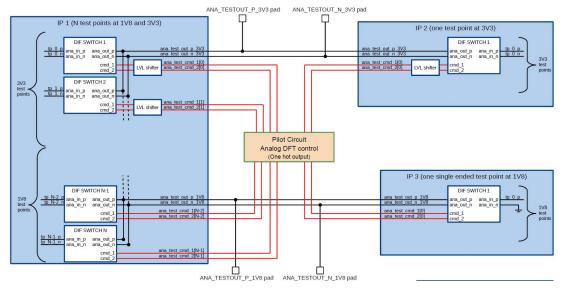

## Analog & Digital DFT strategy

Each blue box represents an IP. All schematics inside a blue box must be implemented inside the corresponding IP. \* NVM has specific signals for Analog DFT DFT Modes

| TI_TEST_MODE[2:0] | Mode                         |

|-------------------|------------------------------|

| 000               | Functional                   |

| 001               | Test-mode                    |

| 010               | Scan-mode pilot circuit      |

| 011               | Scan-mode eFPGA compressed   |

| 101               | Scan-mode eFPGA uncompressed |

| 100               | Boundary Scan                |

- Each IP / TOP has its own SCAN interface:

- Scan-mode, scan-en are common

- ATPG patterns are generated for each IP / TOP independently

- 8 scan-chains: each ~ 500 flops

- ATE clock frequency:10MHz

# **IP** Library **Overview & Status**

PROMISE

European

Commission

This project has received funding from the EU Horizon 2020 research Horizon 2020 European Union funding for Research & Innovation grant agreement No 870358

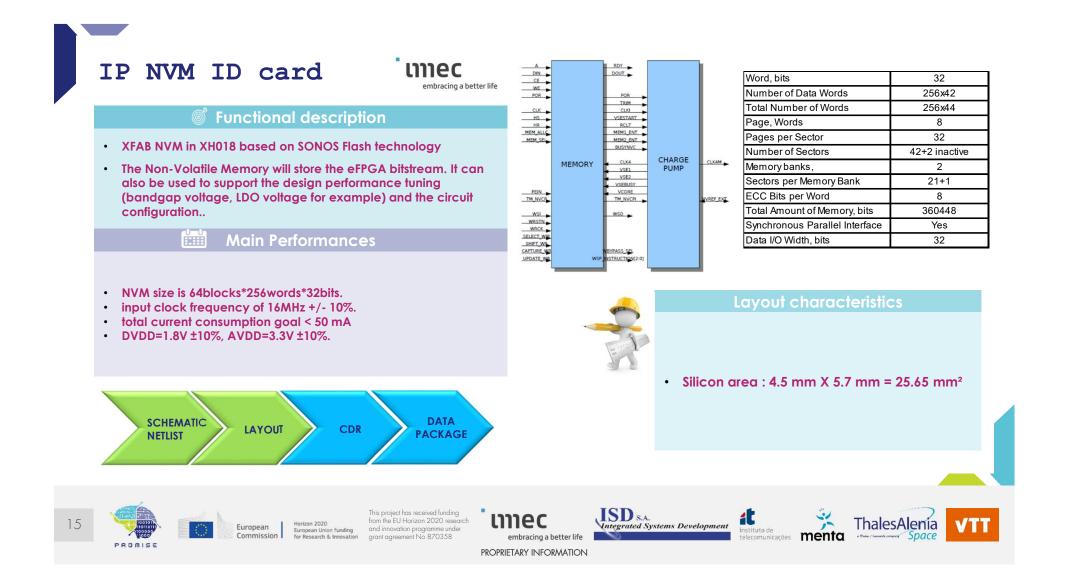

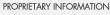

### IP eFPGA ID card

### Functional description

- eFPGA IP of ~1750 LC + 3 DSP similar to Microsemi RTSX32

- Radiation-hardened

- Based on DARE180X heritage and PROMISE rad-hard standard cells from IMEC

- Specific radiation hardened cells to improve density

- Origami Programmer: Menta state-of-the-art eFPGA EDA RTL to bitstream tool

#### Main characteristics

- Equivalent number of logical cells = 1751

- Number of DSP : 3 DSP

- Pre-adder/Multiplier size : 24 bit

- DSP ALU size 48 bits

- Number of clocks : 3

PROMISE

European Commission

Horizon 2020 from European Union Funding and for Research & Innovation gro

This project has received funding from the EU Horizon 2020 research and innovation programme under grant agreement No 870358

eFPGA IP architecture

I/O Bank

I/O Ban

LUT

Config I / 0

PROPRIETARY INFORMATION

eFPGA IP layout

Layout characteristics

• Silicon area : 8.98 mmX10,12 mm=90.88 mm<sup>2</sup>

Consumption : bitstream dependant

• Number of IOs : 391/395 (IN/OUT)

Static Power: 1 mW

# Status

### ✓ 90% done

✓ 80% CDR done

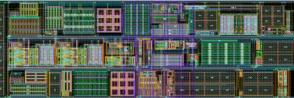

| IP             | SRR              | PDR                                           | DDR                                                   | Layout | CDR  |

|----------------|------------------|-----------------------------------------------|-------------------------------------------------------|--------|------|

|                | (Spec<br>review) | (architecture, schematic and simulation plan) | (Final schematic, simulation at schematic level done) | review |      |

| hvmos          | Done             | Done                                          | Done                                                  | Done   | Done |

| NVM            | Done             | Done                                          | Done                                                  |        |      |

| Standard cells | Done             | Done                                          | Done                                                  | Done   | Done |

| POC            | Done             | Done                                          | Done                                                  | Done   | Done |

| Level shifters | Done             | Done                                          | Done                                                  | Done   | Done |

| IOs            | Done             | Done                                          | Done                                                  | Done   | Done |

| LVDS           | Done             | Done                                          | Done                                                  | Done   | Done |

| POR            | Done             | Done                                          | Done                                                  | Done   | Done |

| BANDGAP        | Done             | Done                                          | Done                                                  | Done   | Done |

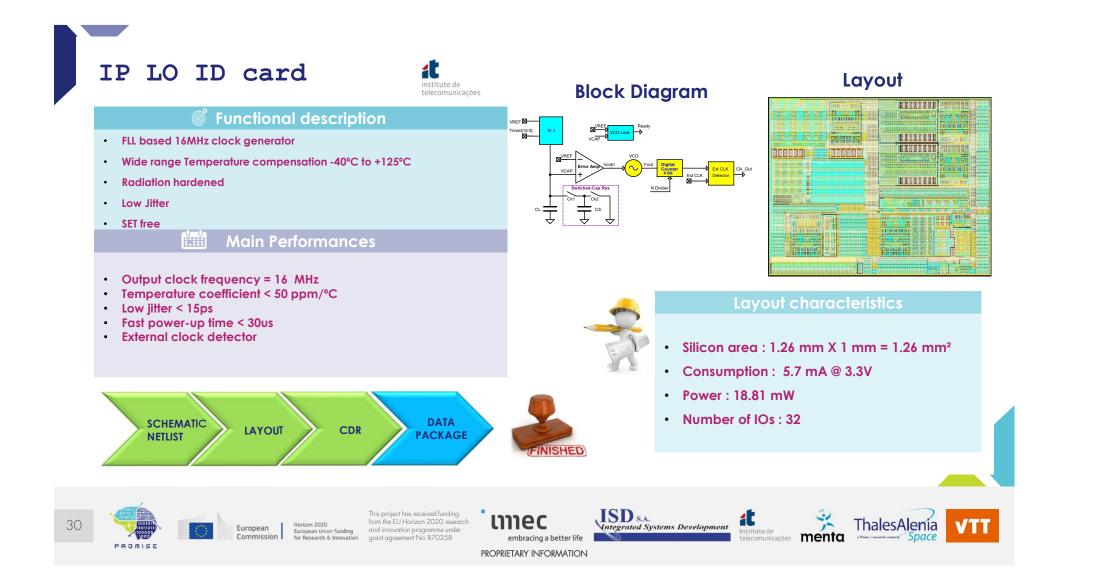

| LO             | Done             | Done                                          | Done                                                  | Done   | Done |

| ADC            | Done             | Done                                          | Done                                                  | Done   |      |

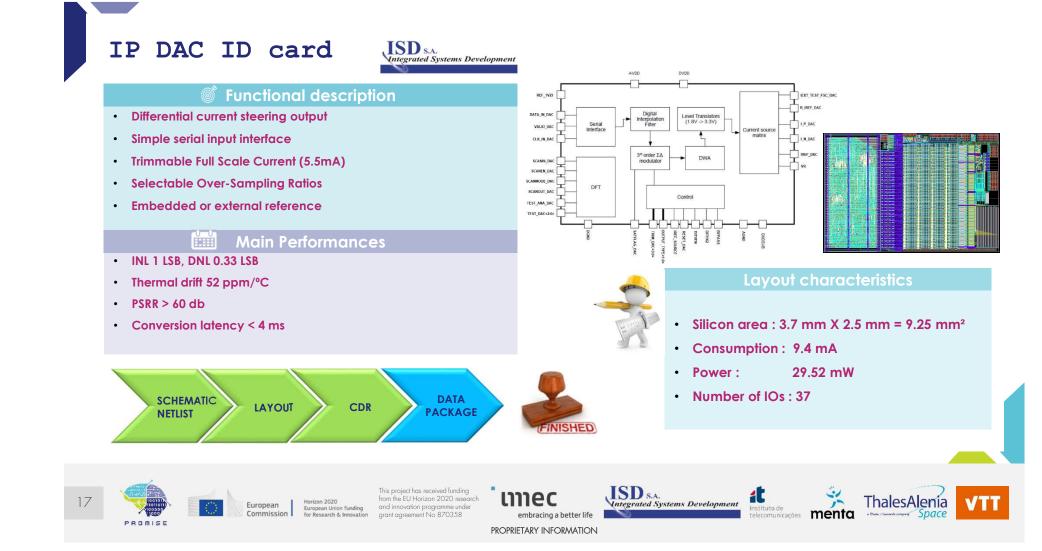

| DAC            | Done             | Done                                          | Done                                                  | Done   | Done |

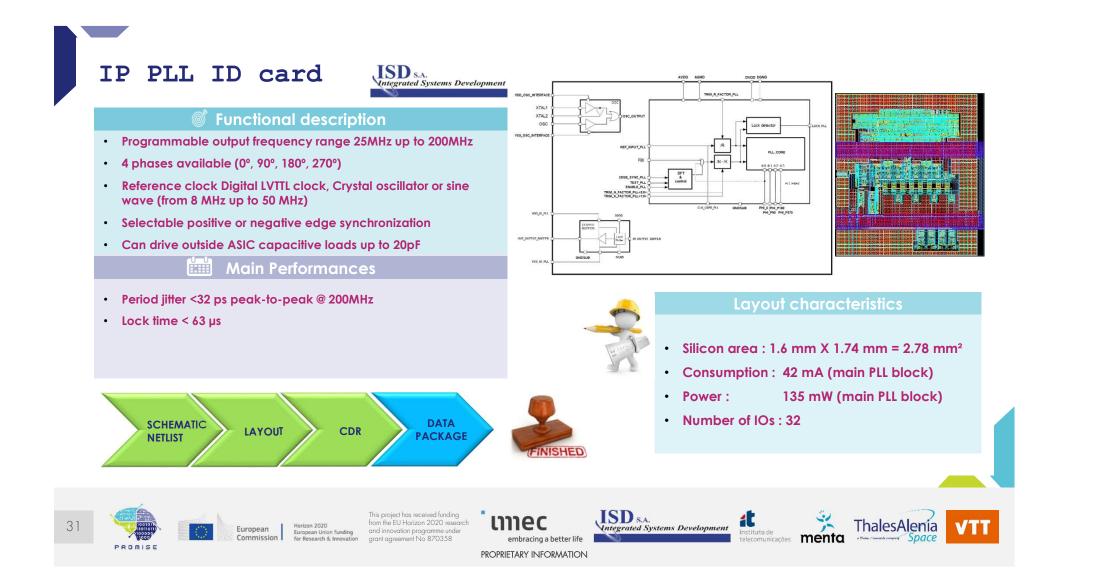

| PLL            | Done             | Done                                          | Done                                                  | Done   | Done |

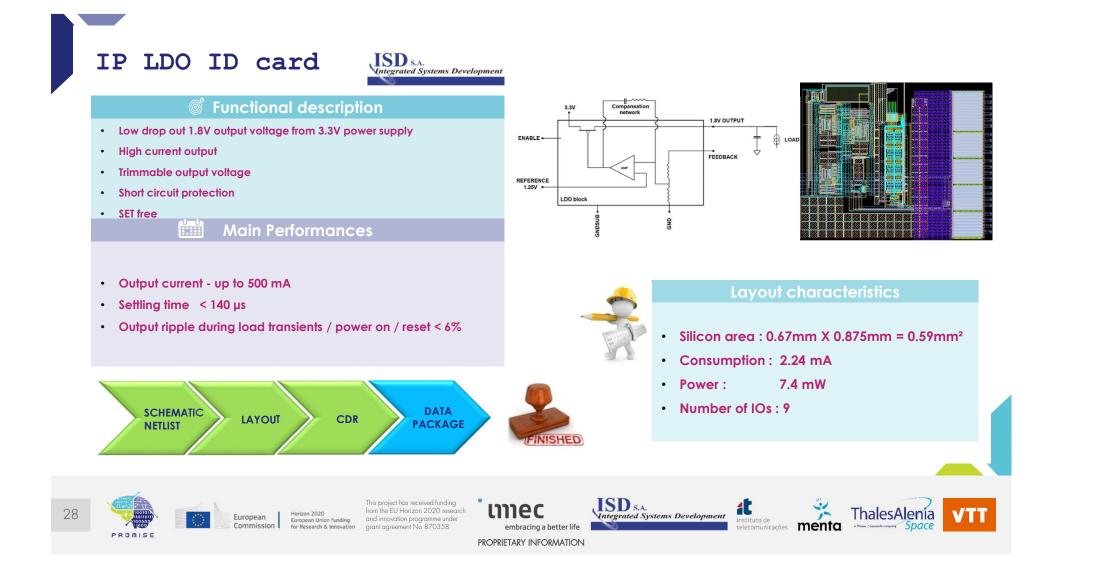

| LDO            | Done             | Done                                          | Done                                                  | Done   | Done |

| eFPGA          | Done             | Done                                          | Done                                                  | Done   | Done |

| Pilot Circuit  | Done             | Done                                          | Done                                                  |        |      |

PROMISE

European Commission

Horizon 2020 European Union frunding for Research & Innovation for Research & Innovation

VTT

# **PROMISE Project Planned Activities**

European Commission

This project has received funding from the EU Horizon 2020 research Horizon 2020 from the EU Horizon 2020 research European Union Funding for Research & Innovation grant agreement No 870358

PROPRIETARY INFORMATION

unec

## Pilot Circuit Test and Qualification

Final step of the design, production and validation chain

Electrical, radiation and silicon qualification tests on the Pilot Circuit □ Assess the space worthiness of the Pilot Circuit Provide silicon qualification status of PROMISE IPs

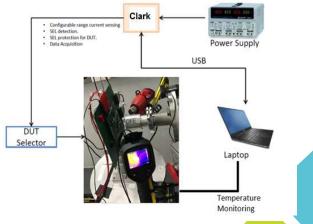

### Task 5.1: Test Board Design and Manufacturing - IN PROGRESS

Development of Test setup: all the elements of the ASIC and measure its performances under laboratory, temperature, radiation....

D5.2 : Electrical Validation plan D5.3 : Radiation Validation plan (TID + SEE) D5.4 : Test board datapackage

Task 5.2: Electrical and radiation tests of Pilot Circuit Run 1 - Participants: TASF, MENTA, VTT - Facilities & beam foreseen by Q2-23.

Test the electrical and radiation performances consistency with the IPs and Pilot Circuit requirements.

D5.5 : Electrical Validation report D5.6 : Radiation Validation report

This project has received funding from the EU Horizon 2020 research European Union funding and innovation programme under for Research & Innovation arant aareement No 870358

umec

### Task 5.3 Qualification of Pilot Circuit

Leader: TASF/Supply Chain - Participants: VTT, MENTA

Includes all qualification steps in compliance with the Manufacturing Plan Standard and Pilot Circuit Procurement Specification.

The Pilot Circuit is submitted to the silicon qualification flow.

Qualification foreseen on the Pilot Circuit, after successful validation of the electrical and radiation specification.

For each of these IPs and for Pilot Circuit, its qualification status will include

- □ usage restrictions and/or recommendations

- production yield

- □ drift during screening and HTOL.

This project has received funding from the EU Horizon 2020 resea for Research & Innovation for Research & Innovation grant agreement No 870358

# **PROMISE Project** Conclusions

European Commission PROMISE

This project has received funding from the EU Horizon 2020 research Horizon 2020 from the EU Horizon 2020 research European Union Funding for Research & Innovation grant agreement No 870358

# Conclusions

PROMISE targets to become an ecosystem built around an IP Library qualified for Space usage

✓ Faster, Cheaper, Lower Risk Mixed Signal ASICs can be manufactured

✓ Participation is open for End Users, Supply Chain actors, Technology and Design providers

Contributions and cooperation will build a stronger community and benefit the contributors

✓ Further IP library details will be shown on final CUG workshop presenting project results & outcomes.

# Thank you

European Horizon 2020 European Unio for Research &

Horizon 2020 European Union funding for Research & Innovation

## Main achievements

## **RTL Verification Plan**

- 8 Unitary test benches + 1 Global test bench ٠

- 69 test cases ٠

- Verification status •

- Code coverage ٠

- ٠

: 100% PASS

- : 100% COVERAGE

- Reference document : [0005-0015514539] PROMISE PILOT CIRCUIT ASIC VERIFICATION PLAN (29/03/2022)

| Design Scope <  | Hits % • | Coverage % ◄ | Total Coverage: (F | iltering A | Active) |          |          | 85.88%  | 100.00%    |

|-----------------|----------|--------------|--------------------|------------|---------|----------|----------|---------|------------|

| i_dut           | 100.00%  | 100.00%      | Coverage Type ◄    | Bins 🖪     | Hits 🖪  | Misses 4 | Weight 4 | % Hit ◄ | Coverage • |

| i propici top 0 | 100.00%  | 100.00%      | Statements         | 2072       | 2072    | 0        | 1        | 100.00% | 100.00%    |

|                 |          |              | Branches           | 1346       | 1346    | 0        | 1        | 100.00% | 100.00%    |

|                 |          |              | FEC Expressions    | 139        | 139     | 0        | 1        | 100.00% | 100.00%    |

|                 |          |              | FEC Conditions     | 281        | 281     | 0        | 1        | 100.00% | 100.00%    |

|                 |          |              | FSMs               | 236        | 236     | 0        | 1        | 100.00% | 100.00%    |

|                 |          |              | States             | 87         | 87      | 0        | 1        | 100.00% | 100.00%    |

|                 |          |              | Transitions        | 149        | 149     | 0        | 1        | 100.00% | 100.00%    |

Horizon 2020 European Union funding European Commission for Research & Innovation

This project has received funding from the EU Horizon 2020 research and innovation programme under grant agreement No 870358

VTT

26

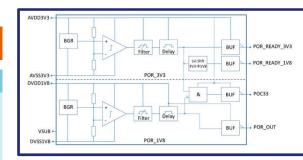

## IP POR

## VTT

### Functional description

- Two independent POR devices supporting 3.3V/1.8V power supply (PS) domains

- BG voltage reference for accurate POR signal generation

- Delay added before POR signal released

- Undervoltage pulse filter

- SET free

### Main Performances

- Valid PS voltage ranges = 3.3V-5%/+10% and  $1.8V \pm 10\%$

- POR released/undervoltage corners = 3.1V/2.9V and 1.60V/1.52V

LAYOUT

- Compatible with PS rise times = 10ns...100ms

- Min POR delay = 100 µs

- UV pulse filter = 10 ns

**SCHEMATIC**

NETLIST

PROMISE

#### Layout characteristics

- Silicon area : 641µm x 209µm

- Consumption: 0.3 mA

- Power: 1 mW

- Number of IOs : 17

European Commission

Horizon 2020 European Union funding for Research & Innovation grant agreem

CDR

This project has received funding from the EU Horizon 2020 research and innovation programme under grant agreement No 870358

DATA

PACKAGE

PROPRIETARY INFORMATION

INISHED

# Next Steps (2/2)

|                       |                                                                          |              |   |     | 2 | 020 |     |    |      |      |      |                  |      | 2    | 021 |      |      |    |       |      |          |      | 20   | 122      |       |          |           |          |      |            |       | 20     | 023      |          |          |            |              |

|-----------------------|--------------------------------------------------------------------------|--------------|---|-----|---|-----|-----|----|------|------|------|------------------|------|------|-----|------|------|----|-------|------|----------|------|------|----------|-------|----------|-----------|----------|------|------------|-------|--------|----------|----------|----------|------------|--------------|

|                       | Work program                                                             | 1 2          | 3 | 4 5 | 6 | 7   | 8 9 | 10 | 11 1 | 12 1 | 2    | 3                | 4 5  | 6    | 7   | 8 9  | 9 10 | 11 | 12 1  | 2    | 3        | 4 :  | 56   | 7        | 89    | 10       |           | 2 1      | 2    | 3          | 4 5   | 6      | 1        | 8        | 9 10     | 11         | 12           |

|                       |                                                                          | 1 2          | 3 | 4 5 | 6 | 7   | 8 9 | 10 | 11 1 | 12 1 | 3 14 | 15               | 16 1 | 7 18 | 19  | 20 2 | 1 22 | 23 | 24 25 | 5 26 | 27       | 28 2 | 9 30 | 31       | 32 33 | 34       | 35 3      | 6 37     | 38   | 39         | 40 41 | 42     | 43       | 44       | 45 46    | i 47       | 48           |

|                       | rary and Pilot Circuit specification                                     | 4            |   |     |   |     |     |    | _    |      | _    |                  |      | -    |     | _    | _    |    | _     | _    |          |      | _    |          |       |          | _         | _        | -    |            | _     |        |          |          | _        |            | _            |

| 1.1 TASF<br>1.2 TASF  | Establish standards for Mixed Signal IP Cores Design                     | _            |   |     | _ |     | _   |    | _    | _    | _    |                  | _    |      |     | _    | _    |    | _     | _    |          | _    | _    |          | _     |          | _         | _        | -    |            | _     | -      |          |          |          |            |              |

| 1.2 TASE<br>1.3 TASE  | IPs Specification<br>Pilot Circuit Specification                         | -            |   |     |   |     |     |    |      | -    | _    |                  |      |      |     |      |      |    |       |      |          |      | -    |          |       |          |           | -        |      |            |       | -      |          |          |          |            |              |

| 1.3 TASE<br>1.4 IMEC  | Plot Circuit Specification<br>Ps Format Definition and Validation Checks | ++-          |   |     |   |     |     |    |      |      |      |                  |      |      |     | -    | _    |    |       |      |          |      | -    |          |       |          |           | -        |      |            | _     | -      |          |          |          | -          |              |

|                       | Pilot Circuit Development                                                |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          | _         | -        |      |            | _     | -      |          |          |          | -          |              |

| 2.1 IMEC              | Standard Cells and IOs Hardened Design, + LVDS                           | 4            |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      | -    |          |       |          |           | -        | -    |            | -     | -      |          |          |          |            |              |

| 2.1 INEC              | Analog IP BG Hardened Design                                             | _            |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      | -    |          | _     |          | -         | -        | -    |            | -     | -      |          |          |          |            |              |

| 22 IT                 | Analog IP LO Hardened Design                                             | ++-          |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      | -    |          |       |          |           | -        | -    |            | -     |        |          |          |          |            |              |

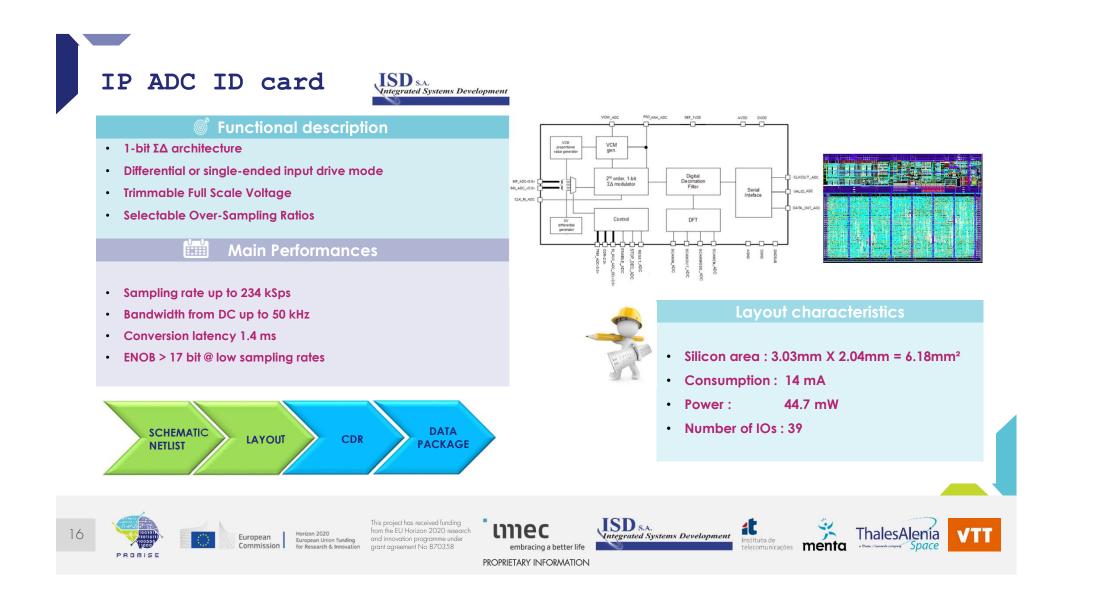

| 2.3 ISD               | Analog IPs ADC Hardened Design                                           | ++-          |   |     | - |     |     |    |      |      |      |                  |      | -    |     |      |      |    |       |      |          |      |      |          |       |          |           | -        |      |            | -     |        |          |          |          |            | _            |

| 2.3 ISD               | Analog IPs DAC Hardened Design                                           |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 2.3 ISD               | Analog IPs LDO 1V8 Hardened Design                                       |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      | +        |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 2.3 ISD               | Analog IPs PLL Hardened Design                                           |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 2.4 VTT               | Analog IPs (POR) Hardened Design                                         |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 1.5 IMEC              | NVM Hardened Design                                                      |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 2.5 IMEC              | HV cells Hardened Design                                                 |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 2.6 MENTA             | eFPGA Hardened Design                                                    |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 2.7 TASF              | Pilot Circuit Top Level Hardened Front-end Design                        |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 2.8 IMEC              | Pilot Circuit Top Level Hardened Back-end Design                         |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      | GDSI     |       |          |           |          |      |            |       |        |          |          |          |            |              |

| VP3 TASF SUPPL        | Y CHAIN DEFINITION                                                       |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 3.1 TASF              | Define manufacturing plan standard                                       |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 3.2 TASF              | Define Qualification Plan Standard                                       |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            | month | margin | for Pilo | ot Circu | it subst | rat lead t | time         |

| 3.3 TASF              | Identify European actors space mixed ASIC supply chain                   | $\downarrow$ |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      | Ŷ          |       |        |          |          |          |            |              |

| 3.4 TASF              | Define Supply Chain for Pilot Circuit                                    |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

|                       | rcuit MANUFACTURING                                                      |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      | 1    |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 4.1 IMEC              | Foundry of Pilot Circuit                                                 |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      | Y    |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 4.2 TASF/Supply Chain | Design Package for the Pilot Circuit :                                   |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          | 2 month o | design + |      | n lead tim |       |        |          |          |          |            |              |

| 4.3 TASF/Supply Chain | Industrialization of Pilot Circuit                                       | ++           |   |     |   |     |     |    |      |      | _    |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          | Test | solutor    |       |        | 1        |          |          |            |              |

| 4.4 TASF/Supply Chain | Manufacturing Pilot Circuit                                              | ++           |   |     |   |     |     |    |      |      |      |                  |      |      |     |      | _    |    |       |      |          |      | _    |          |       |          |           |          |      | (2         | weeks |        |          |          |          | 2 margir   | 1            |

| 4.4 TASF/Supply Chain | Manufacturing Pilot Circuit                                              | <u>++-</u>   |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       | Asser  | mbly 8   | weeks    |          |            |              |

|                       | rcuit TEST AND QUALIFICATION                                             |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      |            |       |        |          |          |          |            |              |

| 5.1 TASE              | Test Board Design and Manufacturing                                      | ++           | + |     |   |     | _   | +  |      |      | +    | $\left  \right $ |      |      | +   |      | +    |    |       | +    |          |      | _    | $\vdash$ | _     |          |           |          |      |            |       |        |          |          |          | +          |              |

| 5.2 TASE              | Electrical and radiation tests of Pilot Circuit                          |              | + |     | _ | ++  | _   | +  |      |      | _    | $\left  \right $ |      |      | ++  |      | _    | +  |       |      | $\vdash$ |      | _    | $\vdash$ | _     | $\vdash$ |           |          | -    |            |       |        |          |          |          | <u> </u>   |              |

| 5.3 TASF/Supply Chain | Qualification of Pilot Circuit : screening                               |              | + |     |   | ++  |     |    |      |      | _    | +                |      |      | ++  | _    | _    | +  |       |      |          |      | _    | $\vdash$ |       | +        | _         |          |      |            |       |        |          | Screenin | ng : 2 m | onths avai | ilable : 1 m |

| 5.3 TASF/Supply Chain | Qualification of Pilot Circuit                                           |              |   |     |   |     |     |    |      |      |      |                  |      |      |     |      |      |    |       |      |          |      |      |          |       |          |           |          |      | -          | -     |        |          |          |          |            |              |

PROMISE

European Commission

Horizon 2020 European Union funding for Mesearch & Imnovation for Research & Imnovation

VTT