# Rad-hard Microcontroller with Open Access ISA for Space Applications

**H2020 Programme Space Theme**

Milos Krstic, <u>Felipe Kuentzer</u>, Klaus Tittlebach, Cristiano Calligaro, Umberto Gatti, Juan Cueto, Fatima García Donday, Michael Schmidt, Bernhard Schommer, Christian Ferdinand, Axel von Blomberg

June 3<sup>rd</sup>, 2022

9th International Workshop on Analogue and Mixed-Signal Integrated Circuits for Space Applications

## **Agenda**

- Background

- MORAL Project Introduction

- MORAL Microcontroller

- PEAKTOP Architecture

- Specification

- Digital Design

- Technology and PDK

- Memory and Analog IPs

- Evaluation Board

- MORAL Software

- PEAKTOP Toolchain

- Compiler and RTSK

- Development Status

#### Small satellites – 2030 and beyond

- Low-cost small satellites (from 10 kg to 500 kg)

- Potential for scientific research and practical applications

- Small satellite modern applications

- Satellite swarms or constellations replacing large satellites

- Augmented satellite based navigation systems

- Satellites in commercial aviation.

- Commercial satellite imagery based services

- Robotic servicing technologies for space applications

- Mainly powered by traditional electronics

- Increased capabilities, but reduced reliability

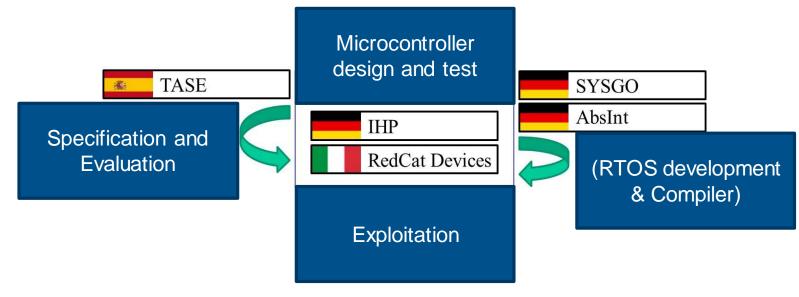

#### MORAL Project – H2020 Space Theme Programme

- Duration from 01. January 2020 to 30. April 2023 (40 months)

- Funded by the EC GA No. 870365

- Two main objectives

- Develop a completely European, ITAR-free microcontroller for space applications

- Exploitation plan for entering the market

- 5 partners

#### Introduction

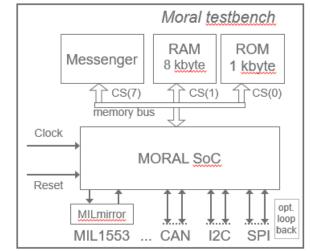

#### MORAL in a nutshell

- Microcontroller based on the novel PEAKTOP architecture, including a novel Instruction Set Architecture (ISA)

- Formally-verified C compiler, RTOS, and toolchain

- Demonstrator board

- Irradiation tests

- Aggressive exploitation plan for bringing the product into market

#### **MORAL Microcontroller - PEAKTOP**

#### Why a new processor core architecture?

- IHP's PEAKTOP architecture

- Freely available

- Complete control over each aspect of the microcontroller

- ITAR-free

- Scalable (e.g., to 64-bit)

- More than TMR and ECC features

- PEAKTOP provides mixed criticality support

- Multiple functions with different criticalities and assurance levels to co-exist in the microcontroller architecture

- General Purpose Register (GPR) banks can be dynamically grouped

- Dual-, Triple- or Quadruple-Modular Redundant (DMR/TMR/QMR) module to increase the fault tolerance

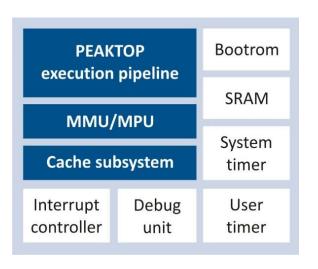

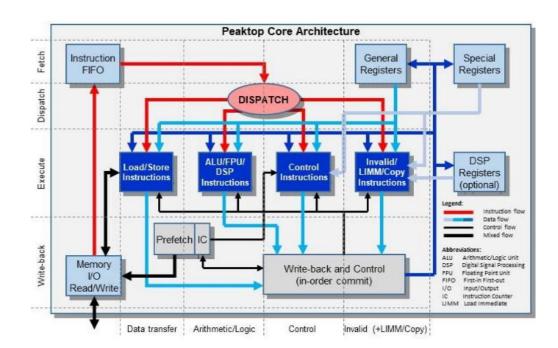

#### **PEAKTOP Architecture**

- IHP's own processor

- Open ISA

- Core architecture characteristics

- RISC architecture

- Up to 64 GPR

- IEEE 754 compliant Floating Point Unit (FPU)

- Optional Digital Signal Processing (DSP) extension

- New ISA is fully orthogonal, regular, and circular

- Multiprocessing support (cache coherence, synchronization support, atomic transfers)

- Configurable addressing space: up to 64-bit; virtual address space is up to 128-bits

- 32-bit wide instructions up to 3 operands

- 2-level Memory Protection Unit (MPU), or (optionally) 2-level Memory Management Unit (MMU)

- Optional L1 (separate data/instruction) cache, and L2 cache

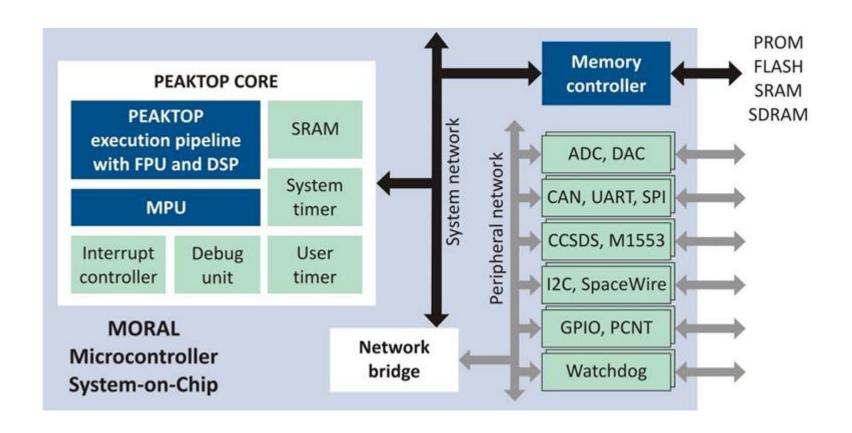

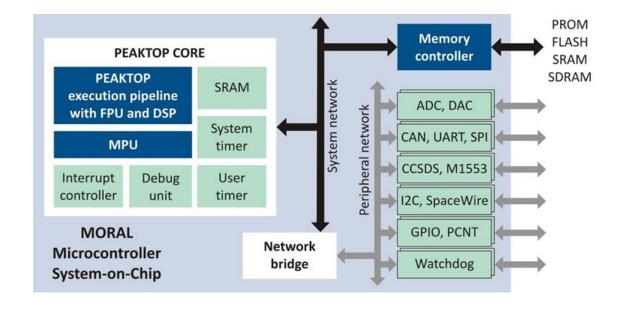

# **MORAL Microcontroller – Specification**

# **MORAL Microcontroller – Specification**

- 256/512 Kbyte SRAM

- Error Detection and Correction (EDAC) protection unit

- 1 x Interrupt Controller

- 32 interrupt lines

- 6 x Timers

- 2x system + 4x user timers

- 64 x GPIO ports

- Shared with internal peripherals I/Os

PROM, FLASH, SRAM, SDRAM

# **MORAL Microcontroller – Specification**

#### Peripherals

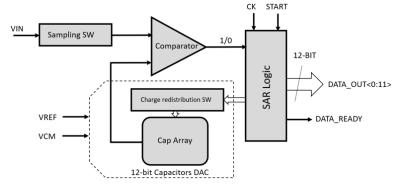

- 1 x 8-channel 12-bit ADC

- 2 x 12-bit DAC

- 2 x CAN 2.0 modules

- 4 x UART interfaces

- 2 x SPI interfaces

- 2 x SpaceWire interfaces (incl. RMAP protocol)

- 1 x MIL-STD 1553C bus interface (incl. redundant bus)

- 2 x I2C interfaces

- 1 x 8-channel PWM generator

- 4 x Pulse counters

- 1 x Watchdog timer

# M1553B Watchdog

#### Rad-Hard Specification

- Total ionizing dose (TID) 100 krad (Si)

- Single event upset (SEU) for the processor's digital core >30 MeVcm²/mg

- Single event latch-up (SEL) >60 MeVcm²/mg

# **MORAL Microcontroller – Digital Design**

- Processor core design

- PEAKTOP previously developed, implemented, and tested in IHP 130nm technology

- FPU design and redesigned of MPU to support the RTSK needs

- Peripherals design an integration

- MIL-STD 1553C designed at IHP

- Peripheral in the specification integrated

- Verification

- Carried every step of the design, from RTL simulations to post-synthesis, and in FPGA

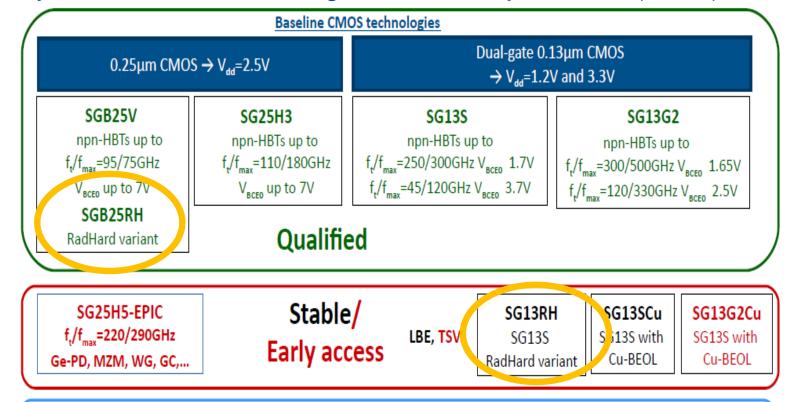

## **MORAL Microcontroller – Technology and PDK**

#### Commercially available IHP Technologies – Multi Project Wafer (MPW)

SG25H5Cu-EPIC SG25H5\_EPIC with Cu-BEOL Under development

W2W bonding Backside RDL RadHard MOS devices

Next generation SG13G3  $f_t/f_{max}$ >450/650GHz

# MORAL Microcontroller – Technology and PDK

IHP SG13S/RH - PDK for Space Applications

|                                                                                                                                                                                   | SG13S/RH                                                                                                                                 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ■ Process Description                                                                                                                                                             | SiGe HBTs npn Peak $f_T/f_{MAX}$ 220/340GHz<br>130nm Dual Gate $-$ Oxide CMOS<br>( $V_{DD}$ =+1.2 $V$ , +3.3 $V$ ; $T_{OX}$ = 2nm / 7nm) |  |  |

| ■ Commercial Qualification                                                                                                                                                        | completed 2014                                                                                                                           |  |  |

| - Based on JEDEC Standard JP001.01                                                                                                                                                |                                                                                                                                          |  |  |

| - EPPL/QML/QPL (ESCC QPL, ESCC QML, MIL QPL, JAXA QPL)                                                                                                                            | Evaluation ongoing                                                                                                                       |  |  |

| ■ PDK Availability ■ Access Status                                                                                                                                                | In development-Early Access NDA/EXPORT License                                                                                           |  |  |

| ■ CMOS Std Cell Core and IO Libraries                                                                                                                                             | IHP IXC013RH (~ 90 cells)                                                                                                                |  |  |

| ■ Radiation Assessment (Digital) ■ TID ■ CMOS Libraries                                                                                                                           | 100krad(Si) – 300krad(Si)<br>SEU/SEL completed                                                                                           |  |  |

|                                                                                                                                                                                   | SEL Threshold > 65MeV/cm²/mg<br>(RHBD IHP cells)                                                                                         |  |  |

|                                                                                                                                                                                   | SEU Threshold > 30MeV/cm²/mg<br>(IHP RTMR FF)                                                                                            |  |  |

| ■ Evaluation Testing in acc. ESCC No. 2269010                                                                                                                                     | Activ ity started                                                                                                                        |  |  |

| ■ Operation Temperature (max rated T <sub>J</sub> )                                                                                                                               | -55°C to +125°C (TBC)                                                                                                                    |  |  |

| ■ Test Vehicles ■ in acc. ESCC No. 2269010                                                                                                                                        | TCV, DEC -I DEC-II(CMOS, Bipolar) RIC in progress                                                                                        |  |  |

| <ul> <li>Radiation Tests</li> <li>TCV (Devices, analog)</li> <li>DECs (Digital, Analog BiCMOS)</li> <li>RIC (Mixed-Signal IC)</li> </ul>                                          | completed                                                                                                                                |  |  |

|                                                                                                                                                                                   | DEC-I (SEU/SEL <sup>"</sup> ), Early structures planned                                                                                  |  |  |

| <ul> <li>Endurance Testing HT &amp; RT</li> <li>HBT npn-devices</li> <li>HBT lifetime determination</li> <li>CMOS devices</li> <li>CMOS Core &amp; IO Std Cell Library</li> </ul> | Activity started (qualification of technology for general purpose applications done)                                                     |  |  |

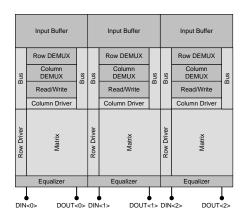

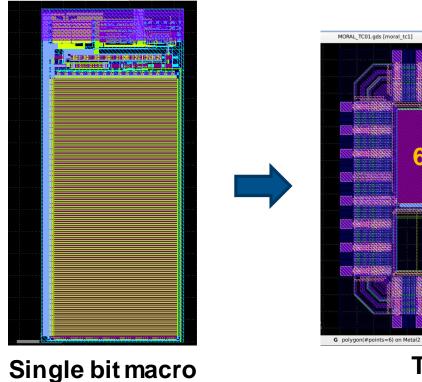

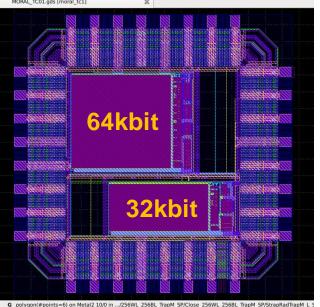

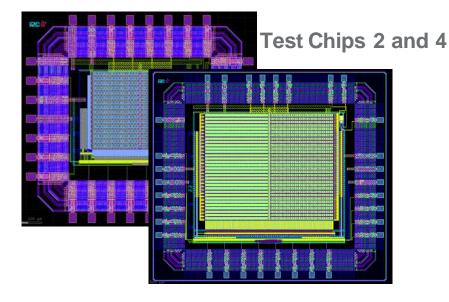

# **MORAL Microcontroller – Memory and Analog IPs**

- Rad-hard SRAMs

- Independent decoding schemes

- 6T SRAM cell

- Island Guard Ring (IGR) instead of Enhanced Guard Ring (EGR)

- Tradeoff between inter-device leakage degradation and area

RC7CSP32K1B.gds [RC7CSP32K1B] 💥

Test Chip 1

AMICSA'22 Workshop June 3, 2022 14

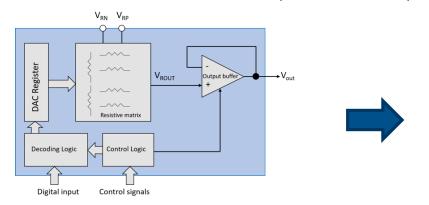

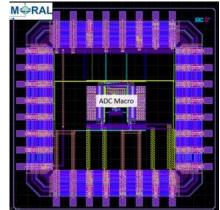

# **MORAL Microcontroller – Memory and Analog IPs**

- Rad-hard 12-bit DAC

- Architecture based on resistor divider (Kelvin divider)

Architecture - SAR (Successive Approximation Register)

Single-ended and differential

**Test Chips 3**

### **MORAL Microcontroller – FPGA Board**

- Implementation on programmable hardware platform

- Early hardware debug

- Early tests of complex software

- Ex.: Operating system, compiler and assembler tool-chain, and simple applications

- Project dissemination

- Opportunity for the academia to know and experiment with the new architecture

For availability of an evaluation board use the contact form in MORAL's website.

www.moral-project.com

June 3, 2022

**FPGA** board

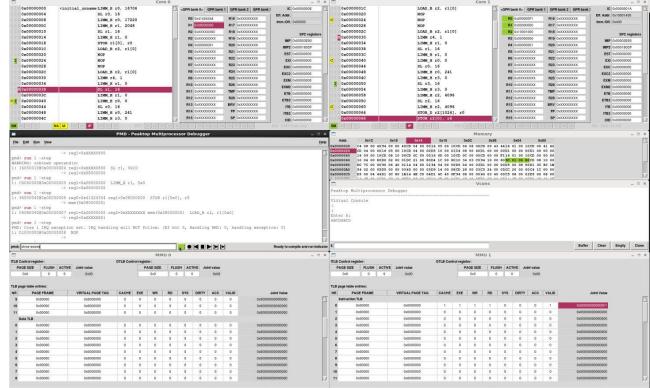

## **MORAL Software – PEAKTOP Toolchain**

- Open source toolchain

- Multiprocessor Debugger

- Instruction Set Simulator

- Complete ISA and tools documentation

https://www.moral-project.eu/acad\_open\_source.html

# **MORAL Software – Compiler and RTSK**

### CompCert – 2021 ACM Software System Award

- Compiler for C programming language

- The only **formally verified** compiler in the market

- Free for evaluation, research, and education

- Commercial licenses distributed by AbsInt

- Porting of CompCert for the PEAKTOP architecture

- Implementation of binary utilities

- Optimization and formal verification

- Semi-automatic testing with FPGA board

# **MORAL Software – Compiler and RTSK**

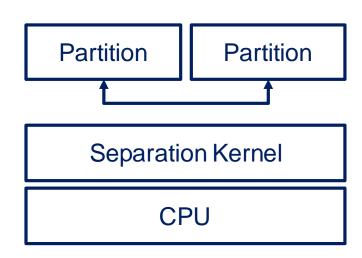

- Real Time Separation Kernel RTSK

- Provides isolated partitions

- Communication between partitions

- Partition is an execution environment that

- Serves as a virtual CPU

- Contains a guest operating system

- RTSK tailored for the PEAKTOP microcontroller.

- Microcontroller for space platforms provide limited RAM for any COTS

- Must have a very low footprint

- Separation kernel prototype

- First release for project partners

- Running on the FPGA board

AMICSA'22 Workshop June 3, 2022 19

# Development Status

| MORAL Project                            | Status | Period  | Comments                               |

|------------------------------------------|--------|---------|----------------------------------------|

| Prototype specification                  | done   | Q2 2020 | Completed                              |

| Prototype design                         | done   | Q1 2021 | FPU, DSP support, and M1553            |

| Prototype functional tests               | done   | Q1 2021 | Integration and functional simulations |

| Prototype emulation                      | done   | Q2 2021 | Running on the FPGA board              |

| Memory and analog IPs design             | done   | Q4 2021 | SRAM, DAC, and ADC                     |

| Test chips fabrication                   | done   | Q4 2021 | Four test chips                        |

| RTSK                                     | done   | Q4 2021 | Running on the FPGA board              |

| Compiler - CompCert                      | done   | Q1 2022 | Porting and verification completed     |

| SRAM, DAC, and ADC test chips evaluation | done   | Q2 2022 | 12-bit DAC and 12-bit ADC              |

| Drivers, library, and software tools     |        | Q1 2023 | Specification on-going                 |

| Prototype fabrication and testing        |        | Q2 2022 | Layout on-going                        |

| Prototype stress tests                   |        | Q1 2023 | Radiation test PCB on-going            |

| Prototype demonstrator                   |        | Q1 2023 | Demonstrator PCD on-going              |

AMICSA'22 Workshop June 3, 2022 20

#### **MORAL Website**

- Access for more information and news about MORAL

- Links for the project Social Media

- PEAKTOP toolchain download

www.moral-project.eu

# Thank you for your attention!

Felipe Kuentzer

www.moral-project.eu