# New ECSS standards for ASIC, FPGA and IP Core engineering and product quality assurance

Agustín Fernández-León ESA ESTEC TEC-E Ref.: ESA-TECE-HO-2022-003286 ADCSS 2022 25/10/2022

ESA UNCLASSIFIED - For ESA Official Use Only

## Contents

- 1. Scope of the new ECSS standards for ASIC/FPGA/IP Cores

- 2. History of ASIC/FPGA ECSS standards

- 3. How did the WG work, starting points

- 4. Main FORMAT changes and goals in new standards

- 5. Table of contents of new standards, the annexes

- 6. Engineering and Product Assurance requirements: to be applied in parallel

- 7. Focus on E-ST-20-40 standard:

- main differences vs. old ECSS-Q-60-02C engineering chapter

- Terminology: term definitions, conventions, equivalence between engineering and management std terms

- generic development flow and variations, phases and reviews name differences vs old standard

- DEVICE criticality pre-tailoring

- Distribution of requirements according to DEVICE type

- 8. How to submit "change requests" during Public Review (deadline Nov 18th 2022)

# ECSS standards for ASIC, FPGA and IP Cores

Applicable in **R&D activities** and **projects**, setting high level requirements for the successful engineering and product assurance of the development by the supplier, and the supervision By the customer of:

- **ASICs** Application Specific Integrated Circuits

- Sometimes ASICs are developed to be Standard Products ("ASSP"), sold and used by different companies

- Can be digital, mixed-signal or analog

- Microprocessors, µC, DSPs, GPUs are a special "general purpose" group of ASICs

#### **[FPGAs**] Field Programmable Gate Arrays

- Customer "programmed" devices. (e.g. designs programmed onto Microchip, NanoXplore or Xilinx FPGAs).

- "blank" devices (e.g. European BRAVE FPGA family by NanoXplore).

- Can embed "processing" cores (will use SW to operate!)

### [IP Cores] Intellectual Property Cores

- "soft" models of integrated circuits,

- reused as "building blocks" to develop ASICs and FPGAs faster

All ESA missions use tens, sometimes hundreds, of these complex microchips and IPs

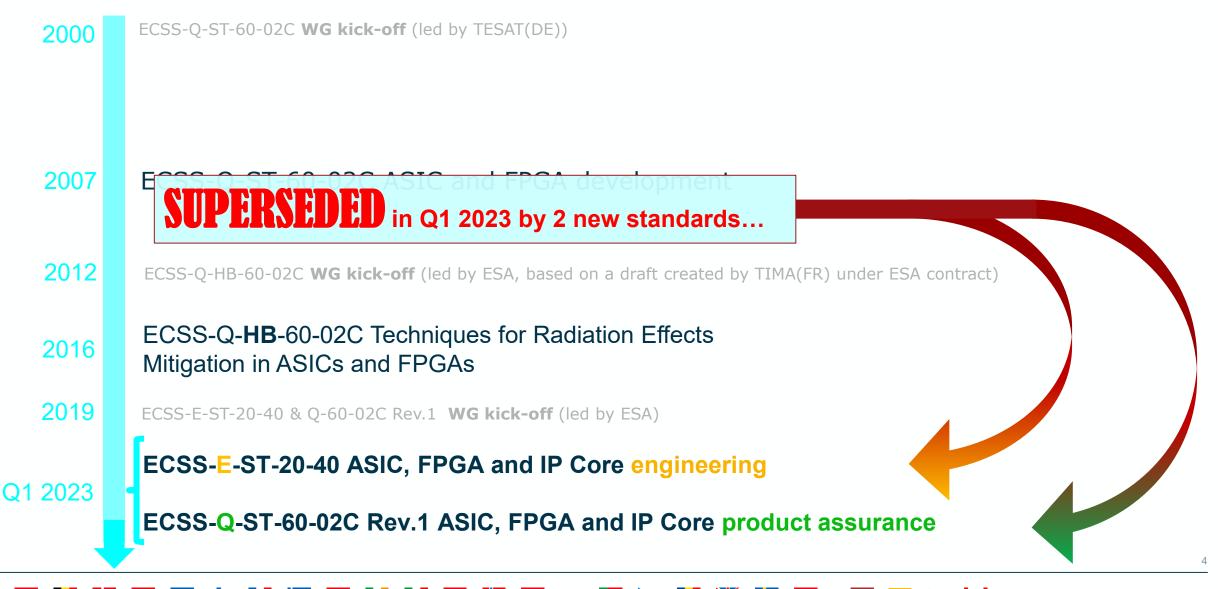

# Timeline: ECSS ST and HB for ASIC and FPGA

# Timeline: NEW ECSS Stds for ASIC, FPGA and IP Core

| eesa |  |

|------|--|

|------|--|

- preliminary list of 28 Change Requests proposed by ESA Microelectronics Section Aug 2017 Apr 2018 - 42 change requests proposed by 11 ASIC/FPGA experts from European companies and institutes (including TAS, ADS, RUAG, Arquimea, Cobham Gaisler, TESAT, IMEC, CNES) at a meeting at ESTEC New ECSS-E-ST-20-40 & Q-60-02C Rev.1 WG kick-off : 10 members, 37 experts Oct 2019 (TAS, ADS, OHB, GMV, TESAT, Cobham Gaisler, BSC, Ariane, RAL, CNES, DLR and ESA) - ECSS-E-ST-20-40 & Q-60-02C Rev.1 in Public Review between Aug 23rd – Oct Nov 18<sup>th</sup> 2022 Aug 2022 - Expected publication of new standards after WG Q1 2023 ECSS-E-ST-20-40 ASIC, FPGA and IP Core engineering ECSS-Q-ST-60-02C Rev.1 ASIC, FPGA and IP Core product assurance processes all requests for changes

#### ECSS-E-ST-20-40 - engineering

starting points : All chapters and requirements of old ECSS-Q-ST-60-02C chapter 5 (ASIC and FPGA engineering), all requests for changes gathered from industry and ESA experts, reviewed item by item, improving/adding/superseding many requirements, having as reference a generic development flow that admits variations, different types of DEVICES, and 2 main criticality levels.

#### ECSS-Q-ST-60-02C Rev.1 – product assurance

A splinter sub-WG created the completely new draft, then reviewed with entire WG reviewed. Took inspiration from Q-ST-80 (SW Product Assurance), but adapted to DEVICE (IC and IP) developments, as PA complement to the new E-ST-20-40. Seeking compliance to ECSS-Q/M branches (Q-10, Q-20, Q-30, M-40, M-10).

# The "old" ECSS-Q-ST-60-02C had engineering and PA

#### Table of contents

| Change log                                 | 3      |     |

|--------------------------------------------|--------|-----|

| Introduction                               |        |     |

| 1 Scope                                    | 8      |     |

| 2 Normative references                     |        |     |

| 3 Terms, definitions and abbreviated terms | 10     |     |

| 4 ASIC and FPGA programme management       | .15    | 000 |

| 5 ASIC and FPGA engineering                | .17    | 85% |

| 6 Quality assurance system                 | .37    |     |

| 7 Development documentation                | .40    |     |

| 8 Deliverables                             | .46    |     |

| Annexes A-J (normative) – DRDs             | .47-61 |     |

| Bibliography                               | .62    |     |

\*

# The "old" ECSS-Q-ST-60-02C had engineering and PA

### 15% is product / quality assurance , dependability

But with simple references to other Q-branch stds – New Q-60-02C Rev.1 has expanded such requirements for clarity and coherence with Q-branch ECSSes

| 4 ASIC and FPGA programme management | 15 |

|--------------------------------------|----|

| 4.1 General                          | 15 |

| 4.1.1 Introduction                   | 15 |

| 4.1.2 Organization                   | 15 |

| 4.1.3 Planning                       | 15 |

| 4.2 ASIC and FPGA control plan       |    |

| 4.3 Management planning tools        | 16 |

| 4.3.1 ASIC and FPGA development plan | 16 |

| 4.3.2 Verification plan              | 16 |

| 4.3.3 Design validation plan         | 16 |

| 4.4 Experience summary report        | 16 |

| 6 Quality assurance system              | 37 |

|-----------------------------------------|----|

| 6.1 General                             |    |

| 6.2 Review meetings                     | 37 |

| 6.3 Risk assessment and risk management |    |

# New standards: main FORMAT changes and goals

- Separation of engineering (in E-ST-20-40) versus product assurance requirements (in Q-ST-60-02C Rev.1)

- Minimize dispersion of requirements between main chapters and normative annexes (DRD = Document Requirements Definition). Most requirements are now in DRDs

- Minimize redundancies (particularly inside each std, E and Q).

- consistent **terminology**, also wrt new SW ECSS-E-ST-40 std,

- **better** and **new definitions** of terms used in the context of this standard.

- Improve the quality and clarity of requirements, the figures and tables used, the overall

organization of the information

#### ■ ■ ■ ■ • ■ • ■ ■ ■ ■ • THE EUROPEAN SPACE AGENC

# new standards separate engineering and PA requirements CESA

#### ECSS-E-ST-20-40 (2022) ECSS-Q-ST-60-02C Rev.1 (2022) 5 Product Assurance programme implementation 5.1 Organization and responsibility 5.2 DEVICE product assurance programme management 5 DEVICE engineering 5.3 Risk management and critical item control 5.1 General requirements 5.4 Supplier selection and control 5.2 **DEVICE** Definition Phase 5.5 Tools and supporting environment 6 DEVICE Process Assurance 5.3 **DEVICE** Architecture Definition Phase 6.1 DEVICE development lifecycle 5.4 **DEVICE** Design and Verification Phase 6.2 Requirements applicable to all DEVICE engineering 5.5 **DEVICE** Detailed Design Phase processes/phases 5.6 6.3 Requirements applicable to individual DEVICE engineering **DEVICE** Layout Phase processes and activities **DEVICE** Implementation Phase 5.7 6.4 Process Assessment and improvement 5.8 **DEVICE** Validation, Acceptance and 7 DEVICE product quality assurance Maintenance Phase 7.1 Product quality objectives and metrication 7.2 IP Core or DEVICES intended for Reuse 6 Pre-tailoring according to DEVICE criticality and type 8 DEVICE Configuration Management 8.1 DEVICE Configuration Management planning and control 8.2 Configuration Management implementation + 12 Annexes (9 DRDs) 8.3 Configuration Control 9 Tailoring by DEVICE criticality + 5 Annexes (3 DRDs) Separation similar to ECSS-E-ST-40 SW engineering and ECSS-Q-ST-80 SW PA, compliant to ECSS-Q-ST-10/20/30 Product assurance

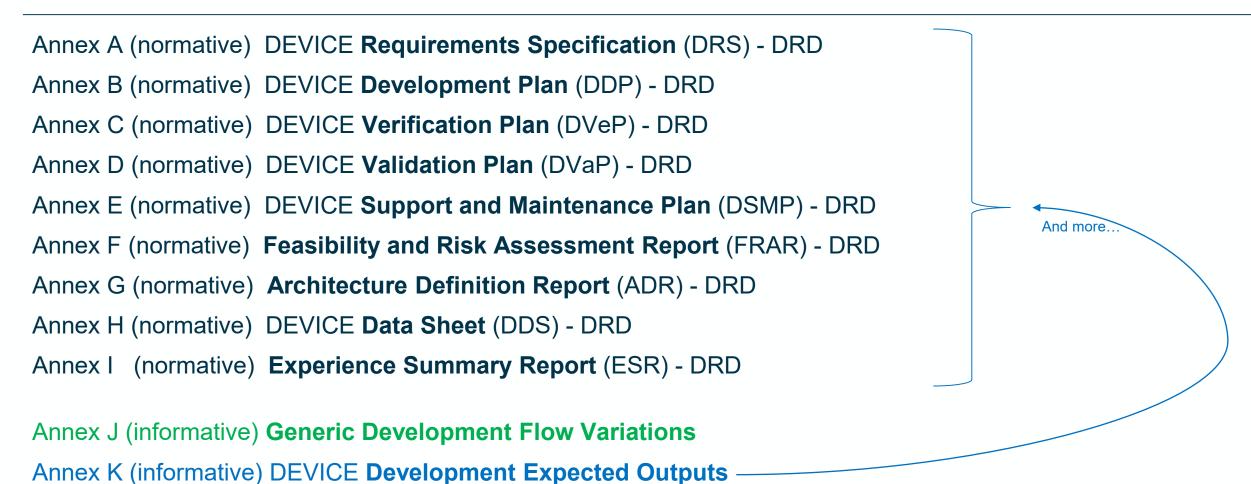

## E-ST-20-40 Annexes (when "normative", it contains requirements too !)

Annex L (informative) Equivalence of phase and milestone terminology of ECSS-M-ST-10 and ECSS-E-ST-20-40

# **Q-ST-60-02C Rev.1 Annexes** (if "normative" contain requirements too !)

Annex A (normative) Product Assurance Plan (DPAP) - DRD

- Annex B (normative) Product Assurance Report (DPAR) DRD

- Annex C (normative) **DEVICE Reuse File (DRF) DRD**

- Annex D (informative) **DEVICE Development Expected Outputs**

Annex E (informative) Traceability from ECSS-Q-ST-60-02C to ECSS-Q-ST-60-02C Rev1

| VCD (Verification Control Document) | ECSS-E-ST-10-02 Annex B |

|-------------------------------------|-------------------------|

| EIDP (End Item Data-Package)        | ECSS-Q-ST-20 Annex B    |

| CMP (Configuration Management Plan) | ECSS-M-ST-40 Annex A    |

| CIDL (Configuration Item Data List) | ECSS-M-ST-40 Annex C    |

| ABCL (As-Built Configuration List)  | ECSS-M-ST-40 Annex D    |

| SCF (SW Configuration File)         | ECSS-M-ST-40 Annex E    |

# the thin line separating engineering from

## product assurance requirements

There are some requirements overlaps between the E-ST-20-40 and Q-ST-60-02 Rev.1 stds, as the Eng/PA borderline is at times blurry.

Also same or very similar things are called sometimes different names, and sometimes same words can have different meanings in the context of different standards (e.g. "verification", "validation" or "qualified", which needs context words : "ECSS PA qualified" vs. "ESCC qualified" vs. "MIL QML-V qualified"...)

Q-60-02C Rev.1 adheres strictly to other applicable ECSS Q and M standards, using their terminology, while E-ST-20-40 uses terminology that is widely used by ASIC and FPGA engineers – "Annex L" in E-ST-20-40 aims to facilitate the understanding of the equivalence of some phase and milestone terms used in E-20-40 and M-10

Both standards shall be applied, in parallel, and supervised by:

- an ASIC/FPGA/IP engineer (e.g. ESA technical officer or expert) and

- a Product Assurance responsible.

Customer "DEVICE acceptance" as "fully verified and validated" (E-20-40) and "PA qualified" (Q-60-02C Rev.1)

is subject to successful final reviews as defined in both standards

14

# FOCUS now on

# The DEVICE <u>engineering</u> standard ECSS-E-ST-20- 40

# Major differences between ECSS-E-ST-20-40 and old standard engineering chapter – (1/2)

- 1. New term definitions and several old ones improved

- 2. Many **NOTES** added with more **examples**

- 3. Most requirements are now "first level" (can be tailored individually). Only a few "level 2" sub-lists

- 4. Tags indicating the applicability of each requirement to 4 main DEVICE types: [D-ASIC, A-ASIC, FPGA, IP]

- 5. General Requirements covering:

- Tailoring according to DEVICE type and DEVICE criticality (a single table in chapter 6 for both)

- > This table can be transformed in a "csv" or "XLSX" file to easily pre-tailor each specific case

- Clearer DEVICE engineering "generic development flow" and introduction of "flow variations"

- All Phase Reviews share a common set of requirements

# Major differences between ECSS-E-ST-20-40 and old standard engineering chapter (2/2)

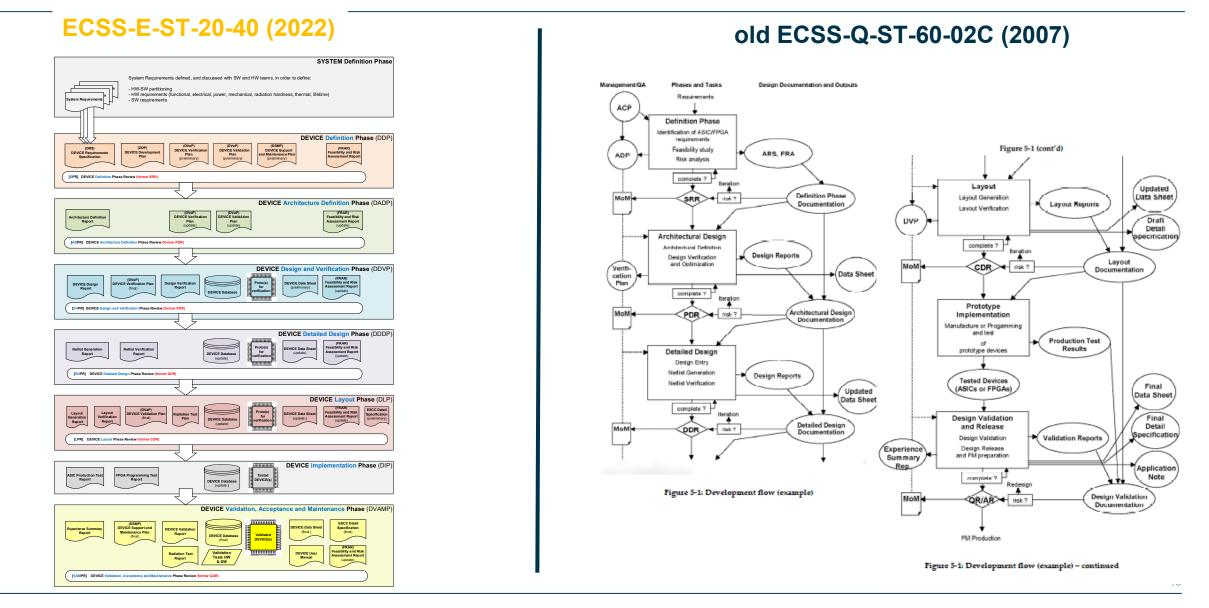

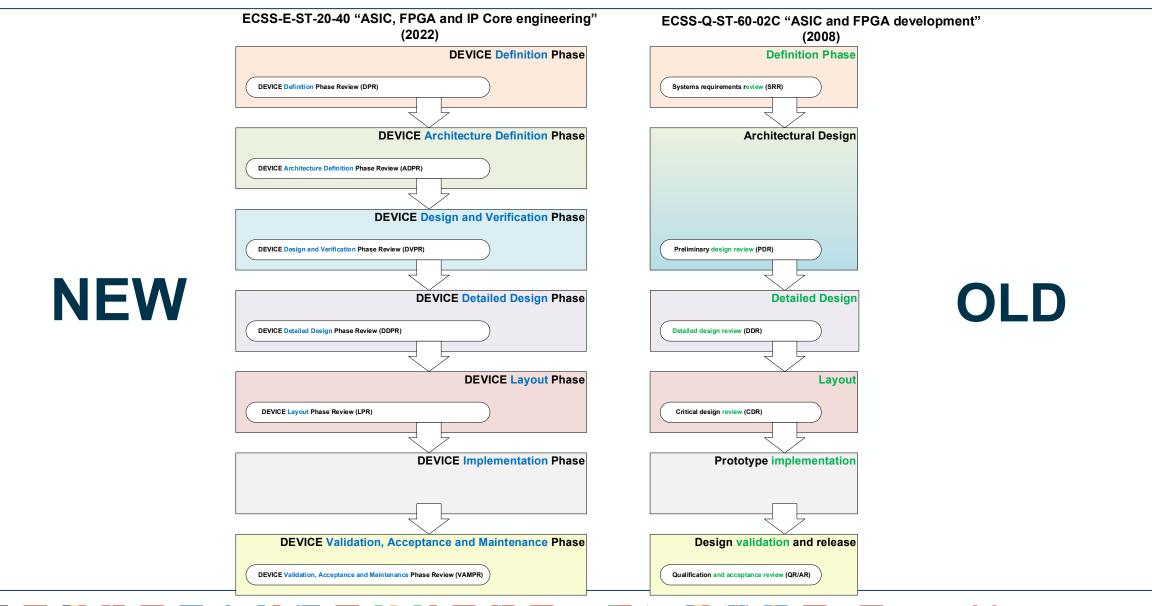

- 6. Improved and more **development flow figures** (in fig. 5-1 and figures in Annex J)

- New phase and review names more self explanatory and commonly used in DEVICE engineer community deviating sometimes from typical "system/equipment" milestone or document names as per ECSS-M-ST-10 (new annex L added to explain names equivalence with Management stds)

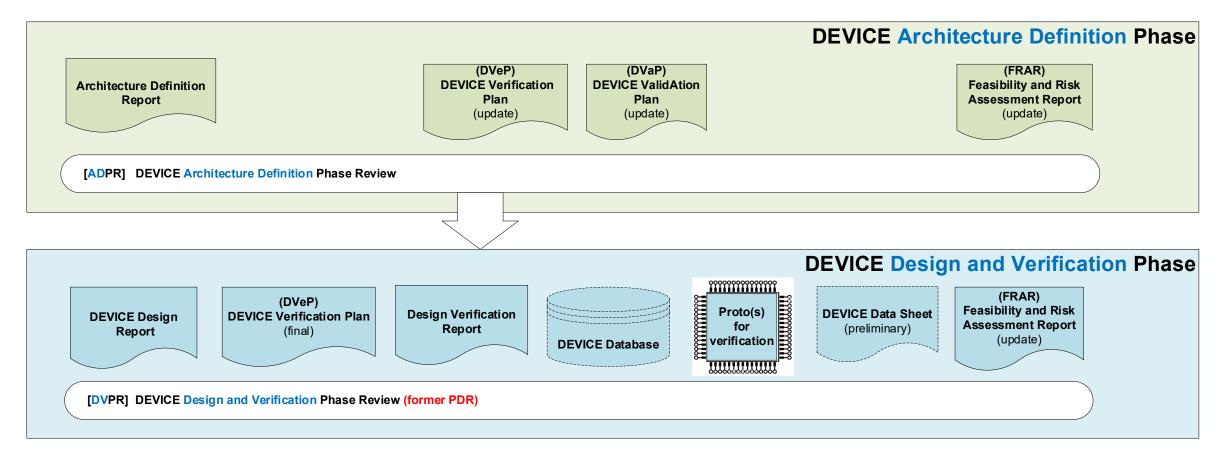

- 8. Additional phase added between old SRR and old PDR: "DEVICE Architecture Definition Phase"

- 9. New requirements added and some improved or superseded by new ones for:

- DEVICES that contain "processing units" (which will use SW to operate) to ensure better HW-SW coengineering

- II. re-use of "IP Cores" and "building-blocks"

- III. mixed-signal ASICs / analog IPs

- IV. More comprehensive sets of requirements for DEVICE Requirements Specification, and for Development, Verification and Validation Plans

# New standards: terminology

#### New term definitions: 3.4.2 Companies involved in the DEVICE Building block development : Code - Customer (ESA) Improved term definitions: **Deactivated function** - Supplier (the company developing the chip or IP) DEVICE Design for test **DEVICE** database FPGA or ASIC technology providers (CAD tools, **Design** iteration Design Kits and libraries, IP Cores) **DEVICE** model (DEVICE) development flow ASIC manufacturers (masks, wafers, packaging) **FPGA** Programming Test (DEVICE) technology Phase HDL model Processing unit **IP** Core Production test Annex L in E-ST-20-40 Macrocell Prototype Equivalence of phase and milestone Software Netlist terminology of M-ST-10 and E-20-40 Synthesis tool Redesign System requirement Unreachable function Validation Verification

#### 🔜 📕 🚍 🚍 🖛 🕂 📲 🧮 🔚 📕 🖉 📲 🚝 🚝 🚛 🔯 🍉 📕 💥 📲 🛨 📰 📾 🕍 🔸 🕂 HE EUROPEAN SPACE AGENCY

## **New development flow figures**

#### → THE EUROPEAN SPACE AGENCY

\*

÷.

# Summary of name differences of phases and reviews

→ THE EUROPEAN SPACE AGENCY

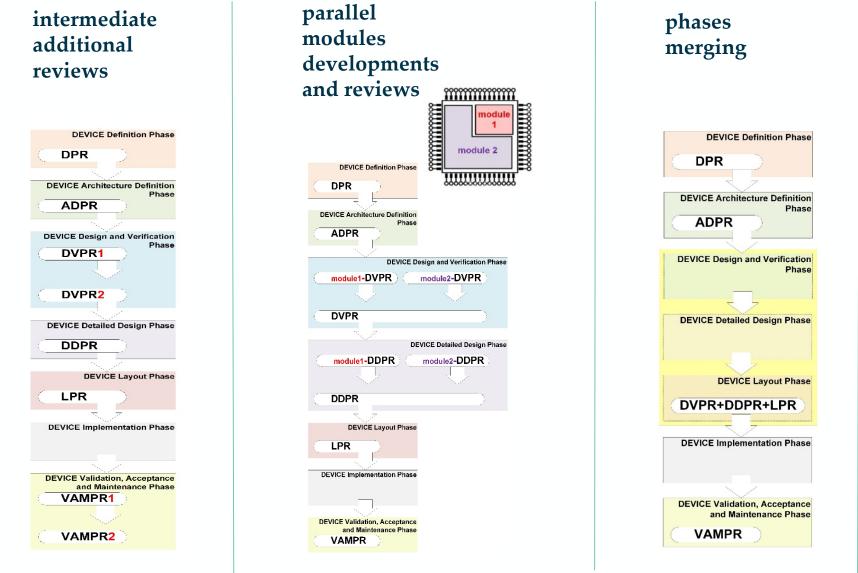

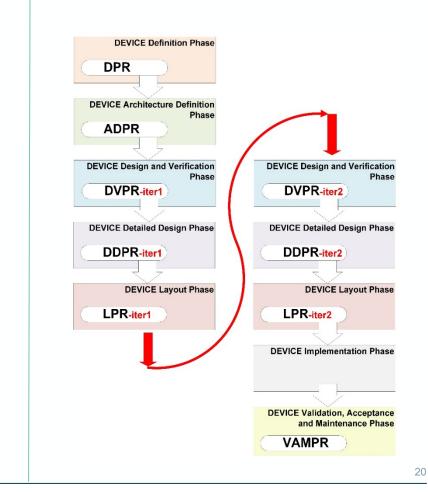

# development flow variations ECSS-E-ST-20-40 (2022)

+

\*

iterations of phases

<u>Two main **DEVICE criticality categories** (based on criticality categories defined in ECSS-Q-ST-30 Dependability clause 5.4, also used in ECSS-Q-ST-80 Software PA):</u>

- A or B or C criticality (catastrophic, loss of mission or major effects)

-> all requirements apply

- D criticality (minor effects) -> some requirements are waived or made lighter (e.g. less or no documentation requested)

# **Pre-tailoring table in new chapter 6**

| The same table indicates tailoring per DEVICE typ | е |

|---------------------------------------------------|---|

| and criticality                                   |   |

Approximately **20%** of all requirements are waived or relaxed for **category D** DEVICES (all R&D developments, minor impact to the mission where DEVICE will fly)

| ECSS Source ID | Requirement main text                                                                                                                                                                        | Requirement NOTES                                                                   | ECSS Object Type | Digital<br>ASIC | Analog ASIC | FPGA | IP Core | CRITICALITY<br>Category D (minor<br>consequences in case<br>of failure) |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|-----------------|-------------|------|---------|-------------------------------------------------------------------------|

| 4.3.4.2i       | Development team, companies involved (designers, foundry,<br>subcontractors, suppliers), indicating technical and administrative<br>interfaces, and clear assignment of tasks. [ALL]         |                                                                                     | Requirement      | yes             | yes         | yes  | yes     | yes                                                                     |

| 4.3.4.2j       | The development methodology of any subcontractors in charge of developing any of the Building Blocks for the DEVICE shall be ascertained by the supplier and agreed with the customer. [ALL] | NOTE For example, whether deviations or tailoring to this standard will be applied. | Requirement      | yes             | yes         | yes  | yes     | no                                                                      |

| 4.7.2c | The core and IO-pad ring power distribution shall be generated.<br>[D-ASIC, A-ASIC,,] | Requirement | yes | yes | no | no | yes                             |

|--------|---------------------------------------------------------------------------------------|-------------|-----|-----|----|----|---------------------------------|

| 4.7.2d | Test pads, if needed, shall be generated. [D-ASIC, A-ASIC,,]                          | Requirement | yes | yes | no | no | partial (no report<br>required) |

# **Distribution of requirements per DEVICE type**

|        | NUMB<br>REMEN |      |         | 272 |     | 20% fewer "engineering" requirements                                                                      |

|--------|---------------|------|---------|-----|-----|-----------------------------------------------------------------------------------------------------------|

| D-ASIC | A-ASIC        | FPGA | IP Core |     |     | than in the old standard which has 333<br>"engineering" requirements                                      |

| x      | x             | X    | x       | 201 | 74% |                                                                                                           |

|        | x             |      |         | 4   |     | 23                                                                                                        |

| X      |               | Х    | x       | 8   |     | "conditional" requirements                                                                                |

| X      | x             |      |         | 13  |     | (start with " <b>If</b> ")                                                                                |

| X      | X             | Х    |         | 20  |     | to be discussed and agreed between customer<br>and supplier at the beginning of the DEVICE<br>development |

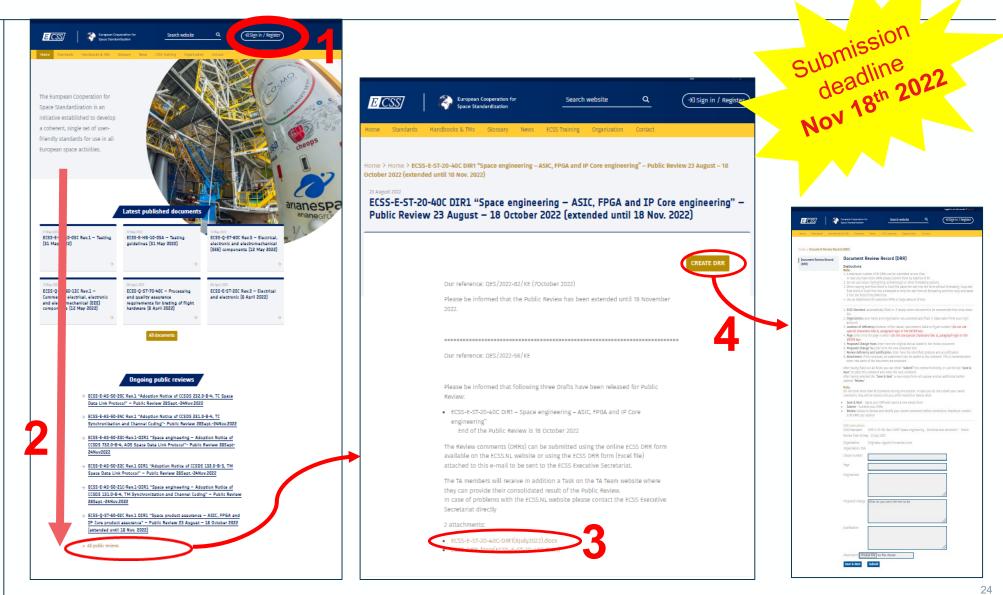

### How to create Change Requests for ECSS standards in Public Review

- 1. <u>https://ecss.nl/</u> : register and sign in

- 2. scroll down to find all "Ongoing public reviews" and select

- 3. read the standard

- 4. open the "Document Review Record" to create and submit a change request following the instructions

# **THANKS** for your attention,

**QUESTIONS?**

ad-hoc info sessions for industry to get to know the new ASIC/FPGA/IP E and Q standards can be organized on demand agustin.fernandez-leon[at]esa.int

# **Backup slides**

🗏 🔜 📲 🚍 💳 🕂 📲 🏣 🔚 🖳 📲 🔚 🔤 🚛 🚱 🛌 🚳 🎽 👫 📲 🛨 📰 📾 🏣 👾 🛛 🕇 the European space Agency

- There were no requirements specific to HW-SW co-engineering in "old" std

- Definition of "software" and "processing unit" added

- Improvements to definitions of "IP Cores" and "building block" that can help to the better handling of "processing units" used or put inside the DEVICE

- Several new requirements interaction between HW and SW design teams (outputs/inputs exchanged, scheduled milestones)

- Several new requirements on:

- **tailored development flow variations** (phases/reviews merging, individual modules parallel flows, additional intermediate reviews, iterations if appropriate and agreed with customer) at the beginning

- interaction between digital and analog design teams (outputs/inputs exchanged, scheduled milestones)

- subcontracted design work to third parties, their design methodology and compliance to the ECSS standard

- development and use of **Analog IP Cores**

- Several "old" requirements specific to A/MS ASICs revised and improved by WG analog experts in dedicated WG meetings

[ACTION for AMICSA 20XX attendees] All experts, future users of the new standards, are kindly invited to help optimize the new standard, by reading the draft once it is published for ECSS **public review**, and submitting Change Requests

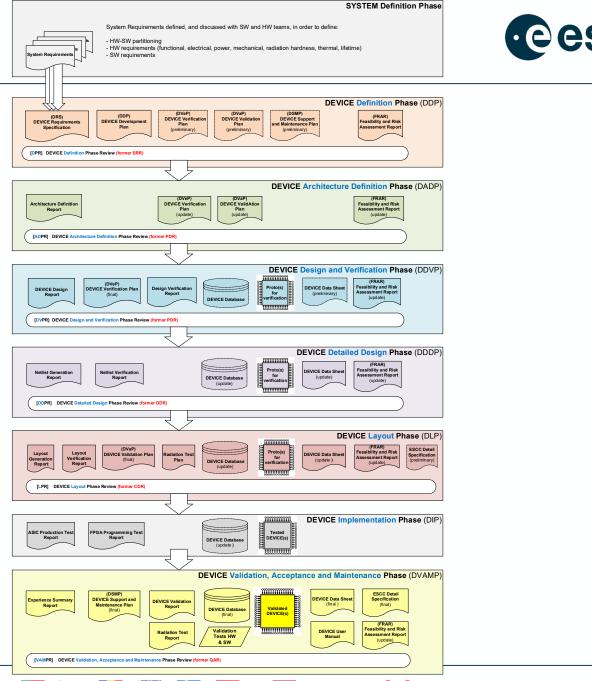

# Phases, reviews, expected outputs

# Generic development flow

30

eesa

## phases, reviews and outputs

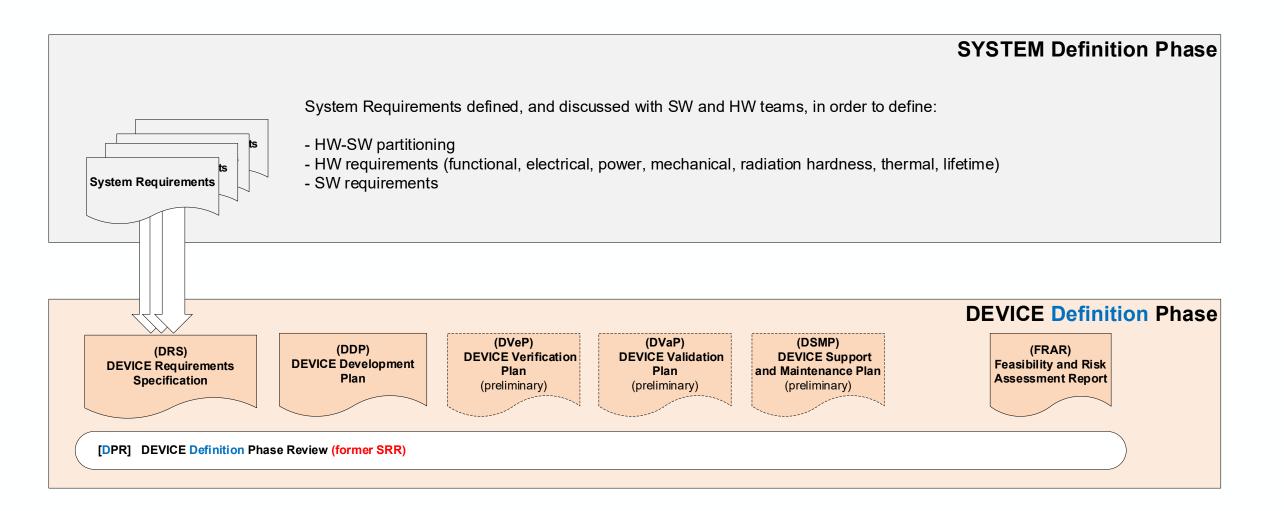

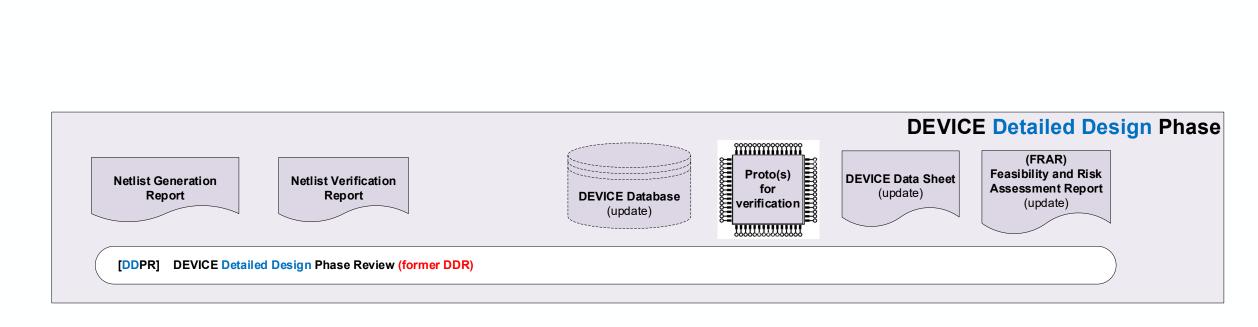

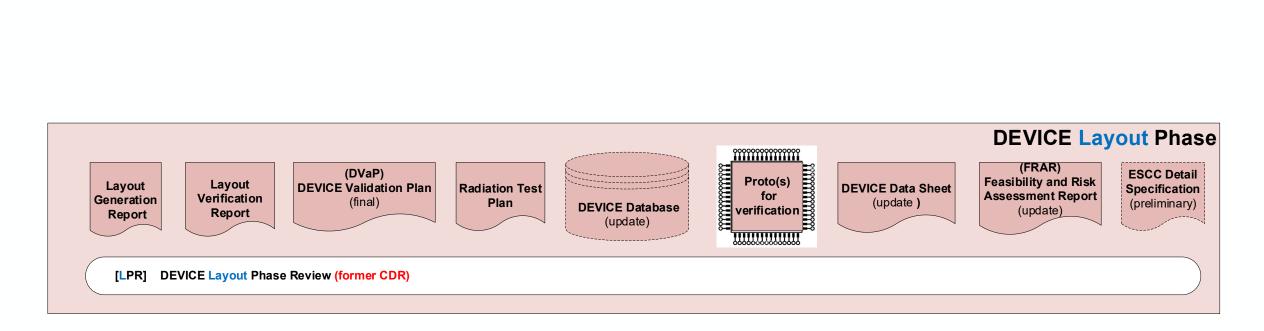

NEW PHASES + NEW REVIEWS resulting from splitting former "Architectural Design phase" into two phases !

### phases, reviews and outputs

## phases, reviews and outputs

#### ■ Section 1 and 1

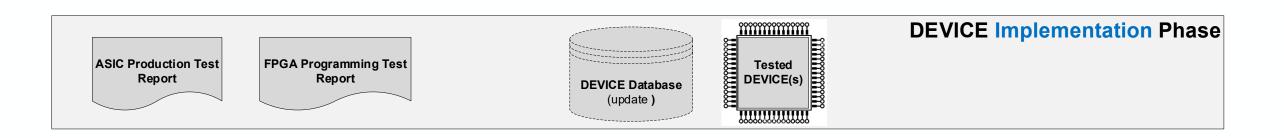

former "Prototype implementation phase"

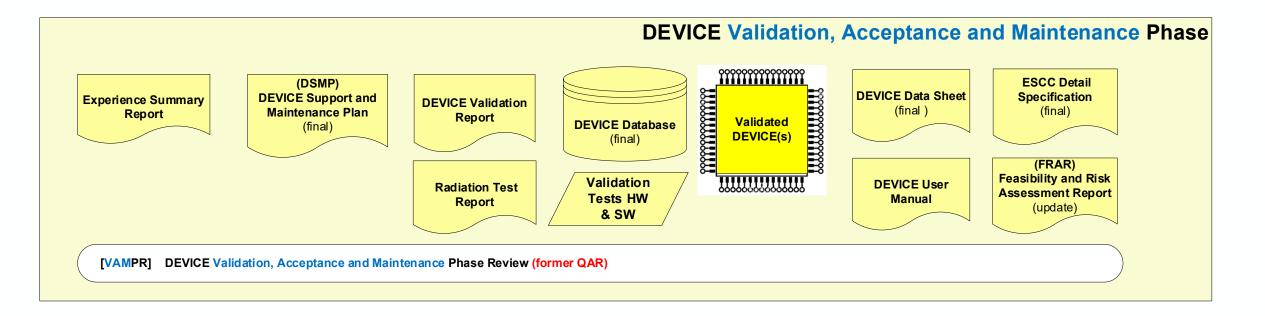

former "Design Validation and Release phase"

\*

# Name differences of phases, reviews and outputs

| E                | CSS-Q-ST                                         | <b>F-60-02C (2008)</b>                                                                                                                                                       | ECSS-E-ST-20-                                                                                                                                                                                                                                                                                                                                                                 | 40C (202                                                       | 2)                                                                 |

|------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------|

| phases           | reviews                                          | outputs                                                                                                                                                                      | outputs                                                                                                                                                                                                                                                                                                                                                                       | reviews                                                        | phases                                                             |

| Definition phase | System<br>Requirements<br>Review<br><b>(SRR)</b> | <ol> <li>ASIC and FPGA requirements<br/>specification (ARS);</li> <li>Feasibility and risk analysis<br/>(FRA);</li> <li>ASIC and FPGA development plan<br/>(ADP);</li> </ol> | <ul> <li>a) DEVICE Requirements Specification<br/>(DRS)</li> <li>b) Feasibility and Risk Assessment<br/>Report (FRAR)</li> <li>c) DEVICE Development Plan (DDP)</li> <li>d) DEVICE Verification Plan (DVeP)<br/>(preliminary)</li> <li>e) DEVICE Validation Plan (DVaP)<br/>(preliminary)</li> <li>f) DEVICE Support and Maintenance<br/>Plan (DSMP) (preliminary)</li> </ul> | DEVICE<br>Definition<br>Phase Review<br>(DPR)                  | <b>DEVICE</b><br><b>Definition</b><br>Phase                        |

| Architectural    | Preliminary<br>Design Review                     | a. Architecture definition report;<br>b. Verification plan;<br>c. Architecture verification and<br>optimization report;                                                      | <ul> <li>a) Architecture Definition Report (ADR)</li> <li>b) DEVICE Verification plan (update)</li> <li>c) DEVICE Validation Plan (update)</li> <li>d) FRAR (update)</li> </ul>                                                                                                                                                                                               | DEVICE<br>Architecture<br>Definition<br>Phase Review<br>(ADPR) | <b>DEVICE</b><br>Architecture<br><b>Definition</b><br>Phase        |

| design           | (PDR)                                            | d. Preliminary data sheet;<br>e. Design database, containing:<br>1. Simulation models;<br>2. Verification results;<br>f. MoM of PDR.                                         | <ul> <li>a) DEVICE Verification Plan (final)</li> <li>b) Architectural Design Report</li> <li>c) Design Verification Report</li> <li>d) Data Sheet (DS) (preliminary)</li> <li>e) DEVICE database</li> <li>f) FRAR (update)</li> </ul>                                                                                                                                        | DEVICE<br>Design and<br>Verification<br>Phase Review<br>(DVPR) | <b>DEVICE</b><br><b>Design and</b><br><b>Verification</b><br>Phase |

#### → THE EUROPEAN SPACE AGENCY

\*

# Name differences of phases, reviews and outputs

| <br>-           | ECSS-Q-S                           | T-60-02C (2008)                                                                                                                                                                                                  | ECSS-E-ST-20-                                                                                                                                                                                                                                                                                         | 40C (2022                                              | 2)                                               |

|-----------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------|

| phases          | reviews                            | outputs                                                                                                                                                                                                          | outputs                                                                                                                                                                                                                                                                                               | reviews                                                | phases                                           |

| Detailed design | Detailed Design<br>Review<br>(DDR) | <ol> <li>Pre-layout netlist;</li> <li>Constraints for layout (i.e.<br/>floorplan and constraints for</li> </ol>                                                                                                  | a) Netlist Generation Report<br>b) Netlist Verification Report<br>c) DEVICE Data Sheet (update)<br>d) DEVICE Database (update)                                                                                                                                                                        | DEVICE<br>Detailed<br>Design Phase<br>Review<br>(DDPR) | <b>DEVICE</b><br><b>Detailed Design</b><br>Phase |

| Layout          | Critical Design<br>Review<br>(CDR) | d. Updated data sheet;<br>e. Updated design database, containing:<br>1. Post-layout netlist in the<br>agreed format depending on the<br>targeted technological approach<br>(GDS II, FPGA P&R files or<br>other): | <ul> <li>a) Layout Generation Report</li> <li>b) Layout Verification Report</li> <li>c) DEVICE Validation Plan (final)</li> <li>d) Radiation Test Plan</li> <li>e) DEVICE Data Sheet (update)</li> <li>f) ESCC Detail Specification<br/>(preliminary)</li> <li>g) DEVICE database (update)</li> </ul> | DEVICE<br>Layout<br>Phase Review<br>(LPR)              | <b>DEVICE</b><br>Layout<br>Phase                 |

# Name differences of phases, reviews and outputs

| ECSS-Q-ST-60-02C (2008)             |                                                    |                                                                                                                                                                                                                                                                                                                                                                                             | ECSS-E-ST-20                                                                                                                                                                                                                                                                                                                                                        | -40C (2022                                                                        | :)                                                              |

|-------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------|

| phases                              | reviews                                            | outputs                                                                                                                                                                                                                                                                                                                                                                                     | outputs                                                                                                                                                                                                                                                                                                                                                             | reviews                                                                           | phases                                                          |

| Prototype<br>implementation         | n/a                                                | <ul> <li>a. Agreed number of tested devices</li> <li>(ASICs or FPGAs);</li> <li>b. Production test results and reports;</li> <li>[not applicable for FPGA designs];</li> <li>c. Burn-in or any other production test results, specifications and patterns.</li> </ul>                                                                                                                       | <ul> <li>a) Agreed number of tested<br/>DEVICES</li> <li>b) Production Test Report</li> <li>c) FPGA Programming Tests Report</li> <li>d) DEVICE database (update)</li> </ul>                                                                                                                                                                                        | n/a                                                                               | DEVICE<br>Implementation<br>Phase                               |

| Design<br>validation and<br>release | Qualification snf<br>Acceptance<br>Review<br>(QAR) | <ul> <li>a. Validation report;</li> <li>b. Radiation test report (if applicable);</li> <li>c. Release report;</li> <li>d. Experience summary report;</li> <li>e. Final data sheet;</li> <li>f. Final detail specification;</li> <li>g. Application note;</li> <li>h. MoM of QR/AR;</li> <li>i. Validation breadboard;</li> <li>j. Burn-in or screening test boards for FM parts.</li> </ul> | <ul> <li>a) DEVICE Validation Report</li> <li>b) Radiation Test Report</li> <li>c) Agreed number of validated<br/>DEVICES</li> <li>d) DEVICE Support and<br/>Maintenance Plan (final)</li> <li>e) Experience Summary Report<br/>(ESR)</li> <li>f) DEVICE Data Sheet (final)</li> <li>g) ESCC Detail Specification (final)</li> <li>h) DEVICE User Manual</li> </ul> | DEVICE<br>Validation,<br>Acceptance and<br>Maintenance<br>Phase Review<br>(VAMPR) | DEVICE<br>Validation,<br>Acceptance and<br>Maintenance<br>Phase |

**Four DEVICE types** (tags next to each requirement indicate applicability as explained in "Conventions" 3.4 section of ECSS-E-ST-20-40):

- D-ASIC: applicable to fully digital ASICs, or the digital part of mixedsignal ASICs

- A-ASIC: applicable to fully analog ASICs, or the analog part of mixed-signal ASICs

- **FPGA**: applicable to FPGAs

- IP: applicable to digital or analog IP Cores

#### 💳 🔜 📲 🚍 💳 🛶 📲 🔚 🔚 🔚 📰 📲 🔚 🚛 🖓 🛌 📲 🗮 🖛 🖓

# ECSS-Q-ST-60-02C Rev.1 : some content highlights Cesa

- ECSS-Q-ST-60-02C Rev.1 explicitly defines PA requirements from ECSS-Q-ST-60-02C in line with ECSS-Q-ST-10/20/30 -> no new requirements wrt ECSS-Q-ST-10/20/30 since ECSS-Q-ST-60-02C

- **New requirements** in ECSS-Q-ST-60-02C Rev.1 cover:

- <u>Tailoring by criticality (in line with ECSS-Q-ST-30/40)</u>, i.e. in line with <u>severity of the consequence of DEVICE failure</u>

- Alignment to <u>reviews definition</u> in ECS-E-ST-20-40

- Alignment to verification/validation activities defined in ECSS-E-ST-20-40

- Security Assurance

- <u>Reuse</u>: engineering, verification, legal (licence, IPR) requirements

- Definition of deactivated and unreachable DEVICE functions

- Definition of <u>Metrication programme</u> requirements

- <u>IVV</u> Independent Verification Validation by Third Party for criticality A and B

- Qualification status assessment and maintenance, in line with ECSS-M-ST-10 and ECSS-Q-ST-20

- Process assessment and improvement