## Microchip Radiation Tolerant FPGAs

A Leading Provider of Smart, Connected and Secure Embedded Control Solutions

Tim Morin March 15, 2023

### Agenda

### Quick Product Update

- RT PolarFire<sup>®</sup> FPGA

- RTG4<sup>™</sup> FPGA

### Microchip and RISC-V – The Road Less Traveled

### **Microchip FPGA Vision and Differentiation**

# To enable innovation by offering the most power-efficient programmable solutions

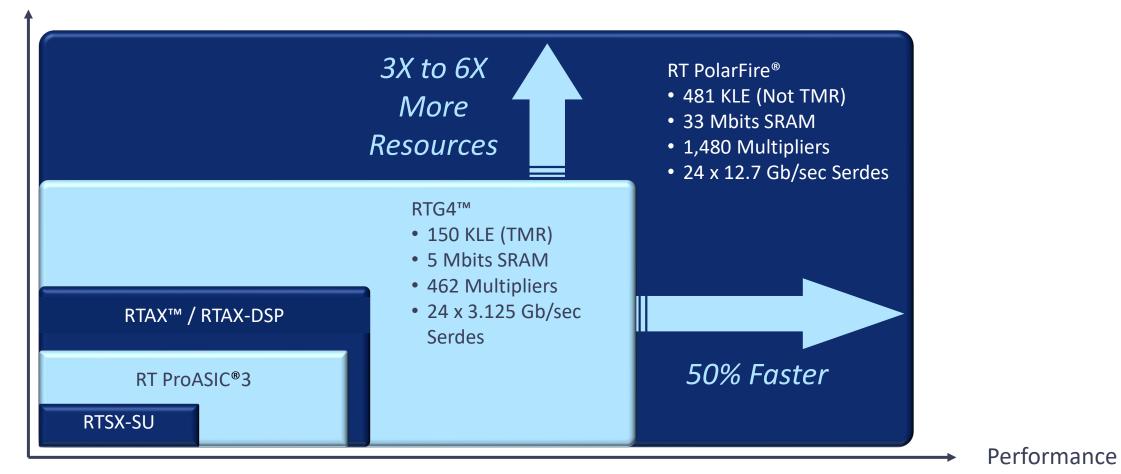

### **RT FPGA Families**

#### Logic Density

# **RT PolarFire<sup>®</sup> FPGA Overview**

### Two versions

- RTPF500T

- RTPF500ZT

### Both derived from commercial PolarFire

- 28 nm SONOS: Non-volatile and reprogrammable

- Hermetically sealed, ceramic column grid array package

- 1509 solder columns (Six Sigma copper spiral columns)

- Robust TID, 100 krad

- No configuration upsets

- LET 80 MeV-cm<sup>2</sup>/mg, fluence more than 5E<sup>8</sup> ions/cm<sup>2</sup>

- SEFI in reset circuit

- 1 in 187 years, in GEO solar min

### • RTPF500ZT has enhanced capabilities

- Better SEL GPIO Performance

- Better on-orbit programming methodology

### **RTPF500T Status**

### Qualification and availability schedule

- Engineering models, PolarFire dev kit–Available NOW

- <u>RT PolarFire dev kit</u> with RTPF500<del>T</del>Expected May 2023

- MIL-STD-883Bqualification for RTPF500T completed

- B-flowand E-flowflight models available to lead times

### **RTPF500T/RTPF500ZT Radiation Summary** Fabric Flops / LSRAM

• SEU in flip-flops report

| SEU                  | Errors /bit-day, Geo Solar Min |                     |  |  |  |

|----------------------|--------------------------------|---------------------|--|--|--|

|                      | Fabric Flip Flops              | Fabric LSRAM        |  |  |  |

| Unprotected          | ~ 1e <sup>-7</sup>             | ~ 5e <sup>-8</sup>  |  |  |  |

| Protected (TMR/EDAC) | ~ 1e <sup>-11</sup>            | ~ 5e <sup>-15</sup> |  |  |  |

Flip Flops : TMR with constrained placement

LSRAM : EDAC (SECDED)

### **RTPF500T/RTPF500ZT Radiation Summary** GPIO SEL

| GPIO V <sub>DDI</sub> | GPIO V <sub>DDAUX</sub> | RTPF500T<br>SEL LET <sub>тн</sub> (MeV.cm²/mg) | RTPF500ZT<br>SEL LET <sub>TH</sub> (MeV.cm <sup>2</sup> /mg) |

|-----------------------|-------------------------|------------------------------------------------|--------------------------------------------------------------|

| 3.3V +3%/-5%          | 3.3V +3%/-5%            | 25*                                            | 37**                                                         |

| 2.5V +3%/-5%          | 2.5V +3%/-5%            | 58                                             | 80                                                           |

| 1.8V ±5%              | 2.5V +3%/-5%            | 58***                                          | 80****                                                       |

#### Notes:

\* Destructive SEL observed in RTPF500T 3.3V at LET > 25 MeV.cm<sup>2</sup>/mg

\*\* Destructive SEL observed in RTPF500ZT 3.3V at LET 68 MeV.cm<sup>2</sup>/mg

\*\*\* Tested MPFS250T and savSEL at LET=66, but since the LET<sub>th</sub>=58 at 2.625V, LET<sub>th</sub> should be equal or better at 1.89V

\*\*\*\* Not tested, but sinceve meet LET=80 at 2.625V, ve should meet LET=80 at 1.89V

No other destructive SEL observed unless board decoupling capacitor requirements are not followed. No uSEL observed on (VDD25/VDDA25) on RTPF500ZT

No SEL observed on HSIO

### **RTPF500T vs RTPF500ZT**

|                         |                                                                     | RTPF500T                                      | RTPF500ZT                                                                          |

|-------------------------|---------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------|

| Part numbers start with |                                                                     | RTPF500T, RTPF500TL, RTPF500TS,<br>RTPF500TLS | RTPF500 <b>Z</b> T, RTPF500 <b>Z</b> TL, RTPF500 <b>Z</b> TS, RTPF500 <b>Z</b> TLS |

| Packaging               | CG1509, LG1509                                                      | Compatible                                    | Compatible                                                                         |

|                         | Engineering Models                                                  | Nov                                           | 1H 2024                                                                            |

| Availability            | Mil Std 883 Class B Flight Models                                   | Nov                                           | 2H 2024                                                                            |

| Qualification           | QML Class Q Flight Models                                           | 1H 2023                                       | 2H 2024                                                                            |

|                         | QML Class V Flight Models                                           | Not Planned                                   | 2025                                                                               |

| System Services         | JTAG and SPI-Target In-Flight<br>Programming                        | Supported                                     | Supported                                                                          |

|                         | SPI-Initiator In-Flight Programming                                 | Not Supported                                 | Support Planned *                                                                  |

|                         | System Services on Temporary Exit of System Controller Suspend Mode | Not Supported                                 | Support Planned *                                                                  |

\* Pending testing and validation

# RTG4<sup>™</sup> FPGA

## **<u>RTG4</u><sup>™</sup> FPGA** Qualification and Availability

|                            | RT4G150-<br>LG1657               | RT4G150-<br>CB1657        | RT4G150-<br>CG1657               | RT4G150-<br>CQ352                | RT4G150-<br>FC1657, FCG1657 |

|----------------------------|----------------------------------|---------------------------|----------------------------------|----------------------------------|-----------------------------|

| Package Type               | Ceramic Land<br>Grid 1657        | Ceramic Ball<br>Grid 1657 | Ceramic Column<br>Grid 1657      | Ceramic Quad<br>Flat Pack 352    | Plastic Ball<br>Grid 1657   |

| Development Kit            | -                                | Available Today           | Available Today                  | -                                | -                           |

| Daisy Chain                | -                                | -                         | Available Today                  | -                                | Available Today             |

| Mechanical Sample          | -                                | -                         | -                                | Available Today                  | -                           |

| PROTO                      | Available Today                  | Available Today           | Available Today                  | Available Today                  | Available Today             |

| Flight Units – QML Q and V | Available Today<br>SMD Published | -                         | Available Today<br>SMD Published | Available Today<br>SMD Published | -                           |

| Flight Units – Sub-QML     | Available Today                  | -                         | Available Today                  | Available Today                  | Available Today             |

## **RTG4<sup>™</sup> FPGA Screening Flows**

| Flow           | Purpose                          | Package                                                | Qualification          | Screening         |                  |                    |          |

|----------------|----------------------------------|--------------------------------------------------------|------------------------|-------------------|------------------|--------------------|----------|

| 11000          |                                  |                                                        |                        | Burn-In           | Temp Test        | Life Test          | DPA      |

| V              | NSS, NASA Class1                 | Hermetic Ceramic                                       | QML-V                  | Static<br>Dynamic | -55°C –<br>125°C | Wafer-Lot          | Assy Lot |

| E              | Advanced<br>Traditional Space    | Hermetic Ceramic                                       | QML-Q                  | Static<br>Dynamic | -55°C –<br>125°C | Generic<br>Group C | Optional |

| В              | Entry Level<br>Traditional Space | Hermetic Ceramic                                       | QML-Q                  | Dynamic           | -55°C –<br>125°C | Generic<br>Group C | None     |

| R              | New Space,<br>Strategic Programs | Hermetic Ceramic                                       | MIL-STD-883<br>Class B | Dynamic           | -55°C –<br>125°C | None               | None     |

| Mil<br>Ceramic | New Space,<br>Strategic Programs | Hermetic Ceramic                                       | MIL-STD-883<br>Class B | None              | -55°C –<br>125°C | None               | None     |

| Mil<br>Plastic | New Space,<br>Strategic Programs | Plastic<br>Non-Hermetic                                | JEDEC                  | None              | -55°C –<br>125°C | None               | None     |

| PROTO          | Prototyping                      | Plastic and<br>Ceramic (Hermeticity<br>not guaranteed) | None                   | None              | -55°C –<br>125°C | None               | None     |

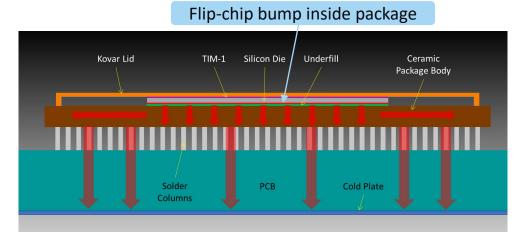

### **RTG4™ FPGA Flip-chip Bump Change (1)**

#### Background

- Leaded flip-chip bump materialwas discontinued by Microchip vendor

- Impacting all RTG4 in ceramic packages (CG1657 and CQ352) in all screening flows

- RTG4 in plastic package and RT PolarFire are NOT impacted. They always use lead-free bump

#### • Plans

- Issued RTG4 flip-chip bump customer notification

- 2. Qualifying RTG4 lead-free bump parts

- Mil-Std-883Bqualification—expected 2H 2023

- QML-Qqualification–expected 2H 2023

- QML-Vqualification—expected 1H 2024

### **RTG4™ FPGA Flip-chip Bump Change (2)**

#### Customer notification

- Microchip PCN JAON-26GOCS315 released in November 2022

- GIDEP SC7-C-23-0001 acknowledged

#### Important timelines for leaded-bump RTG4

- Last Time Buy (LTB): April 2023

- Last Time Ship (LTS): April 2024

#### Replacement parts with lead-free bump

- All standard RT4G150 parts in CG1657 and CQ352 have equivalent replacement lead-free bump part

- Ex: RT4G150-CGG1657B, RT4G150-CQG352B

- **G** references lead-free flip-chip bump for RTG4 FPGA family

- No change to the Six Sigma columns which have lead content

- No design impact when migrating to replacement parts

- No change in board design, reflowprofile, board assembly flowor software setting

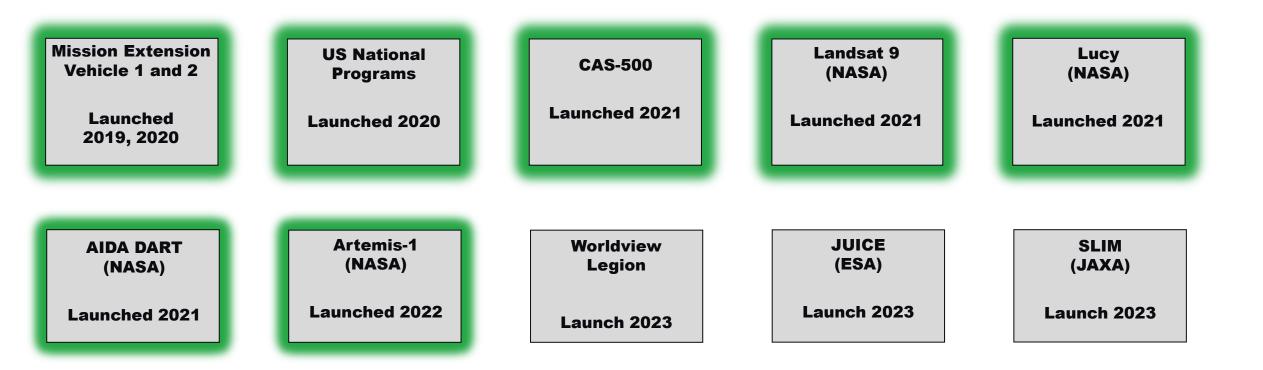

## **RTG4<sup>™</sup> FPGA Flight Heritage**

# **RT Update Conclusion**

### RT PolarFire<sup>®</sup> FPGAs

- MIL-STD-883Bqualification for RTPF500T completed

- RTPF500ZT has improved radiation performance, added system services and a path to QML-Vqualification

### • RTG4™ FPGAs

- Leaded bump last-time-buy is April 2023

- Ongoing lead-free bumpqualification, anticipating MIL-STD-883B and QML-Q in 2023

- Microchip Space Forum

- Free virtual on-demand presentations available now

Sign up for Microchip Space Brief newsletter to receive quarterly updates

### Microchip RISC-V Road Trip or The Road Less Traveled

A Leading Provider of Smart, Connected and Secure Embedded Control Solutions

**Tim Morin**

# June 2015 2<sup>nd</sup> RISC-V Workshop Berkeley California

### **The Road Trip**

The Opportunity

When you come to a fork in the road take it

The Road Trip

The Decision

What's around the corner?

### **The Opportunity**

- A&D client building an assembly for a strategic platform

- Needs a soft CPU with Cache

What could gowong?

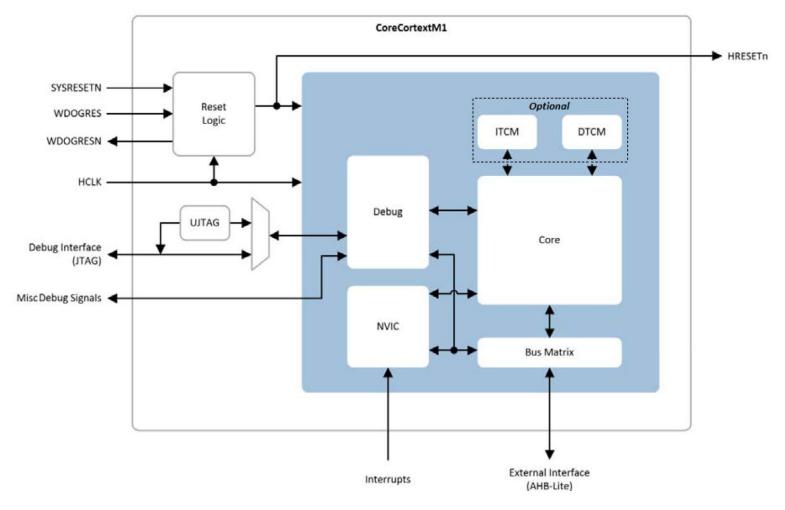

### **ARM Cortex-M1**

### Jointly developed between Actel and ARM in 2006

Unfortunately, no Cache

### We get into the Soft RISC-V Business

- 1-page requirements document

- \$ was exchanged

- 3 months later the client was up and running with some basic code

#### Soft RISC-V Platform RFI

Microsemi Soc Business unit is requesting a quote for the delivery of the following items.

- RISC-V RV321M core with the following features

- o hardware divide and optional barrel shifter

- Integrated Cache controller

- Interrupt controller

- o Debug environment

- o Cacheable and non-cacheable software defined memory regions

- Software Enable/Disable I cache

- Enable Software /Disable D Cache

- Software Flush I cache

- Software Flush D cache

- o 8Kbyte Instruction and Data Cache

- >=1 DMIPS/ MHz

- AXI bus interface to main memory

- o AHB Bus interface to Peripherals

- o AHB Bus interface to Boot eNVM

- 32 interrupts, prioritized

- o RISCV Standard Hardware debug

- RISCV Standard watchpoints

- o 100MHz Operation on an M2S0090TS-FGG484 (Standard Speed Grade)

- A Uart for printf debug support

- A Timer for generating periodic interrupts

- C startup code for booting from internal eNVM in a M2S090TS-FGG484 device

- Test application software

- o Flushes Instruction and Data Caches and then enables them

- o Initializes and starts timers

- Timer 1: 10 ms countdown, with interrupt on expiration

- Timer 2: Free running counter

- Initializes and enables interrupts

- o Test code for cache operation

- sleep routines using free-running counter

- Receives and handles 10 ms timeout interrupts

- o Receive interrupts, determine the source and handle it, then return to main routine

- o Exception handling routines

- o <u>eNVM</u> flash read/erase/program

- GCC tool chain V4.7, V4.9 or later

- All Source code under a BSD license

- Documentation

**RISC-V** is about business innovation

### **Mi-V RISC-V Soft CPUs**

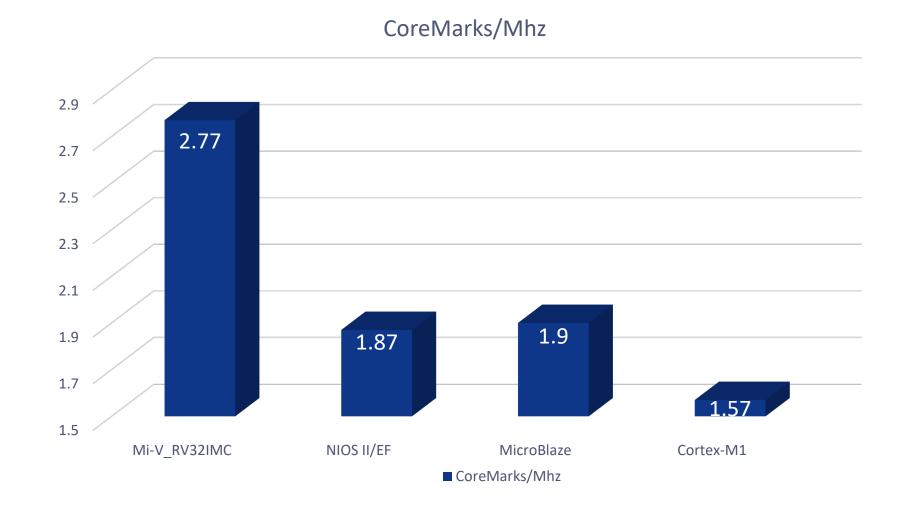

| RISC-V Soft CPU                 | <u>MiV_RV32</u>                                                | Mi-V_RV32IMAF_L1_AHB | Mi-V_RV32IMA_L1_AHB | Mi-V_RV32IMA_L1_AXI |

|---------------------------------|----------------------------------------------------------------|----------------------|---------------------|---------------------|

| LEs                             | 4k-10k                                                         | 26k                  | 10k                 | 10k                 |

| Coremark Score                  | 0.177-2.77                                                     | 2.01                 | 2.01                | 2.01                |

| Cache Size                      | Libero 2023.01                                                 | 8KB I/D              | 8KB I/D             | 8KB I/D             |

| Tightly Coupled Memory<br>(TCM) | Yes-configurable depth to 256Kb                                | N/A                  | N/A                 | N/A                 |

| Compressed                      | optional                                                       | N/A                  | N/A                 | N/A                 |

| Mul/Div                         | Optional, MACC,<br>Pipelined-MACC,<br>or 32 cycle fabric (LEs) | Yes                  | Yes                 | Yes                 |

| Atomics                         | N/A                                                            | Yes                  | Yes                 | Yes                 |

| Floating Point                  | Libero 2023.01                                                 | Single Precision     | N/A                 | N/A                 |

| Interface(s)                    | APB3/AHB/AXI                                                   | AHB                  | AHB                 | AXI                 |

| Debug                           | Optional                                                       | Yes                  | Yes                 | Yes                 |

| SECDED                          | Optional                                                       | Optional             | Optional            | N/A                 |

| Availability                    | Nov                                                            | Nov                  | Nov                 | Nov                 |

### **Benchmarks: Soft CPUs**

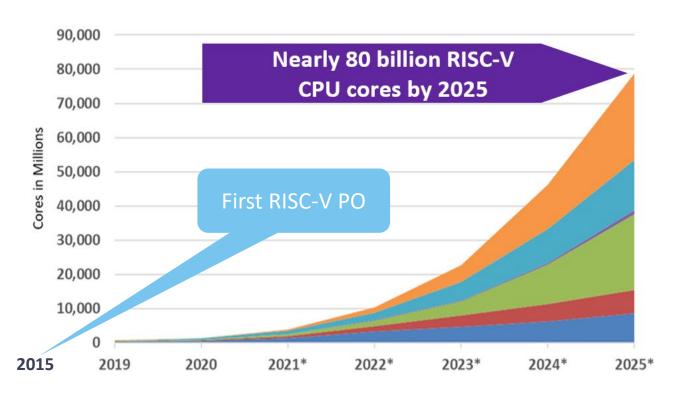

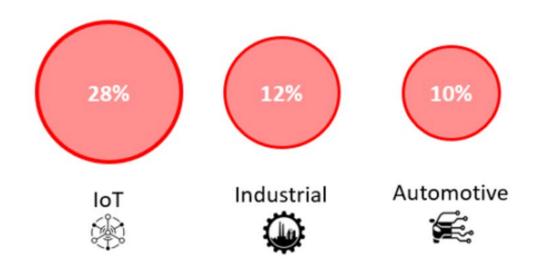

RISC-V CPU core market grows 114.9% CAGR, capturing >14% of all CPU cores by 2025

Computer Consumer Communications Transportation Industrial Other RISC-V

**RISC-V Penetration Rate by 2025**

"The rise of RISC-V cannot be ignored... RISC-V will shake up the \$8.6 Billion semiconductor IP market." -- William Li, Counterpoint Research

RISC-V°

Source: Counterpoint Research, September 2021

When you come to a fork in the road, take it Yogi Berra

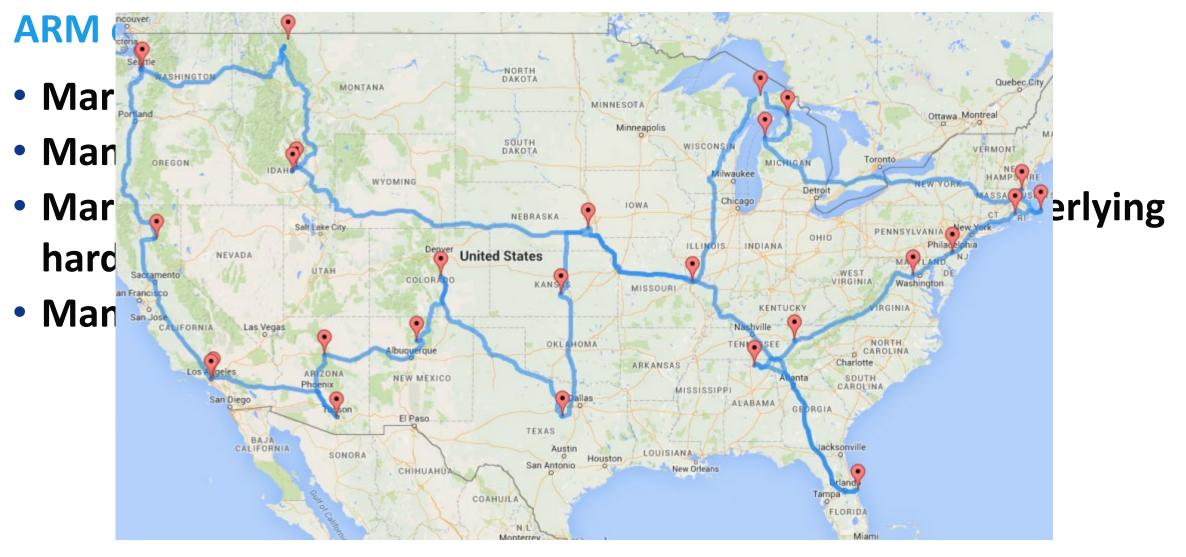

### **Our next SoC FPGA platform needs to run Linux**

# **The Road Trip**

Mission : bring back client validation to green light the next project

### Have you heard of RISC-V?

# But we use ARM!

### **Embedded Linux Adoption**

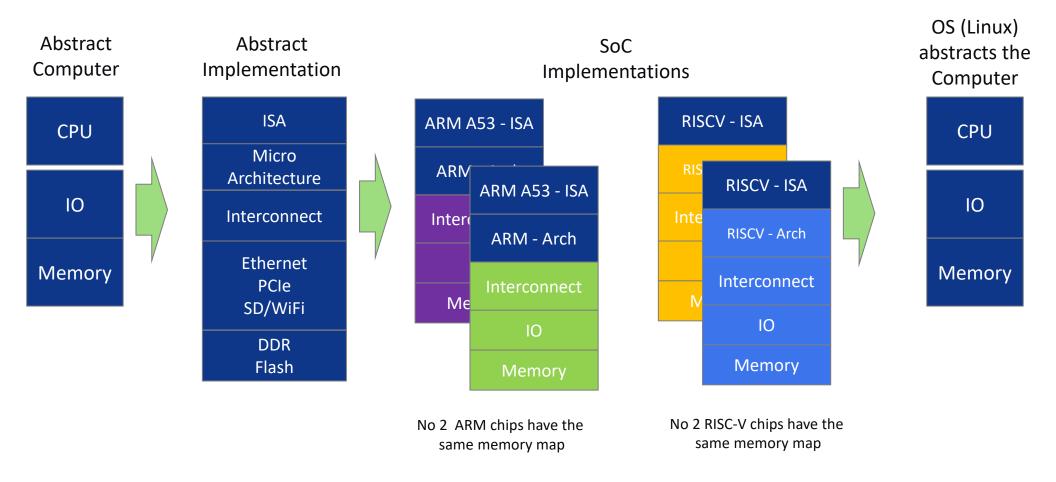

Fragmentation in the ARM ecosystem drove the creation of the Device Tree in Linux Making Linux even more portable

# **Diversity versus Fragmentation**

Fragmentation: Same thing done different ways

Diversity: Solving different problems

# **The Decision**

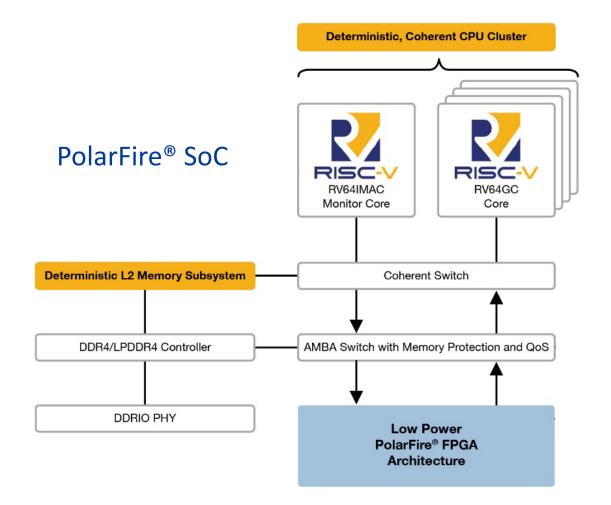

### **Enjoy Absolute Freedom to Innovate...**

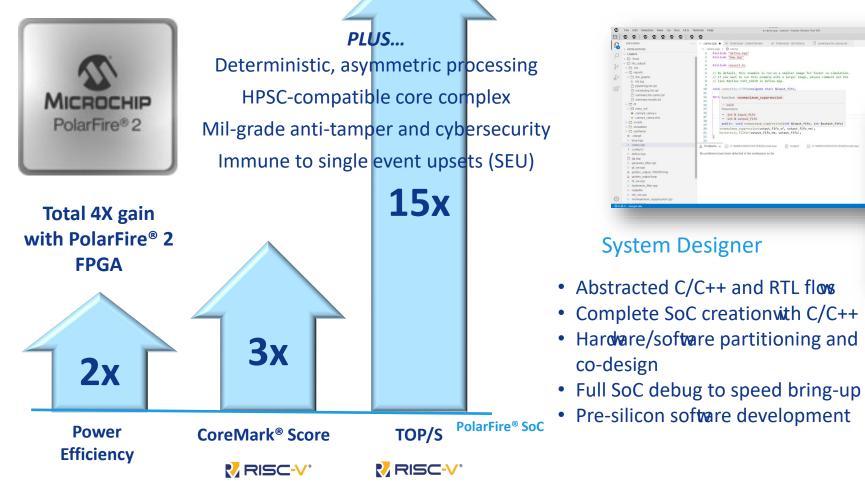

Asymmetric processing with 2X power efficiency Quad-core 64-bit RISC-V processors Linux<sup>®</sup> and Real-time operating systems Highly flexible 2MB L2 cache

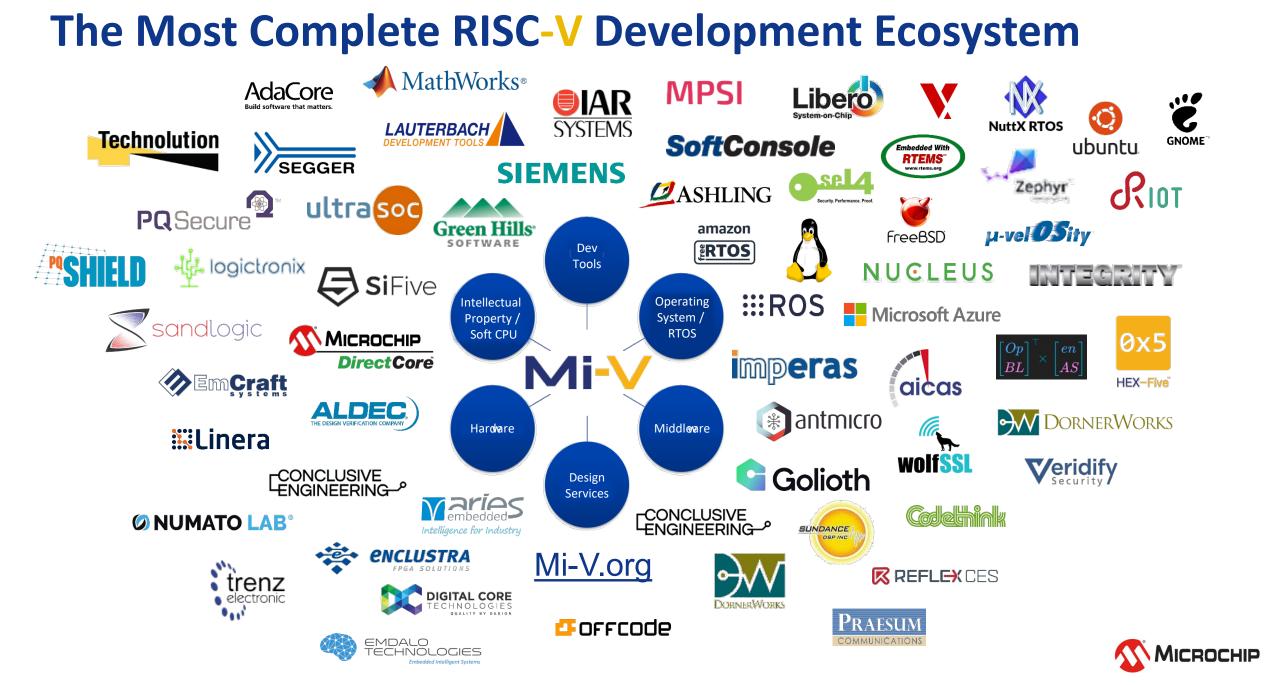

With the most comprehensive RISC-V development ecosystem

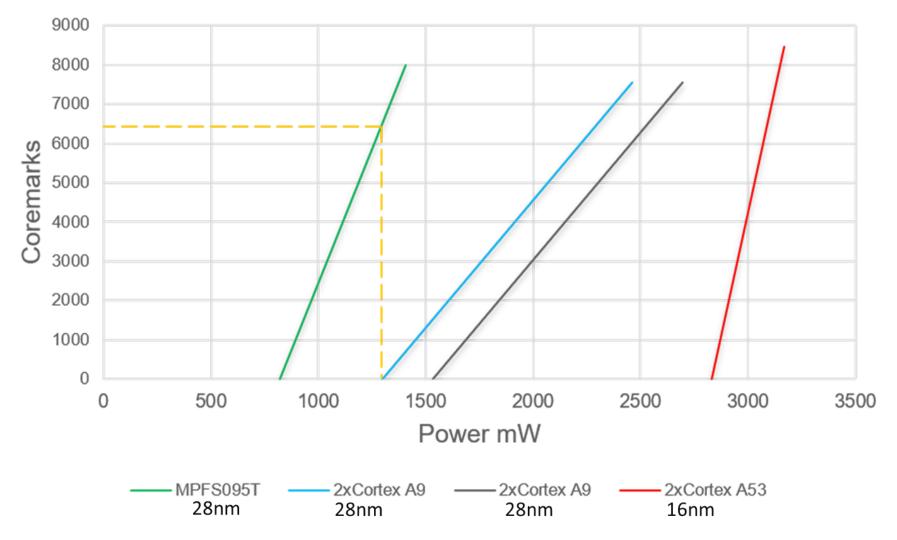

### PolarFire SoC has a 6K CoreMark head start! CoreMarks / W

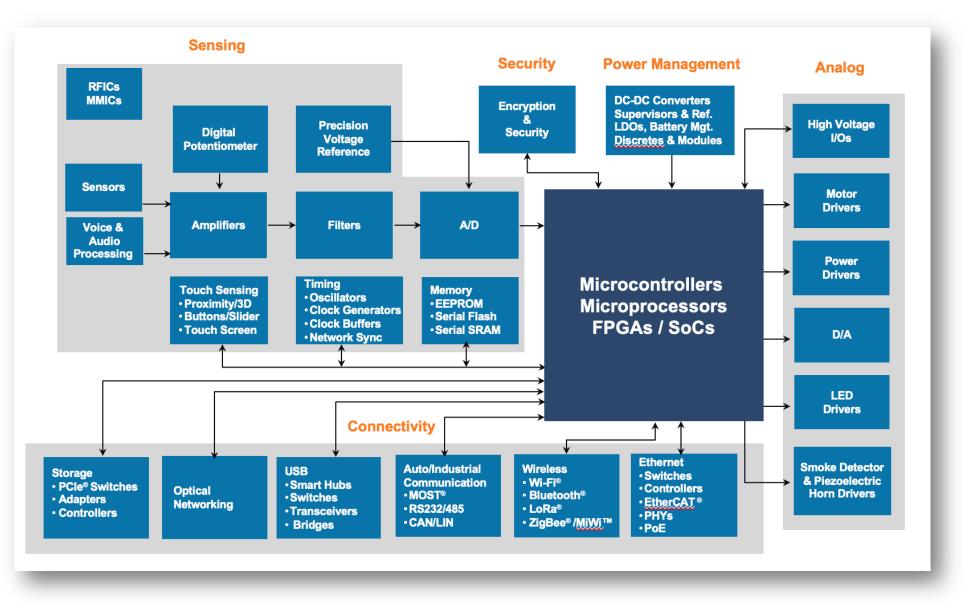

### Part of Microchip's Commitment to Total System Design

Devices Firmvare Softvare Tools Support

### What's around the corner?

# Next: The Second Generation of PolarFire<sup>®</sup> FPGAs

co-design

### We're Doubling Pover Efficiency... Again!

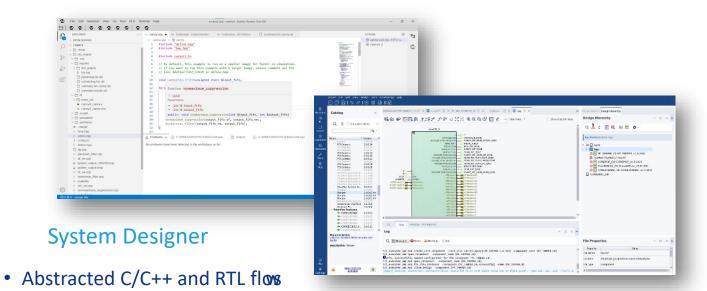

#### System-Level Design Gets Its Own Suite

#### **FPGA** Designer

- Modern and intuitive UI

- Fast timing closure

- Adaptive design flow

- Better IP handling and delivery ٠

- Faster simulation and expanded debug

### **Tuned for Power-Hungry 100G Edge Technologies**

### What's around the next corner?

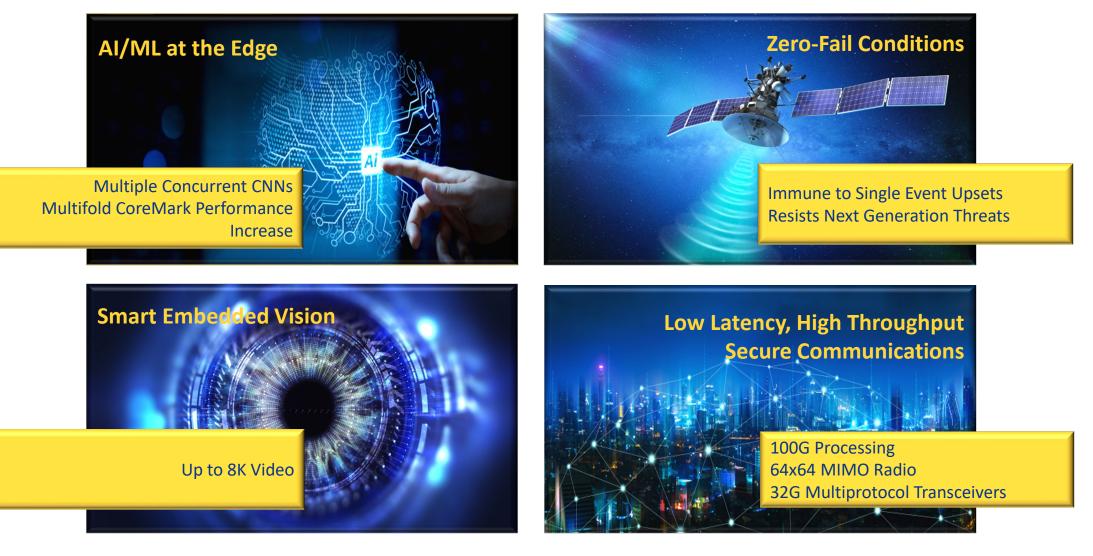

### HPSC is Critical for NASA's Strategic Framework

### HPSC-based Autonomy is the Key

Rapid and efficient space transportation

### Land

Expanded access to diverse surface destinations

Live

Sustainable Living and Working Farther from Earth

Transformative missions and discoveries

Rapid, low cost robotic payloads: Moon, Mars and beyond. Next generation computing and communications in space.

Precision landings. Avoid unknown local hazards. Ability to handle unknown environments and situations.

Human and Robotic Lunar Missions > 28 days. Human Mars Missions > 800 days.

Robotic systems augmenting human operation. Remote servicing, assembly and manufacturing.

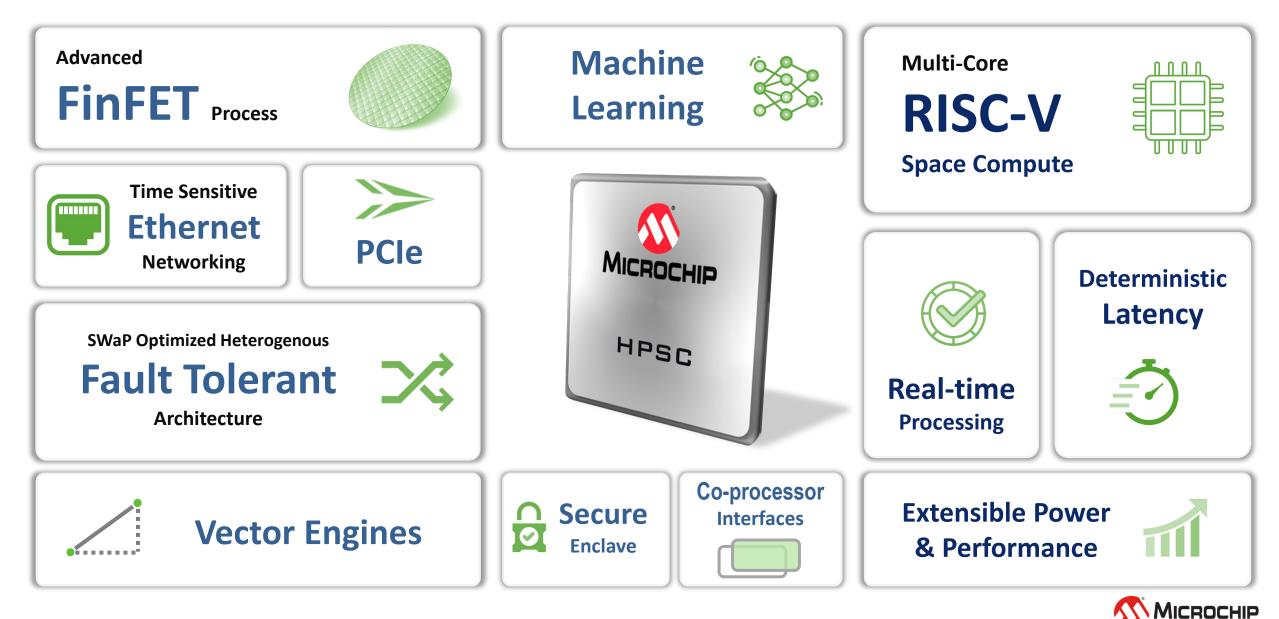

### **HPSC Architecture Highlights**

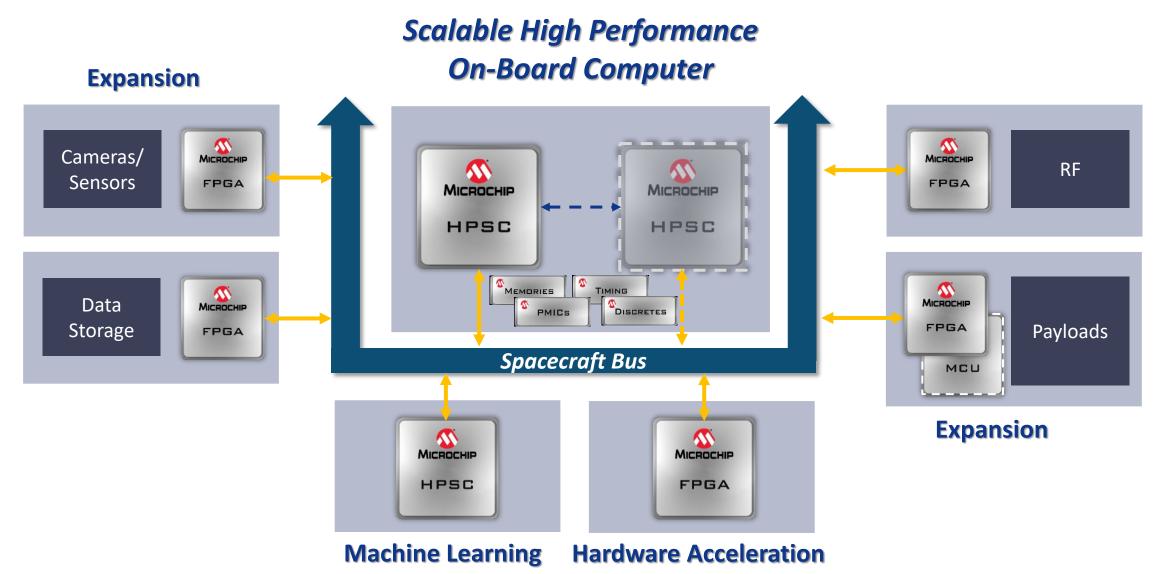

### **Extensible Space System Solution**

**Міскоснір**

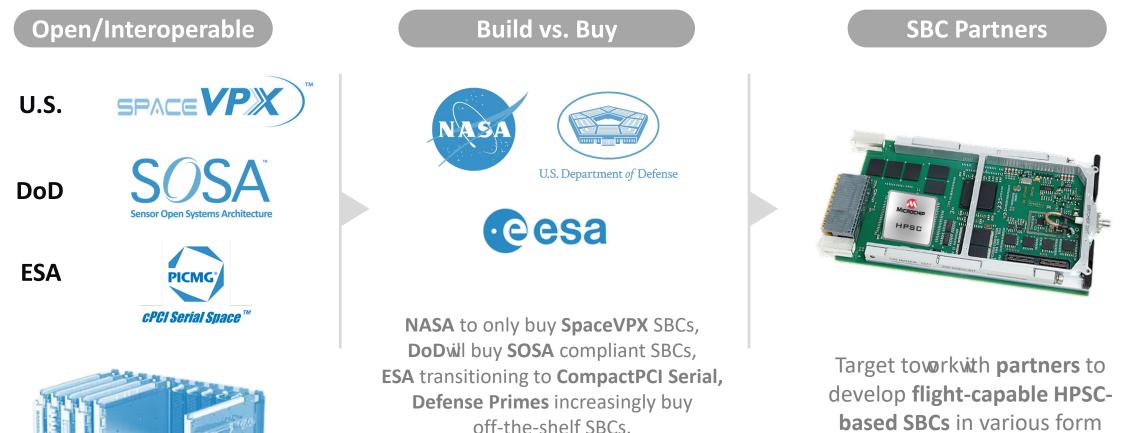

### **Enabling HPSC-Based SBC Ecosystem**

Single Board Computer (SBC) Partners To Fully Address Customer Development Needs

**based SBCs** in various form factors for different end-markets (Space, ESA, Defense, etc.)

### **HPSC Timeline**

### **RISC-V Take Aways**

**RISC-V** breathes new life into the semiconductor industry

#### **CPU Architectural licenses are free**

Leading to more diverse compute solutions for OEMs

Microchip has been a pioneer in this effort

The future is very bright for RISC-V and space-based computing.

# Thank You