NG-Ultra, the European rad-hard SoC + FPGA suitable for future space applications

**SEFUW 2023**

Marion LE PENVEN & Jean-Luc POUPAT

## Key Messages Summary

NG-Ultra is unique in the landscape of available Rad Hard components

It is the only European FPGA solution with a SoC

It offers performancess & robustnesss breakthroughs with Huge FPGA + High performance processing

> Tools are (now) at good maturity level and continue to improve

NG-Ultra selected as technical baseline on several Airbus D&S on-going projects

Why NG-Ultra is unique in the landscape of available Rad Hard components?

Introduction Performances Status Ecosystem Status Use Cases Conclusion

#### Context

Initiated by CNES, collaboration between Airbus and TAS to develop a European chip supported by H2020 NanoXplore is the company owning and commercialising the NG-Ultra manufactured by STMicro in 28FDSOI

## NG-Ultra = SoC + FPGA

Horizon 2020 was the EU's research and innovation funding programme from 2014-2020

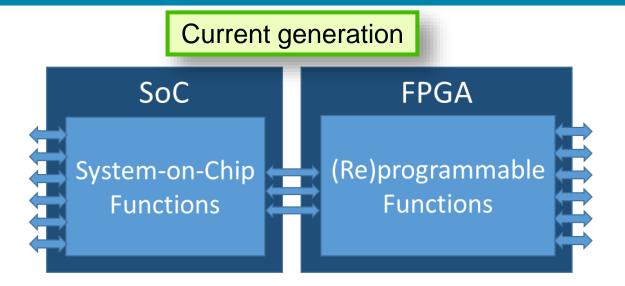

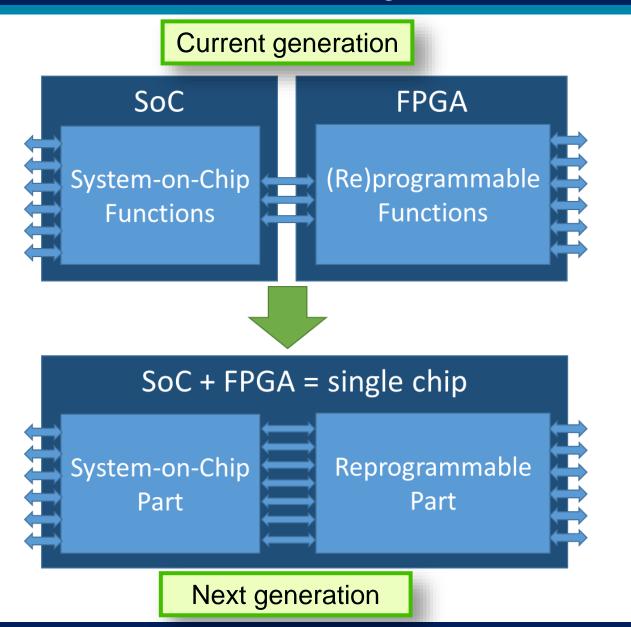

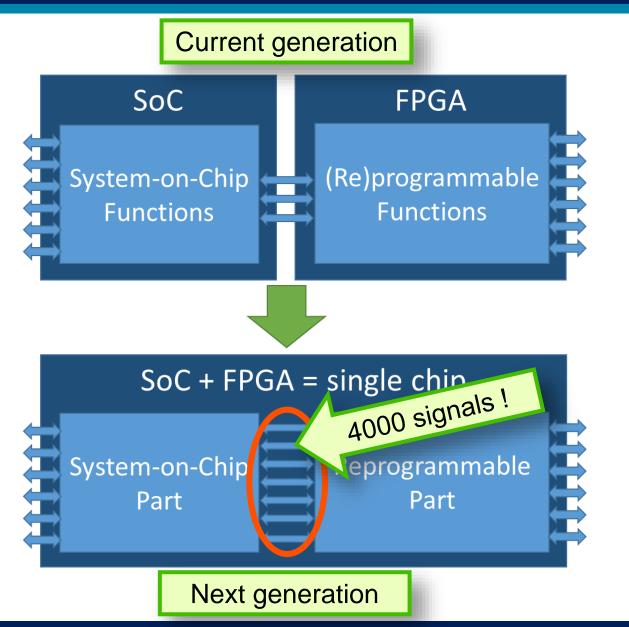

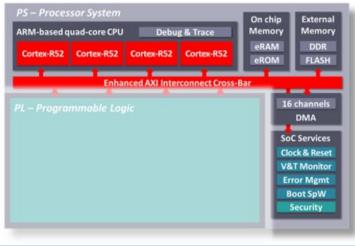

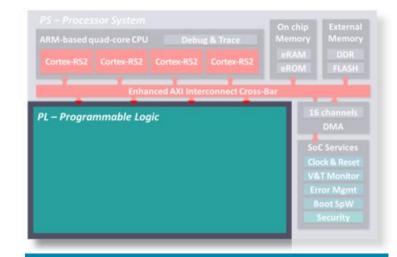

#### To integrated SoCs and beyond

#### Integrated SoC+FPGA

‡ Consistent with the design of processing boards

- ‡ Optimized interfaces SOC Å ÆFPGA

- ‡ Key enabler for more integrated designs& cost reduction

#### To integrated SoCs and beyond

#### Integrated SoC+FPGA

‡ Consistent with the design of processing boards

- ‡ Optimized interfaces SOC Å ÆFPGA

- ‡ Key enabler for more integrated designs& cost reduction

#### To integrated SoCs and beyond

#### Integrated SoC+FPGA

‡ Consistent with the design of processing boards

- ‡ Optimized interfaces SOC Å ÆFPGA

- ‡ Key enabler for more integrated designs& cost reduction

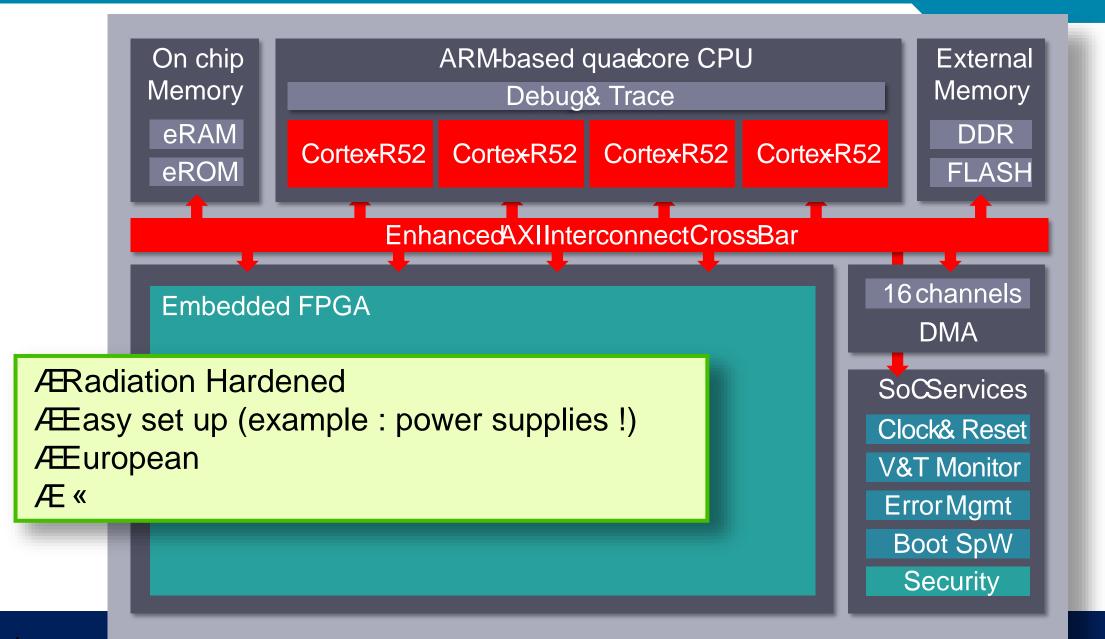

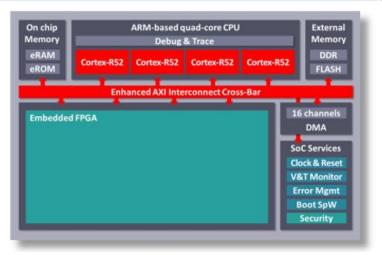

#### Features ±Processing

| ARM-based quadcore CPU |           |           |           |  |  |  |  |

|------------------------|-----------|-----------|-----------|--|--|--|--|

| Debug& Trace           |           |           |           |  |  |  |  |

| CortexR52              | CortexR52 | CortexR52 | CortexR52 |  |  |  |  |

ÆQuad-Core ARM R52 @ 600 MHz > 4000 DMIPS ÆFPU (SP/DP) + NEON SIMD ÆCompatibility with ARM Debug & Trace ecosystem

FPU : Floating Point Unit / SP/DP : Single/Double Precision / SIMD : Single Instruction Multiple Data Co-processing

#### Features ±Memories

| On chip<br>Memory | External<br>Memory |

|-------------------|--------------------|

| eRAM<br>eROM      | DDR<br>FLASH       |

16 channels DMA

ÆBoot eROM + 2 MBytes eRAM w/ ECC ÆMemory interface (volatile) ÆDDR2/DDR3/DDR4 ÆMemory interface (non volatile) ÆBoot NOR Flash Æ16 channels DMA to support memory transfers

#### Features ±Interconnect

ÆAXI network interconnect (ARM NIC400) ÆQuality of Service (QoS)

#### Features ±FPGA matrix

#### Embedded FPGA

ÆMore than 500 KLUTs programmable matrix ÆHSSL in the FPGA ÆAdditional on-chip services ÆSecurity features (e.g. bitstream encryption)

SoCServices Clock& Reset V&T Monitor Error Mgmt Boot SpW Security

#### Features ±What else ?

What are the breakthroughs (\*) of NG-Ultra architecture and detailed performances ?

Introduction Performances Status Ecosystem Status Use Cases Conclusion

(\*) for a rad-hard component

#### High level performances comparison

#### SoC + FPGA

#### SoC only

#### **FPGA only**

NG-Ultra FPGA capacity

~530 KLUT

NG-Ultra processing perfo 1 818 CoreMark / core 1 250 DMIPS / core

CPU Performance Æ40 x SCOC3 Æ2 x GR740 FPGA Capacity Æ2 x RTG4 <sup>(\*)</sup> Æ25 x RTAX2000 <sup>(\*)</sup>

(\*) estimation of realistically useable FPGA size at Q1/2023 date, twice more to be expected considering theoretical LUTs resources and the strong momentum deployed on tools improvement

#### High level performances comparison

| Table: Power Supp                                      | ly Ramp Time                                                                                                                                                      |     |          |        |                       |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|--------|-----------------------|

| Symbol                                                 | Description                                                                                                                                                       |     |          |        |                       |

| T <sub>VCCINT</sub>                                    | -oscription                                                                                                                                                       |     |          |        |                       |

| T <sub>VCCINT_IO</sub>                                 | Ramp time from GND to once                                                                                                                                        |     |          |        | On chip Exter         |

| T <sub>VCCINT_VCU</sub>                                | Ramp time from GND to 95% of V <sub>CCINT</sub><br>Ramp time from GND to 95%                                                                                      | Mir | n Max    | v      |                       |

| T <sub>VCCO</sub>                                      | Ramp time from as of VCCINT IO                                                                                                                                    | 0.2 |          | × Unit | S IROM PLAS           |

| T <sub>VCCAUX</sub>                                    | Ramp time from Que to 35% of VCCINT Voi                                                                                                                           | 0.2 | 40       | ms     |                       |

|                                                        | Ramp time from as                                                                                                                                                 | 0.2 | 40       | ms     | 16 channe             |

| T <sub>MGTAVCC</sub>                                   | Ramp time from Que of VCCAUX                                                                                                                                      | 0.2 | 40       | ms     | Sociarity             |

| T <sub>MGTAVTT</sub>                                   | Ramp time from an of V <sub>CCBPAN</sub>                                                                                                                          | 0.2 | 40       | ms     | Clock & Re            |

| T <sub>MGTVCCAUX</sub>                                 | Ramp time from GND to 95% of V <sub>MGTAVCC</sub><br>Ramp time from GND to 95% of V <sub>MGTAVTT</sub>                                                            |     | 40       | ms     | V&I Mont<br>Error Mgr |

| T <sub>VCC_PSINTFP</sub>                               | Ramp time from GND to 95% of VMCTU                                                                                                                                | 0.2 | 40       | ms     | Boot SpV              |

| T <sub>VCC_PSINTLP</sub>                               | Ramp time from GND to 95% of V <sub>MGTAVTT</sub><br>Ramp time from GND to 95% of V <sub>MGTVCCAUX</sub>                                                          | 0.2 | 40       | ms     |                       |

| T <sub>VCC_PSAUX</sub>                                 | Ramp time from GND to 95% of V <sub>MGTVCCAUX</sub><br>Ramp time from GND to 95% of V <sub>CC_PSINTFP</sub>                                                       | 0.2 | 40       | ms     |                       |

| TVCC POWE                                              | Ramp time from GND to 95% of V <sub>CC_PSINTFP</sub><br>Ramp time from GND to 95% of V <sub>CC_PSINTLP</sub>                                                      | 0.2 | 40       |        | A capacity            |

| T <sub>VCC_PSINTFP_DDR</sub><br>T <sub>VCC_PSADC</sub> | Ramp time from GND to 95% of V <sub>CC_PSINTEP</sub><br>Ramp time from GND to 95% of V <sub>CC_PSAUX</sub>                                                        | 0.2 | 40       | ms     | LUT                   |

| T <sub>VCC_PSPLL</sub>                                 | Ramp time from GND to 95% of V <sub>CC_PSAUX</sub><br>Ramp time from GND to 95% of V <sub>CC_PSINTFP_DDR</sub>                                                    | 0.2 | 40       | ms     |                       |

|                                                        | Ramp time from GND to 95% of V <sub>CC_PSINTFP_DDR</sub><br>Ramp time from GND to 95% of V <sub>CC_PSADC</sub>                                                    | 0.2 | 40       | ms     |                       |

| T <sub>PS_MGTRAVCC</sub>                               |                                                                                                                                                                   | 0.2 | 40       | ms     |                       |

| T <sub>PS_MGTRAVTT</sub>                               | Ramp time from GND to 95% of V <sub>CC_PSADC</sub><br>Ramp time from GND to 95% of V <sub>CC_PSPLL</sub><br>Ramp time from GND to 95% of V <sub>CC_MGTRAVCC</sub> | 0.2 | 40       | ms     | a althur              |

| T <sub>VCCO_PSDDR</sub>                                | Hamp time from Our                                                                                                                                                | 0.2 | 40       | ms     | Dacity                |

| T <sub>VCC_PSDDR_PLL</sub>                             | Ramp time from GND to 95% of V <sub>CC_MGTRAVTT</sub>                                                                                                             | 0.2 | 40<br>40 | ms     |                       |

Comparing performances is important but not enough. Many other criteria shall be considered such as package, radiation hardening, cost, hardware setup (memories, power supply « KDUGaZdDUH software ecosystem, ULVN PLWLJDWLRQ RIH[SRUW FRQWURO OLPLWD

#### Space environment is hostile - Radiations

## NG-80WUD UDGLDWLRQ UREXVWO

‡28FDSOI technology intrinsically latch-up immune Æno SEL

‡NG-Ultra tested during 2 radiation campaigns Æno SEFI

‡Robustness confirmed (no SEU, no SEFI) on v1, v2 launched

## DDR memory protection Æa game changer

\$\$\product\$ Supporting DDR2, DDR3 and DDR4 / 8-bits & 16-bits devices

\$\$\product\$ Reed-Solomon for SEU high level of memory protection

\$\$\product\$ Robustness against SEFI up to the loss of two 16-bits devices

#### NG-Ultra architecture approach ±No « weakest link »

Having a high performance and very robust component is not enough, because if it is associated to sensitive components (such as peripheral memories), the overall UREXVWQHVV ZLOO GHSHQGV RQ WKH <sup>3</sup> As an example, if you need to reboot each time you have an upset in a memory, this will drive the way you RSHUDWH \RXU SURFHVVLQJ PRGXOH« WKLV LV DQ LVVXH«

NG-Ultra solves this issue, since (1) it offers a robust Radiation Hardened By Design (RHBD) chip and (2) it provides unprecedented protection mechanisms for all of its peripheral components (Flash, DDR) allowing to XVH LW ZLWKRXW ULVN RI LQWURGXI

# What about the ecosystem to develop with NG-Ultra?

Introduction Performances Status Ecosystem Status Use Cases Conclusion

#### NG-Ultra ±OPERA Study Status

Horizon 2020 was the EU's research and innovation funding programme from 2014-2020

OPERA project objectives were to assess the performances that can be achieved by some designs in NG-ULTRA technology and compare it with performances achieved in reference technologies.

Several designs from low to higher complexity synthesized on both NG-Ultra and RTG4 targets \$\propto ynthesis\$

9Synthesis time Æsimilar performance on both technologies

9Clock frequency Æsimilar performance ~100MHz, Libero/RTG4 slightly better handles complex design 9Resource utilization Æperformance in favor of NG -Ultra factor of 1.5 in nb of LUT, factor 2 improvement on large memories due to NG-Ultra larger BRAM, larger DSP width +++ for algo

Place and Route

9Not easy to obtain a good layout in one run whatever the target Æsimilar performance

## NG-Ultra relevance confirmed for ADS future projects

## What about first use cases targeted by Airbus with NG-Ultra ?

Introduction Performances Status Ecosystem Status Use Cases Conclusion

#### NG-Ultra already on ADS Projects - Platform OBC-Ultra

#### NG-Ultra present in both platform & payload ADS roadmaps

‡Several boards under development ÆQ2 2023 / NG-Ultra+DDR4 demo, Q3 2023 / OBC use case demonstrated with OLYMPE processing board ‡One main component = simplified board design

#### NG-Ultra-based OBC

#High performances multicore processing @600MHz, FPGA @80MHz #NAND Flash + DDR4 Memory + High Speed Serial Links #Enhanced Security features / Bitstream encryption included #ADHA-compatible format

#### Highly integrated OBC-Ultra

‡Gain in performances confirmed through studies ‡More than 500kLUT compared to ~20kLUT for previous generation with RTAX2000 ‡More embedded functionalities ‡Very compact product

#### NG-Ultra on ADS Projects - Payload Missions

## Payload missions requirements analysis

‡Very performant FPGA (fast clocking, huge matrix)‡High DDR bandwidth‡High Speed Serial Links

#### NG-Ultra suitability ? Confirmed !

#Huge 500k LUT matrix

#> 1000 Large DSPs

#DDR4 100Gbps

#HSSL

NG-Ultra-based board for payload processing under development at Airbus

DDRA

LASH

HSSI

‡Ground demonstrator ready for Q4 2023

What can be concluded considering the overall picture and status on NG-Ultra ?

Introduction Performances Status Ecosystem Status Use Cases Conclusion

## Key Messages Summary

NG-Ultra is unique in the landscape of available Rad Hard components

It is the only European FPGA solution with a SoC

It offers performances & robustness breakthroughs with Huge FPGA + High performance processing

Confidence in tools capacity to meet performances for complex designs use cases (cf OPERA)

NG-Ultra selected as technical baseline on several Airbus D&S on-going projects

Questions:??