SpacE FPGA Users Workshop (SEFUW) 2023, ESTEC, Noordwijk, 14-16 March

# High-Performance UVM Verification IP for SpaceWire Codec

Simone Vagaggini<sup>1,2</sup>, Marco Trafeli<sup>1</sup>, Daniele Davalle<sup>1</sup>, Lucana Santos<sup>3</sup>, Roberto Ciardi<sup>1,2</sup>, Pietro Nannipieri<sup>2</sup>, Luca Fanucci<sup>2</sup>

<sup>1</sup>IngeniArs S.r.l., Via Ponte a Piglieri 8, Pisa, Italy

<sup>2</sup>Dept. Of Information Engineering, University of Pisa, Via Caruso 16, Pisa, Italy

<sup>3</sup>European Space Research and Technology Centre, European Space Agency, Keplerlaan 1, Noordwijk, The Netherlands

- Introduction

- UVM-based SpaceWire Codec Twin Model

- UVM-based Verification Environment Architecture

- Verification Campaign

- UVM-based Approach Advantages

- Results and Conclusions

- Q&A

- Introduction

- UVM-based SpaceWire Codec Twin Model

- UVM-based Verification Environment Architecture

- Verification Campaign

- UVM-based Approach Advantages

- Results and Conclusions

- Q&A

Verification Intellectual Property (VIP) for Functional Verification of any SpaceWire Codec, Fully compliant with Universal Verification Methodology (UVM)

## Verification Intellectual Property (VIP) for Functional Verification of any SpaceWire Codec, Fully compliant with Universal Verification Methodology (UVM)

• Developed by IngeniArs S.r.l.

## Verification Intellectual Property (VIP) for Functional Verification of any SpaceWire Codec, Fully compliant with Universal Verification Methodology (UVM)

- Developed by IngeniArs S.r.l.

- Funded by European Space Agency

## Verification Intellectual Property (VIP) for Functional Verification of any SpaceWire Codec, Fully compliant with Universal Verification Methodology (UVM)

- Developed by IngeniArs S.r.l.

- Funded by European Space Agency

- Activity goals:

- > Check the compliance of IP Cores with the SpW standard

THE REPARTMENTO DI INGENIATS

## Verification Intellectual Property (VIP) for Functional Verification of any SpaceWire Codec, Fully compliant with Universal Verification Methodology (UVM)

- Developed by IngeniArs S.r.l.

- Funded by European Space Agency

- Activity goals:

- > Check the compliance of IP Cores with the SpW standard

- Evaluate the UVM advantages

THE REPARTMENTO DI INGENIATS

## Verification Intellectual Property (VIP) for Functional Verification of any SpaceWire Codec, Fully compliant with Universal Verification Methodology (UVM)

- Developed by IngeniArs S.r.l.

- Funded by European Space Agency

- Activity goals:

- > Check the compliance of IP Cores with the SpW standard

- ≻ Evaluate the UVM advantages

- > Prove the UVM applicability to space systems

## Verification Intellectual Property (VIP) for Functional Verification of any SpaceWire Codec, Fully compliant with Universal Verification Methodology (UVM)

- Developed by IngeniArs S.r.l.

- Funded by European Space Agency

- Activity goals:

- > Check the compliance of IP Cores with the SpW standard

- ≻ Evaluate the UVM advantages

- > Prove the UVM applicability to space systems

Promotion of UVM-based Verification Approach

- Introduction

- UVM-based SpaceWire Codec Twin Model

- UVM-based Verification Environment Architecture

- Verification Campaign

- UVM-based Approach Advantages

- Results and Conclusions

- Q&A

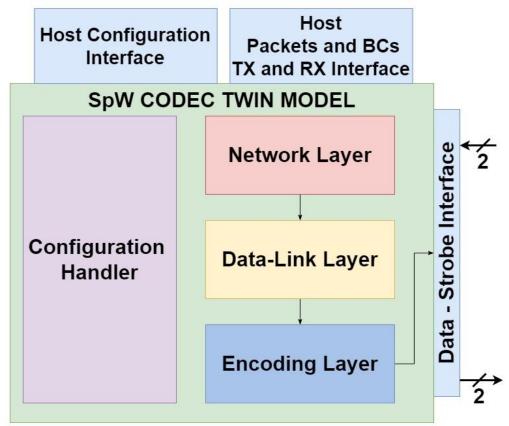

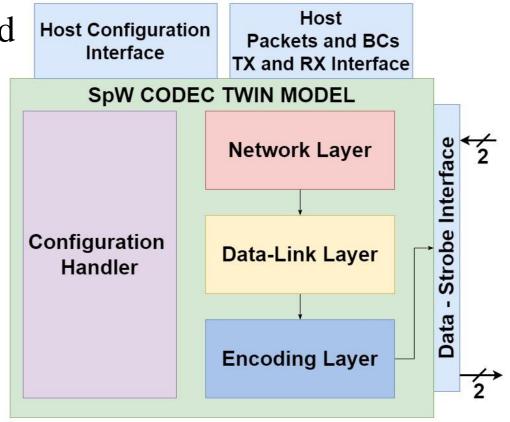

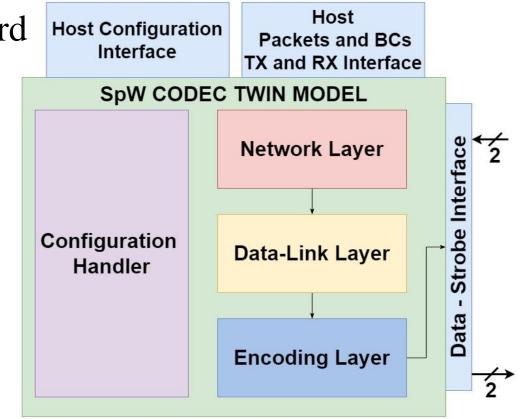

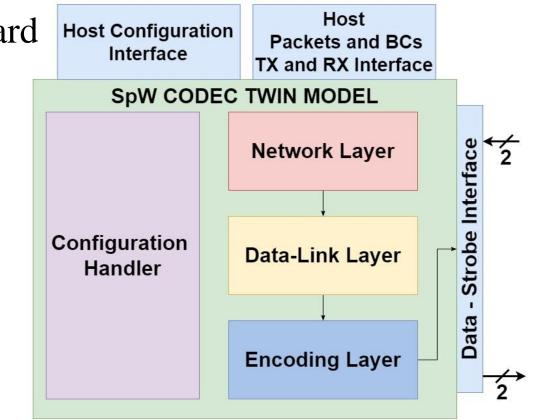

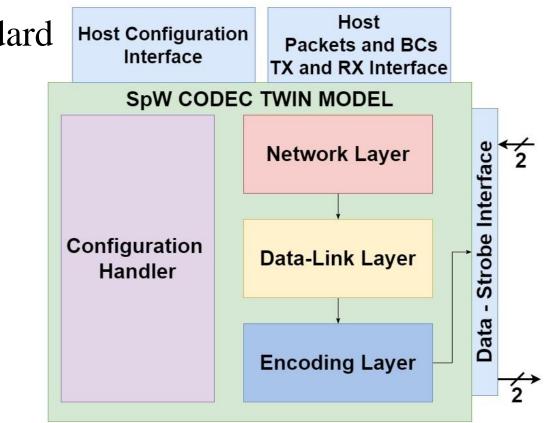

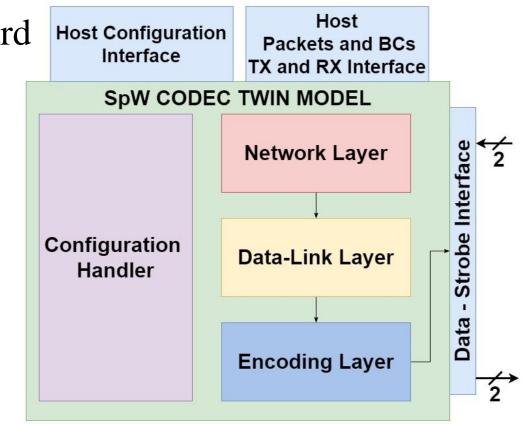

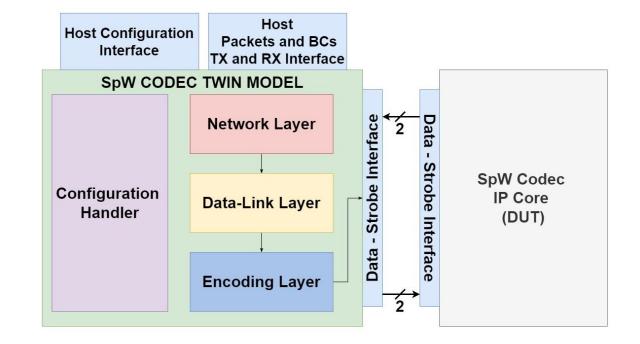

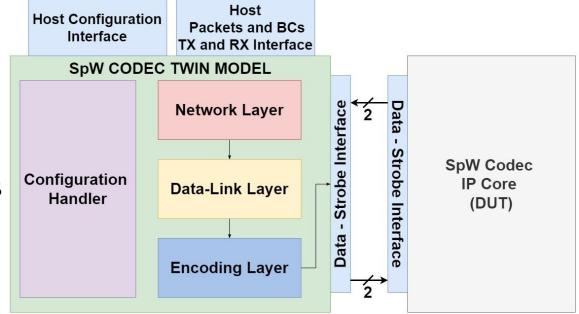

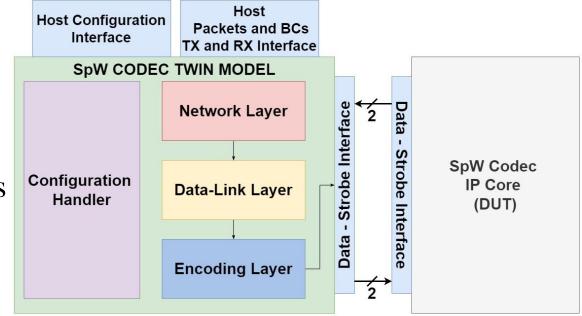

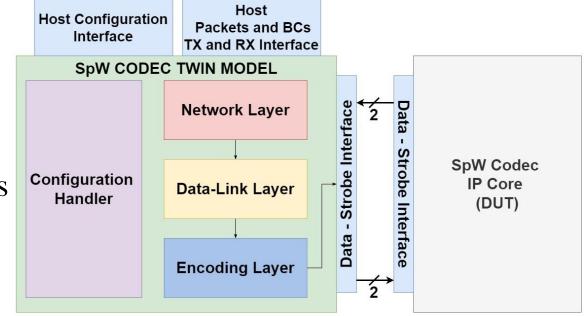

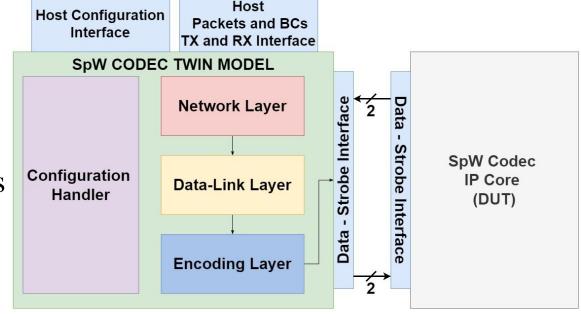

• Emulates the ideal behavior of a SPW Codec

- Emulates the ideal behavior of a SPW Codec

- Fully compliant with Rev.1 of SpW Standard

- Emulates the ideal behavior of a SPW Codec

- Fully compliant with Rev.1 of SpW Standard

- Developed in SystemVerilog HVL

- Emulates the ideal behavior of a SPW Codec

- Fully compliant with Rev.1 of SpW Standard

- Developed in SystemVerilog HVL

- Fully compliant with UVM

Easily reusable and maintainable

- Emulates the ideal behavior of a SPW Codec

- Fully compliant with Rev.1 of SpW Standard

- Developed in SystemVerilog HVL

- Fully compliant with UVM

Easily reusable and maintainable

- Host interface

- $_{\odot}$  Packets and BC transmission and reception

- $\circ$  Configuration changes and readings

THE REARTIMENTO DI INGENIATS

- Emulates the ideal behavior of a SPW Codec

- Fully compliant with Rev.1 of SpW Standard

- Developed in SystemVerilog HVL

- Fully compliant with UVM

Easily reusable and maintainable

- Host interface

- Packets and BC transmission and reception

Configuration changes and readings

- $\circ$  Configuration changes and readin

- Data-Strobe interface

- Communication with DUT or any system with SpW interface

• Direct Communication with DUT

Direct Communication with DUT

> Automatic link initialization

Direct Communication with DUT

> Automatic link initialization

> Automatic TX and RX credit handling

- Direct Communication with DUT

> Automatic link initialization

> Automatic TX and RX credit handling

- > Automatic TX of NULLs when needed

- Direct Communication with DUT

> Automatic link initialization

- > Automatic TX and RX credit handling

- > Automatic TX of NULLs when needed

- > Automatic recognition of all types of errors

- Direct Communication with DUT

> Automatic link initialization

- ≻ Automatic TX and RX credit handling

- > Automatic TX of NULLs when needed

- > Automatic recognition of all types of errors

- > No actions needed by the user

- Direct Communication with DUT

> Automatic link initialization

- > Automatic TX and RX credit handling

- > Automatic TX of NULLs when needed

- > Automatic recognition of all types of errors

- > No actions needed by the user

- Higher level of abstraction

> Only packets and BCs to be defined

- Direct Communication with DUT

> Automatic link initialization

- > Automatic TX and RX credit handling

- > Automatic TX of NULLs when needed

- > Automatic recognition of all types of errors

- $\succ$  No actions needed by the user

- Higher level of abstraction

> Only packets and BCs to be defined

Significant Simplification of the Verification Process Significant Reduction in Verification Time and Cost

- Introduction

- UVM-based SpaceWire Codec Twin Model

- UVM-based Verification Environment Architecture

- Verification Campaign

- UVM-based Approach Advantages

- Results and Conclusions

- Q&A

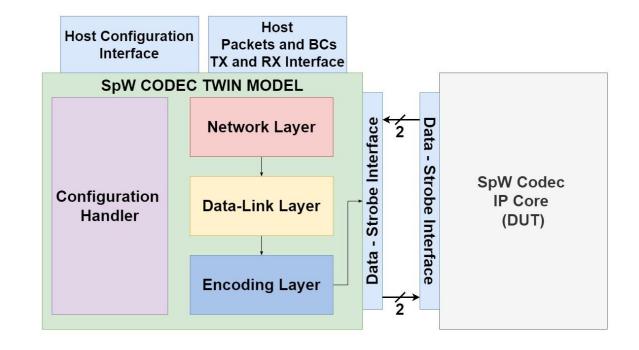

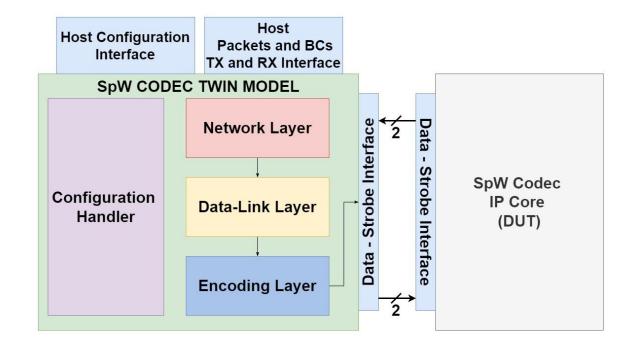

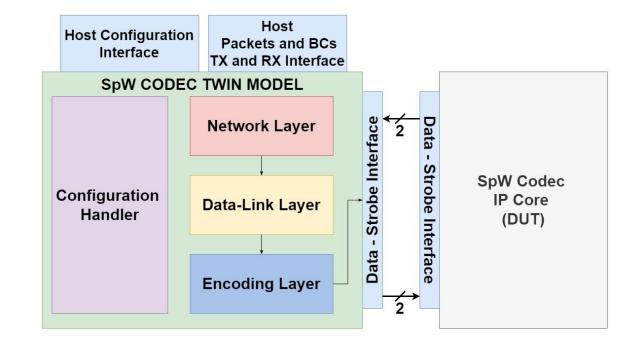

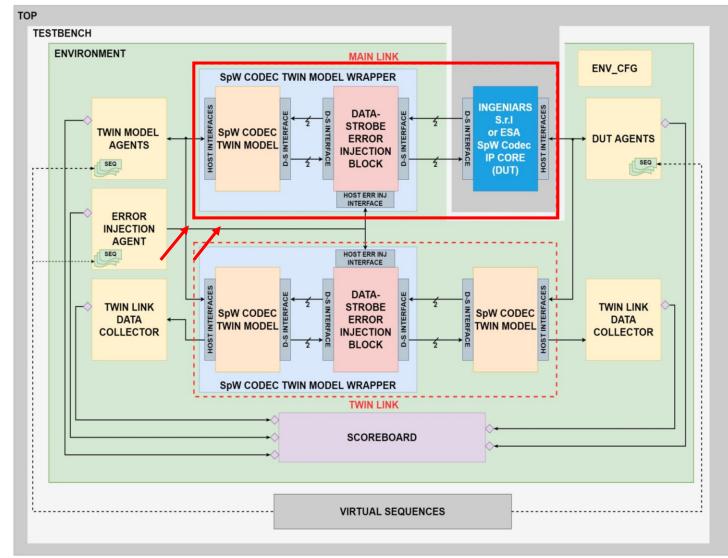

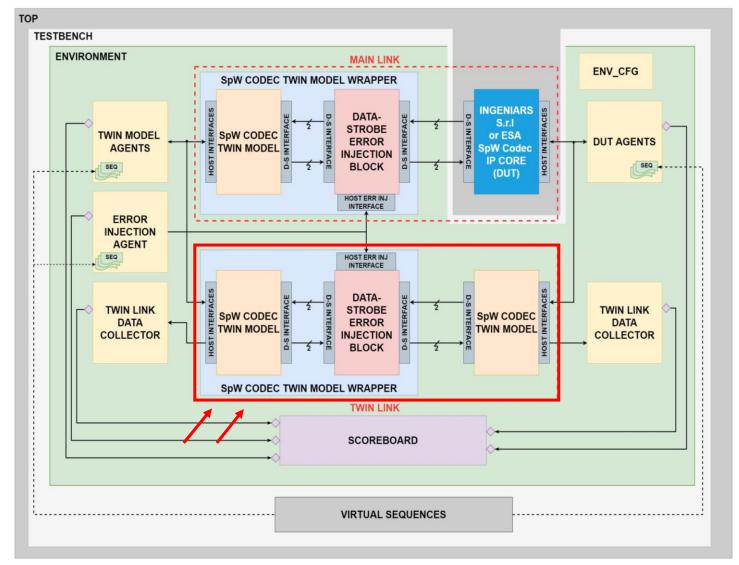

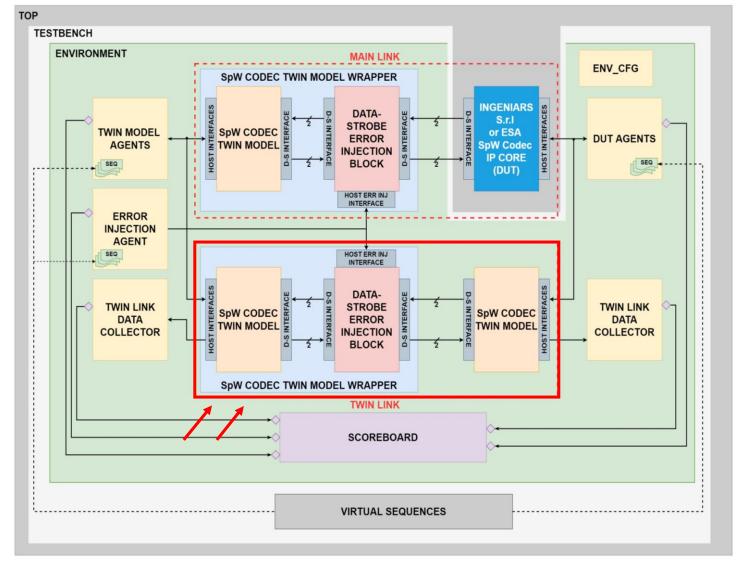

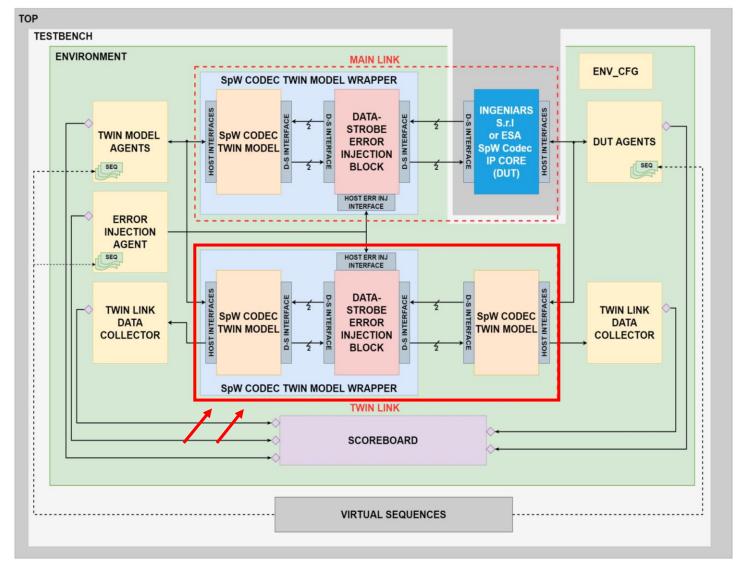

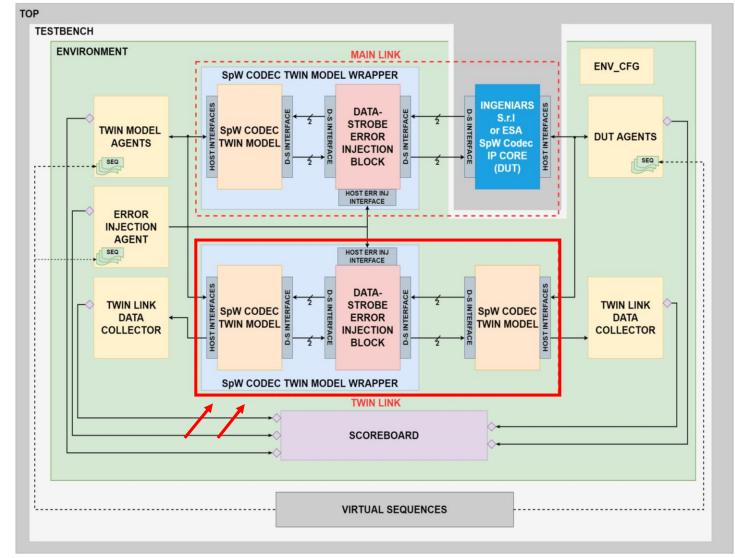

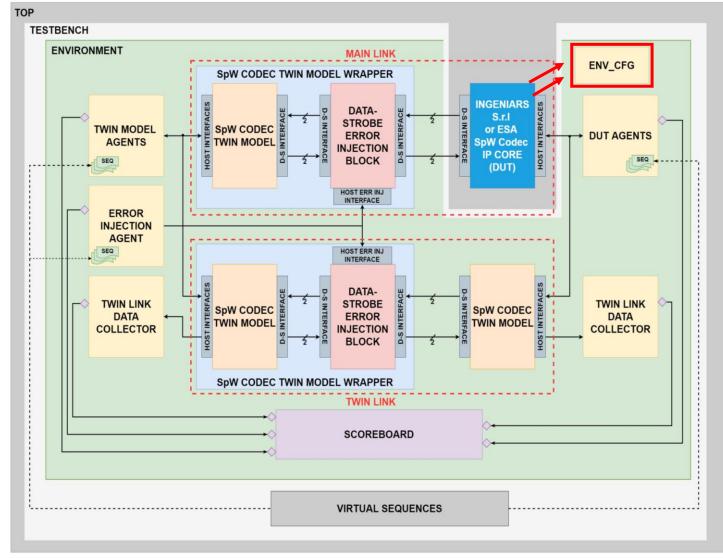

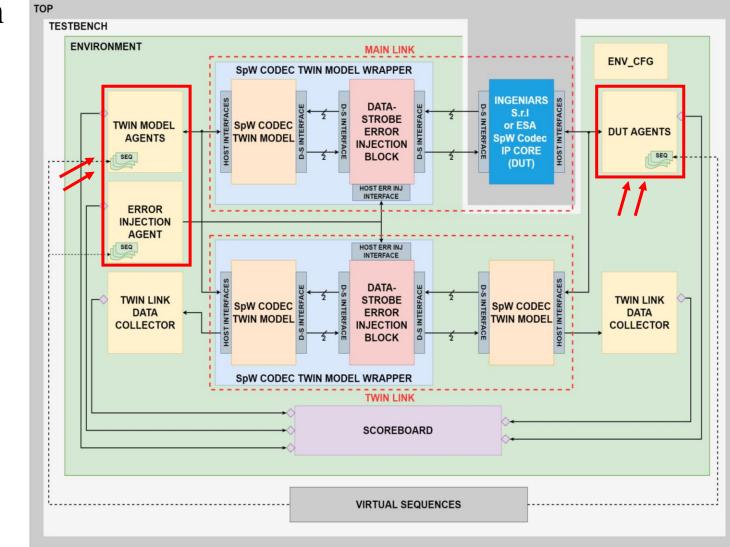

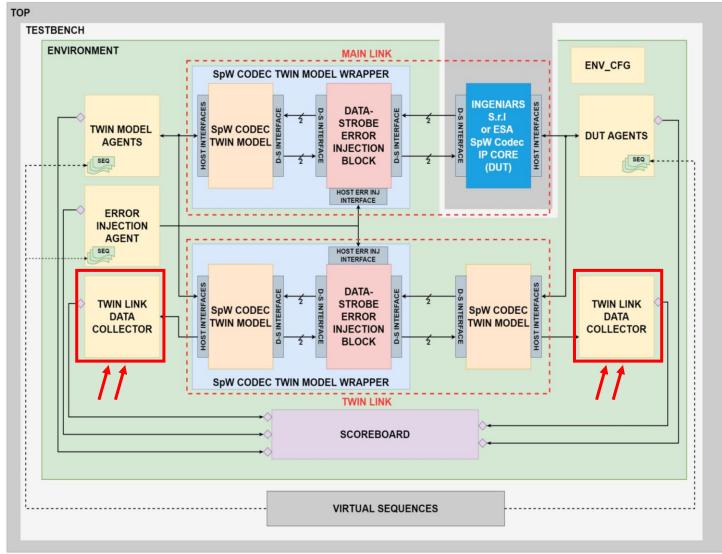

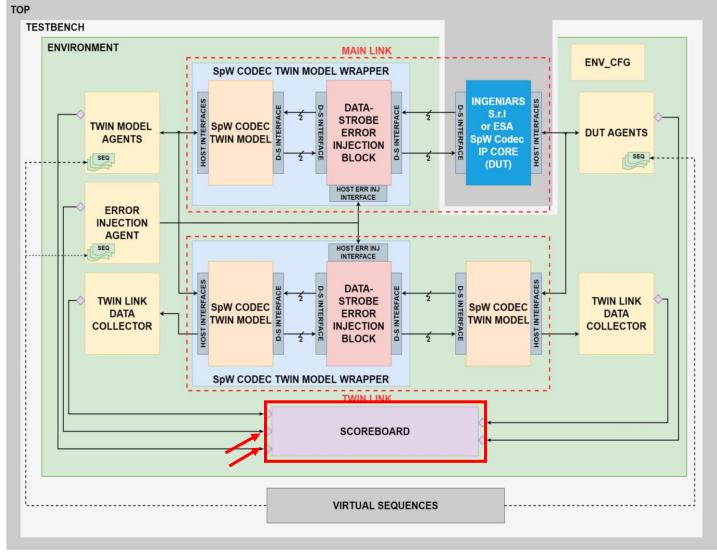

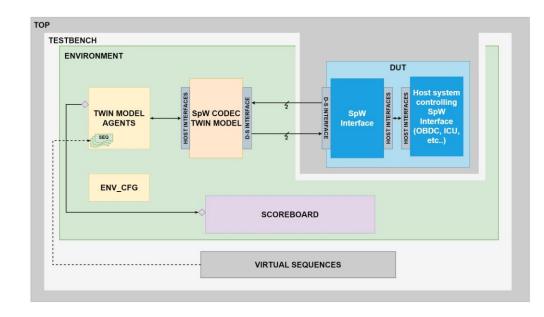

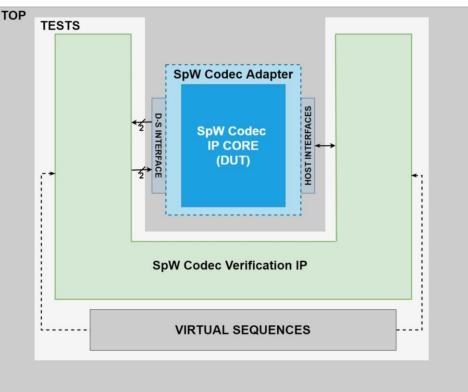

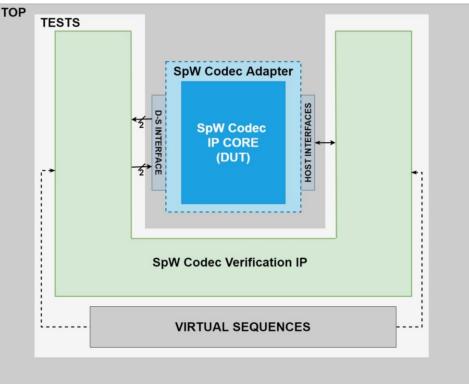

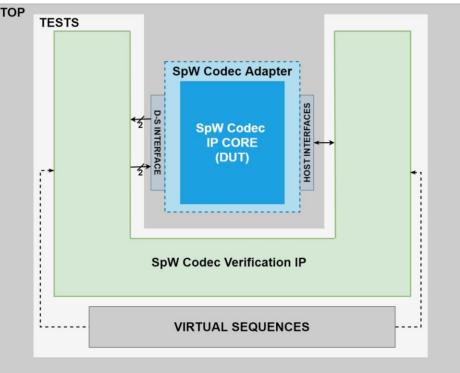

- Main Link

- Communication between DUT and Twin Model

- Main Link

- Communication between DUT and Twin Model

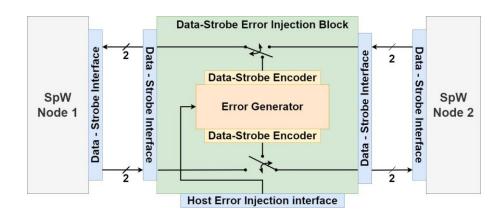

- $\circ$  Data-Strobe Error Injector

- Main Link

- Communication between DUT and Twin Model

- $\circ$  Data-Strobe Error Injector

- Twin Link

- Communication between two Twin Models

- Main Link

- Communication between DUT and Twin Model

- $\circ$  Data-Strobe Error Injector

- Twin Link

- Communication between two Twin Models

- Same stimuli of the Main Link

- Main Link

- Communication between DUT and Twin Model

- Data-Strobe Error Injector

- Twin Link

- Communication between two Twin Models

- Same stimuli of the Main Link

- Emulates the ideal behavior of the SpW Link

- Main Link

- Communication between DUT and Twin Model

- Data-Strobe Error Injector

- Twin Link

- Communication between two Twin Models

- Same stimuli of the Main Link

- Emulates the ideal behavior of the SpW Link

## Support automated verification of all possible simulation scenarios

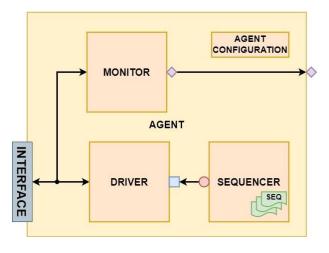

Environment Configuration

- Environment Configuration

- Agents

7

- $\circ$  DUT

- $\circ$  Twin Model

- $\circ$  Error Injection

- Environment Configuration

- Agents

- $\circ$  DUT

- $\circ$  Twin Model

- Error Injection

- Twin Link Data Collectors

- Environment Configuration

- Agents

- $\circ$  DUT

- $\circ$  Twin Model

- Error Injection

- Twin Link Data Collectors

- Scoreboard

- Introduction

- UVM-based SpaceWire Codec Twin Model

- UVM-based Verification Environment Architecture

- Verification Campaign

- UVM-based Approach Advantages

- Results and Conclusions

- Q&A

Defined and implemented 153 testcases

00% of functional coverage of SpW Standard Rev.1

- Defined and implemented 153 testcases

00% of functional coverage of SpW Standard Rev.1

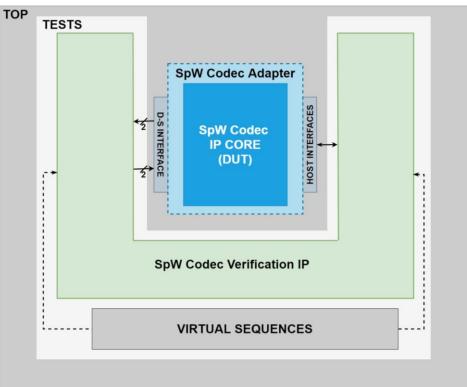

- Verification Campaign on IngeniArs SpW Codec IP Core

- Defined and implemented 153 testcases

00% of functional coverage of SpW Standard Rev.1

- Verification Campaign on IngeniArs SpW Codec IP Core

- Verification Campaign on ESA SpW Codec IP Core

Basic VHDL adapter has been developed

- Defined and implemented 153 testcases

00% of functional coverage of SpW Standard Rev.1

- Verification Campaign on IngeniArs SpW Codec IP Core

- Verification Campaign on ESA SpW Codec IP Core

Basic VHDL adapter has been developed

| DUT                                   | Compliance with<br>SpW Standard | Compliance with<br>SpW Standard Rev.1 | Code Coverage –<br>Statements | Code Coverage -<br>Branches |

|---------------------------------------|---------------------------------|---------------------------------------|-------------------------------|-----------------------------|

| IngeniArs S.r.l.<br>SpW Codec IP Core | $\checkmark$                    | $\checkmark$                          | 96.05%                        | 92.08%                      |

| ESA<br>SpW Codec IP Core              | $\checkmark$                    | X                                     | 95.24%                        | 91.72%                      |

- Introduction

- UVM-based SpaceWire Codec Twin Model

- UVM-based Verification Environment Architecture

- Verification Campaign

- UVM-based Approach Advantages

- Results and Conclusions

- Q&A

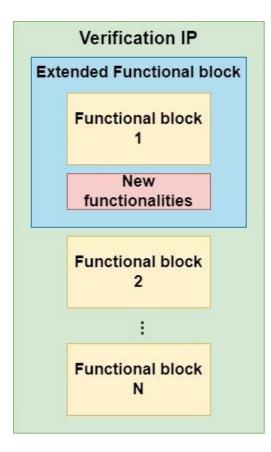

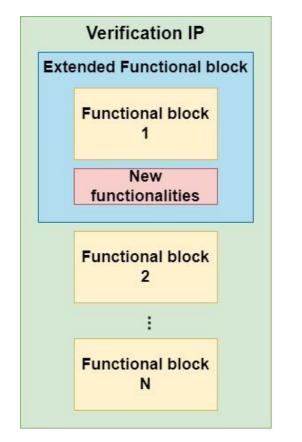

• Maintainability

#### • Maintainability

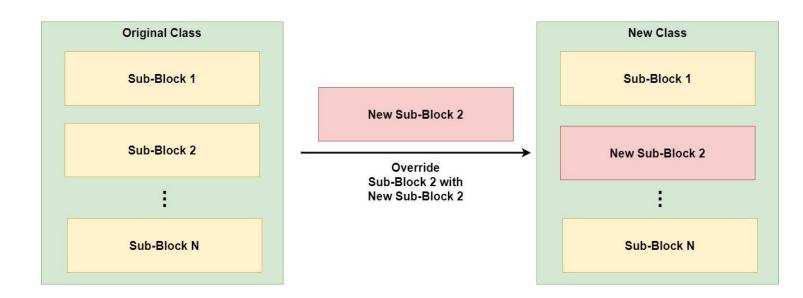

➤Add functionalities (extension)

### • Maintainability

≻Add functionalities (extension)

#### ➢Update functionalities (override)

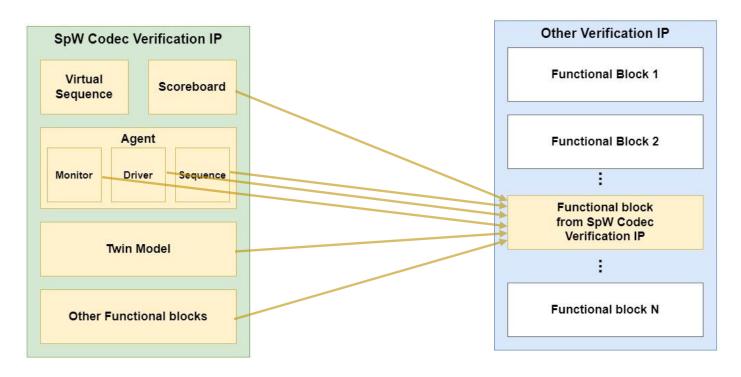

- Maintainability

- Reusability

- Maintainability

- Reusability

- ≻From a single functional block

- Maintainability

- Reusability

- ≻From a single functional block

(DUT)

IP Core 1

IP Core 2

IP Core 1

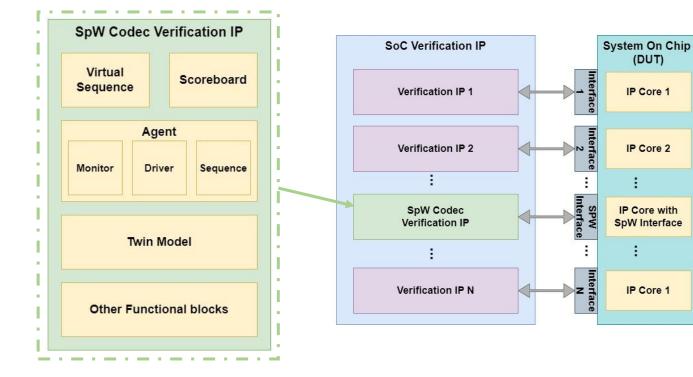

- Maintainability

- Reusability

- Separation between Verification IPs developers and users

- Maintainability

- Reusability

- Separation between Verification IPs developers and users

- Usability without deep knowledge of the VIPs architecture, SystemVerilog HVL and UVM standard

- Maintainability

- Reusability

- Separation between Verification IPs developers and users

- Usability without deep knowledge of the VIPs architecture, SystemVerilog HVL and UVM standard

- $\circ$  Very user-friendly definition of new test cases

- Maintainability

- Reusability

- Separation between Verification IPs developers and users

- Usability without deep knowledge of the VIPs architecture, SystemVerilog HVL and UVM standard

- $\circ$  Very user-friendly definition of new test cases

- Possibility to buy VIPs developed by other companies

- Maintainability

- Reusability

- Separation between Verification IPs developers and users

- Usability without deep knowledge of the VIPs architecture, SystemVerilog HVL and UVM standard

- Very user-friendly definition of new testcases

Possibility to buy VIPs developed by other companies

Visit IngeniArs Booth to prove our SpW Codec Verification IP

- Introduction

- UVM-based SpaceWire Codec Twin Model

- UVM-based Verification Environment Architecture

- Verification Campaign

- UVM-based Approach Advantages

- Results and Conclusions

- Q&A

### Verification IP supporting a full test Campaign of any SpW Codec

• Based on SpW Codec Twin Models

- Based on SpW Codec Twin Models

- Double-Link Environment Architecture

- Based on SpW Codec Twin Models

- Double-Link Environment Architecture

- Completely automated and self-checking

- Based on SpW Codec Twin Models

- Double-Link Environment Architecture

- Completely automated and self-checking

- Supporting all communication scenarios provided by the SpW Standard

- Based on SpW Codec Twin Models

- Double-Link Environment Architecture

- Completely automated and self-checking

- Supporting all communication scenarios provided by the SpW Standard

- Employed in verification campaigns:

- Up to 100% functional coverage of SpW Standard, Rev.1.

- Based on SpW Codec Twin Models

- Double-Link Environment Architecture

- Completely automated and self-checking

- Supporting all communication scenarios provided by the SpW Standard

- Employed in verification campaigns:

- Up to 100% functional coverage of SpW Standard, Rev.1.

- o On IngeniArs S.r.l. SpW Codec IP Core

- Based on SpW Codec Twin Models

- Double-Link Environment Architecture

- Completely automated and self-checking

- Supporting all communication scenarios provided by the SpW Standard

- Employed in verification campaigns:

- Up to 100% functional coverage of SpW Standard, Rev.1.

- o On IngeniArs S.r.l. SpW Codec IP Core

- $\circ$   $\,$  On European Space Agency SpW Codec IP Core

- Fully compliant with UVM with advantages in terms of:

- o Maintainability

- Reusability in other projects

- Fully compliant with UVM with advantages in terms of:

- Maintainability

- Reusability in other projects

- Reusable for Verification of any SpW Codec IP Core

- Very user-friendly

- Knowlegde of SystemVerilog, UVM and VIP Architecture not required

- Fully compliant with UVM with advantages in terms of:

- Maintainability

- Reusability in other projects

- Reusable for Verification of any SpW Codec IP Core

- Very user-friendly

- Knowlegde of SystemVerilog, UVM and VIP Architecture not required

- $\circ$  Reusable for Testing of any DUT with SpW Interfaces

# Verification IP supporting a full test Campaign of any SpW Codec

- Fully compliant with UVM with advantages in terms of:

- Maintainability

- Reusability in other projects

- Reusable for Verification of any SpW Codec IP Core

- Very user-friendly

- Knowlegde of SystemVerilog, UVM and VIP Architecture not required

- Reusable for Testing of any DUT with SpW Interfaces

# Significant reduction of verification time and costs Significant increase of DUTs reliability

# **Thanks for your attention!**

# For more information about SpW Codec Verification IP:

#### **Visit IngeniArs Booth**

simone.vagaggini@ingeniars.com marco.trafeli@ingeniars.com daniele.davalle@ingeniars.com

**Email:**

The Art of Engineering