#### ASIC Development for Space Radiation Monitors at IDEAS

#### Integrated Detector Electronics AS

Presented to the European Space Plasma and Radiation Workshop, ESTEC, May 14 2014 Philip Påhlsson, Development Engineer, philip.pahlsson@ideas.no

#### ASIC Development for Space Radiation Monitors at IDEAS

**IDEAS** company overview

**ASIC** Heritage and ASIC families

Selection of ASICs for space radiation and plasma monitoring

#### Integrated Detector Electronics AS

Presented to the European Space Plasma and Radiation Workshop, ESTE Philip Pahlsson, Development Engineer, philip.pahlsson@ideas.no

2014-05-14

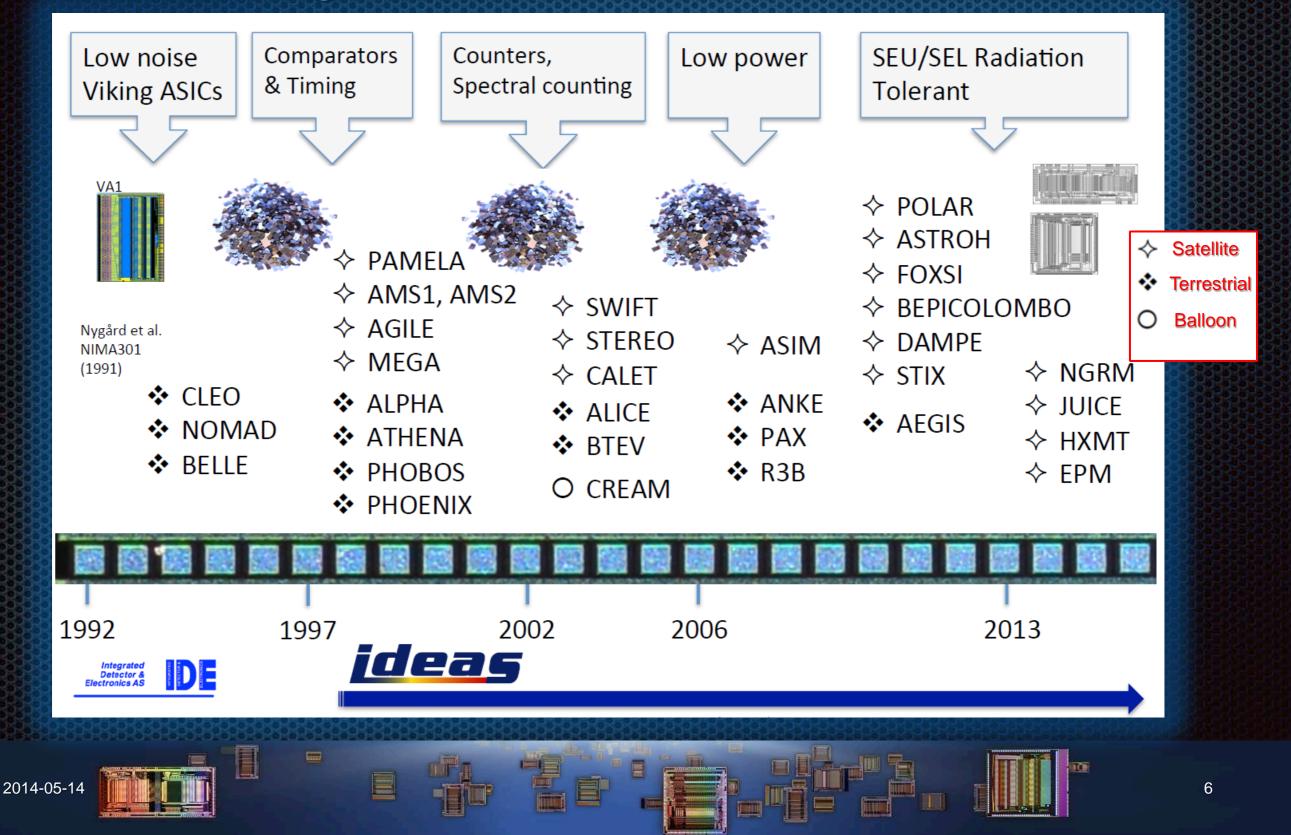

## IDEAS overview

IDEAS - Integrated Detector Electronics AS develops and sells integrated circuits for radiation detection and imaging applications. The company was founded in 1992 with strong background in applied physics, radiation detector instrumentation and electrical engineering. The headquarter is located near Oslo, Norway. IDEAS products are used in medical imaging, industrial inspection, nuclear science and astrophysics. The circuits can be delivered in any quantity to commercial and scientific customers worldwide.

## **IDEAS** staff

2 Ph.D. Physicists with Nuclear Science and HEP

1 Ph.D. Electronics Engineer, Digital Systems

6 M.Sc Integrated Circuit Designers

2 M.Sc Electronic Design Engineers

2 M.Sc Space Engineering

1 Electronic Design/Validation Engineer

1 Technician

1 M.Sc. Senior Accountant

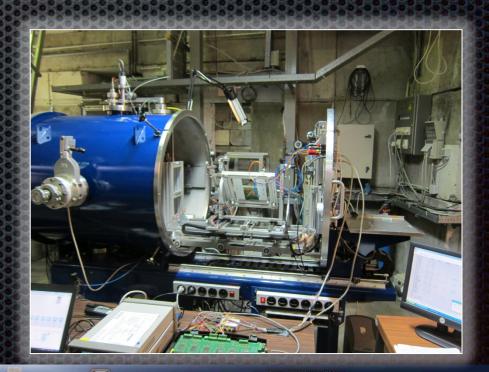

## **IDEAS** validation

Temperature Chamber Cryogenic Dewar X-ray Source Radioactive sources

| 00000 |  |

|-------|--|

| Validation | Standard   |

|------------|------------|

| SEE        | ESCC-25100 |

| TID        | ESCC-22900 |

| SEM        | ESCC-21400 |

#### ASIC heritage for Science

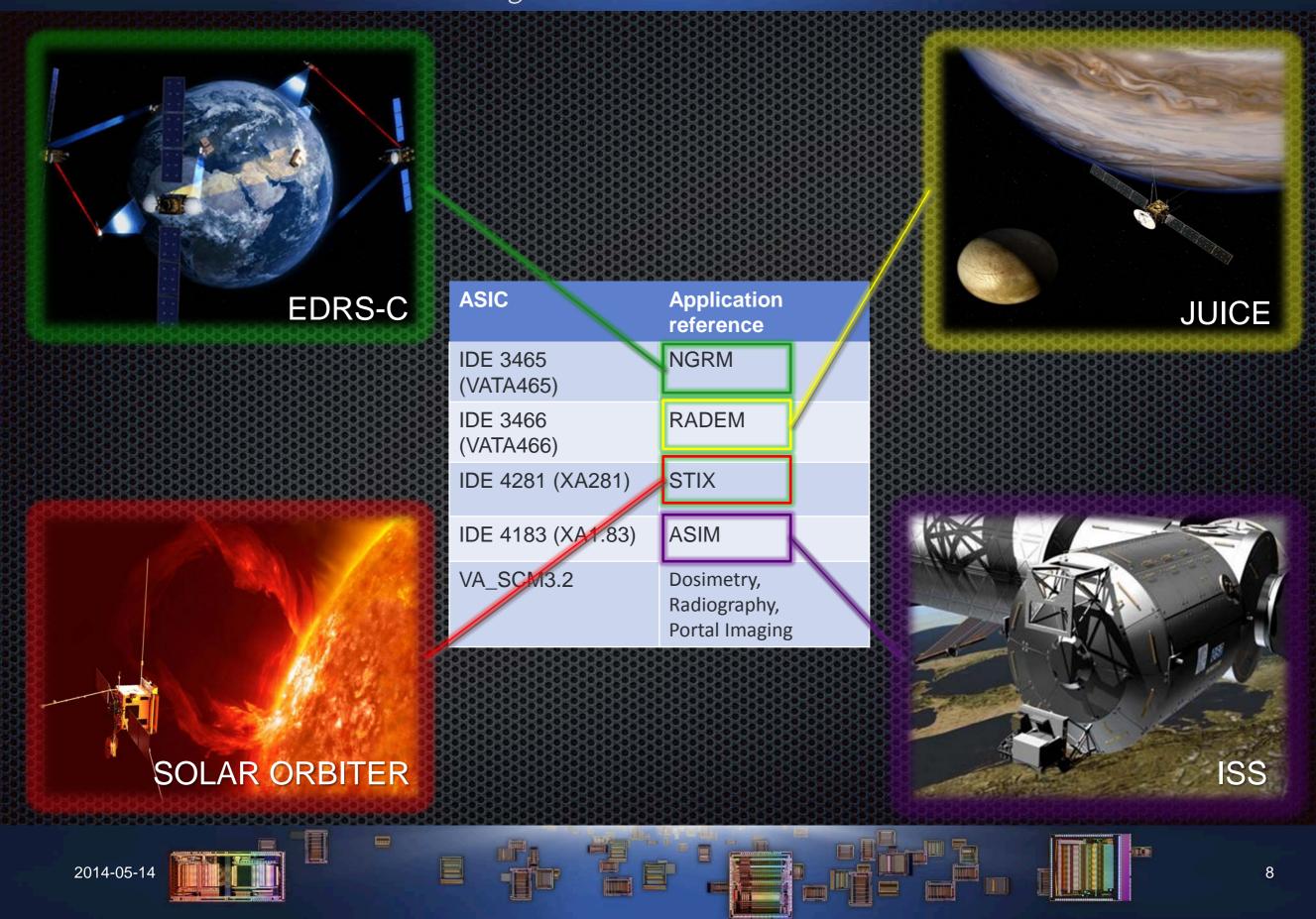

# Selection of ASICs

| ASIC               | Application<br>reference                     |

|--------------------|----------------------------------------------|

| IDE 3465 (VATA465) | NGRM                                         |

| IDE 3466 (VATA466) | RADEM                                        |

| IDE 4281 (XA281)   | STIX                                         |

| IDE 4183 (XA1.83)  | ASIM                                         |

| VA_SCM3.2          | Dosimetry,<br>Radiography,<br>Portal Imaging |

#### **ideas** Integrated Detector Electronics AS

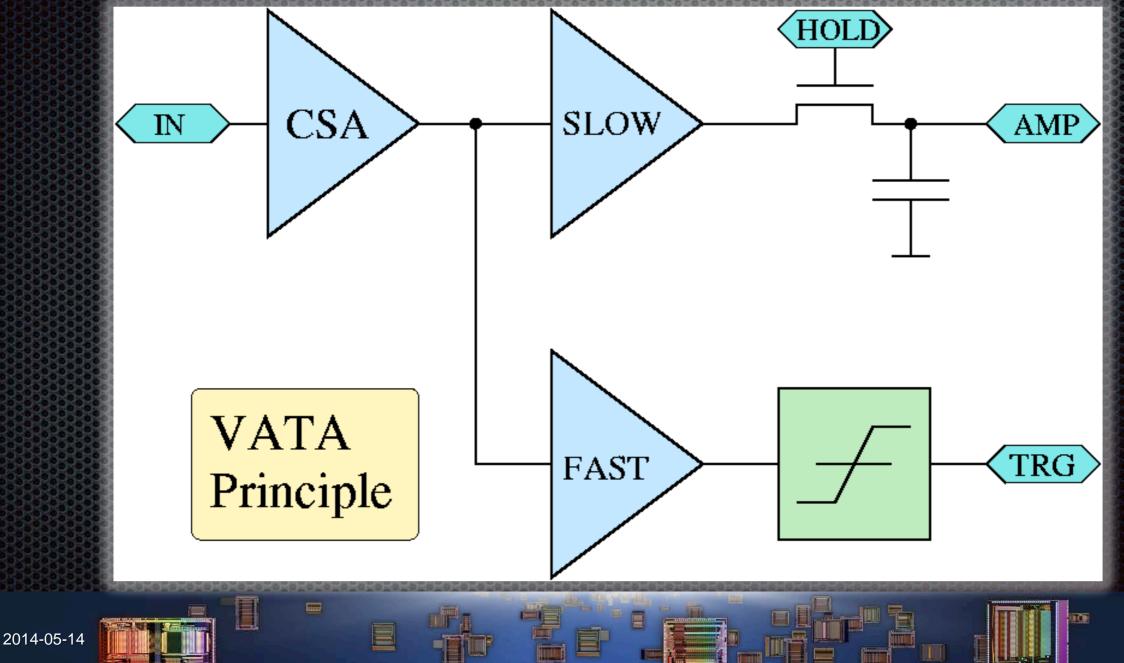

### VATA - family ASICs

ASICs for spectroscopy with on-chip trigger, system driven

## IDE 3465 – NGRM

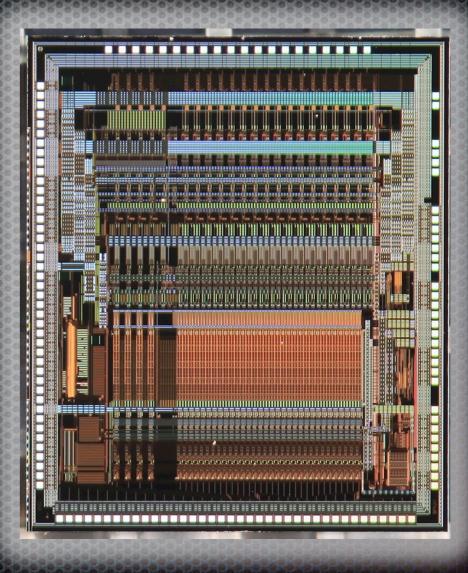

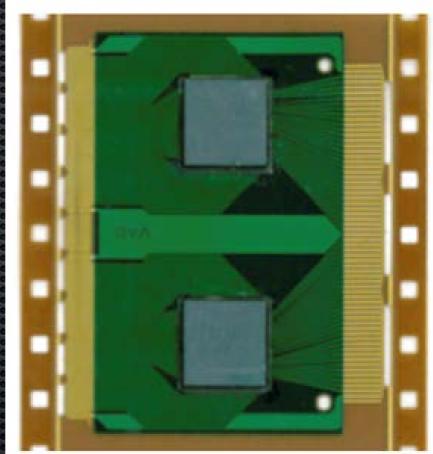

The IDE 3465 is an application specific integrated circuit (ASIC) that has been designed for the readout of the p-side of silicon detectors.

|                  |                   | ŏ.     |

|------------------|-------------------|--------|

| Supplier         | IDEAS             | 00000  |

| Wafer fab        | AMS               | 0000   |

| Technology       | 0.35 μm CMOS      | 000000 |

| Epitaxial layer  | Yes               | 0000   |

| Metal Layers     | 4                 |        |

| Capacitor option | Double poly       | 00000  |

| Chip dimensions  | 6045 μm × 7140 μm | 00000  |

## IDE 3465 – NGRM

|                                  |                                                             | 0000000  | 265 | 0000     |                                            |   |              |

|----------------------------------|-------------------------------------------------------------|----------|-----|----------|--------------------------------------------|---|--------------|

| 20 charge                        | < 2.6 pC in 16 high-gain channels                           | 000      | _   |          | HOLDB                                      |   |              |

| sensitive inputs                 | < 26 pC in 4 low-gain channels                              | In0      |     |          | 16 high-gain channels                      |   |              |

| 37 digital logic trigger outputs | 32 outputs from the 2 comparators in the high-gain channels | In15     |     |          |                                            |   |              |

|                                  | 4 outputs from the comparator in the low-gain channels      | 0000     |     | ADEMUX   |                                            |   | T_OUT0A      |

|                                  | 1 OR from all comparators                                   |          |     | AD       | threshold DAC                              |   | <br>T_OUT15A |

| 1 analogue                       | Pulse height spectroscopy from all channels                 | 0000     |     |          |                                            |   | T_OUT0B      |

| output                           |                                                             | 000      |     |          | threshold DAC                              |   | T_OUT15B     |

| Noise                            | 0.45 fC ENC in high-gain channels                           | In16     |     |          | 4 low-gain channels                        |   |              |

|                                  | 5 fC ENC in low-gain channels                               | <br>In19 |     |          |                                            |   |              |

| Trigger                          | 1.5 fC and 71 fC in high-gain channels                      |          | •   |          |                                            |   |              |

| threshold,                       | 150 fC in low-gain channels                                 | 000      |     | ×        |                                            |   |              |

| minimum                          |                                                             |          |     | EMU      |                                            |   | T_OUT16      |

| Power                            | 62.5 mW maximum, typical consumption 50 mW                  |          |     | ADI      |                                            |   | <br>T_OUT19  |

| Rate,                            | > 1 Mcps/channel capability at the trigger outputs          | 000      |     |          |                                            |   |              |

| maximum                          | > 2.5 kcps/channel with analogue readout of all             | 000      |     | ×        | SC_CLK REGIN DRESET RO_CLK SHIFT_IN        | 4 | T_OUT        |

|                                  | channels                                                    |          |     | ADEMUX   | D RES D RES TOR                            | T | 1_001        |

| Radiation                        | The chip is SEL immune (SEL LET <sub>th</sub> >100          |          |     | AD       | Bias Network Configuration                 |   | T_OUTB       |

| tolerance                        | MeV/mg/cm2)                                                 |          |     | T        |                                            | - | AOUTP        |

|                                  | The chip is radiation tolerant by design and                | 000      |     | <b>_</b> |                                            |   | AOUTM        |

|                                  | manufacture, with respect to single event upsets            | 000      |     | CAL      | MBIAS REGOUT READ_BACK LOAD SHIFT_OUT VREF |   |              |

2014-05-14

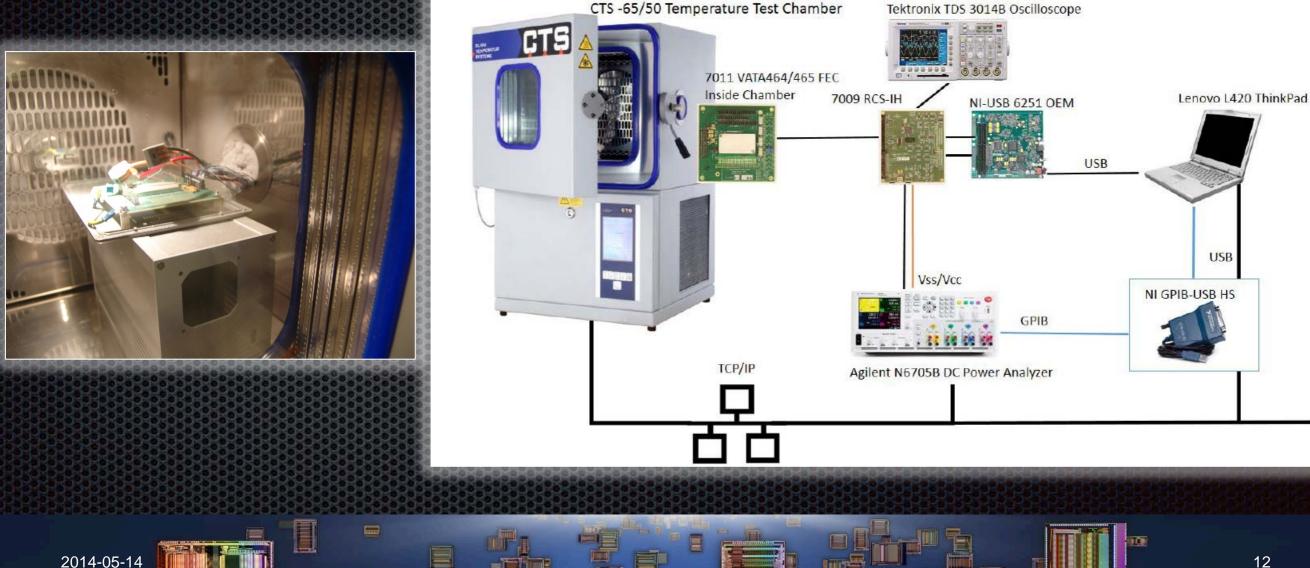

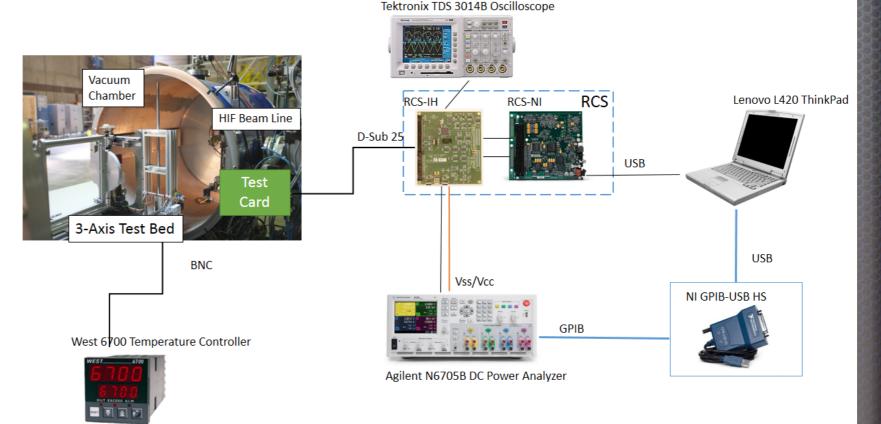

#### Design validation – temperature

Validated operating temperature -65°C to +40°C at IDEAS

#### **Design validation – radiation**

#### SEE tests performed at UCL SEL<sub>th</sub> >116 MeVcm<sup>2</sup>/mg 80°C ASIC temperature in accordance with ESCC 25100

#### **NGRM ASIC** validation

2014-05-14

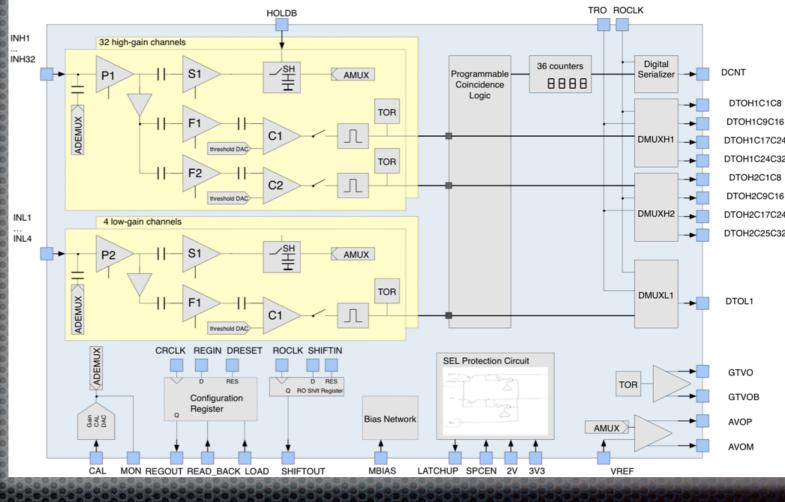

# IDE 3466 – RADEM

The IDE 3466 is an application specific integrated circuit (ASIC) for RADEM with heritage from IDE 3465.

#### **Features**

On-chip event counting

SEL protection circuit

32 HG channels and 4 LG channels

Dynamic range: 2.6 fC HG 26 fC LG

Radiation hard by design

2014-05-14

### IDE 3466 – RADEM

Validation with functional, performance and operational testing SEM testing in accordance with ESCC-21400 Radiation testing in accordance to ESCC-25100 and ESCC-22900

# VAI – family ASICs

ASICs with current integrators

# VA SCM3.2

The VS\_SCM3.2 is a current integrator ASIC designed to read out a variety of detectors

#### **Continuus current integration mode**

Correlated double sampling mode

128 input channels

Multiple pre-amplifier gain settings

Dynamic range ±20 pC

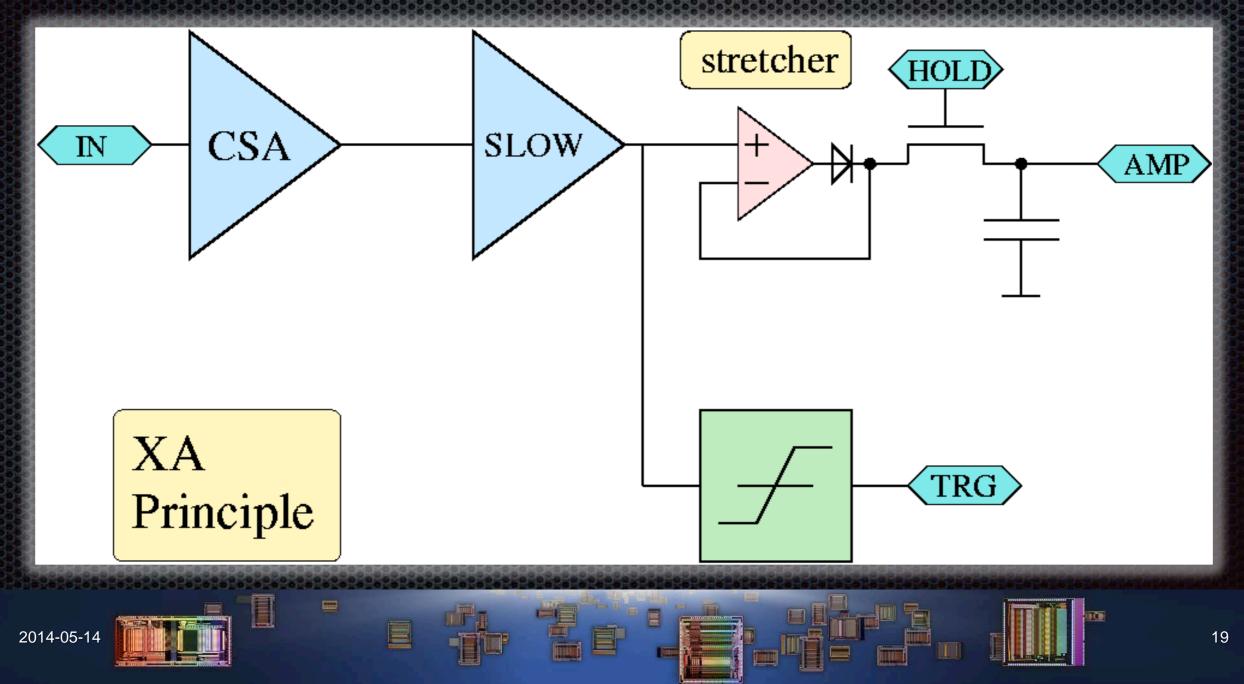

## XA – family ASICs

ASICs for spectroscopy with on-chip trigger, self-triggering

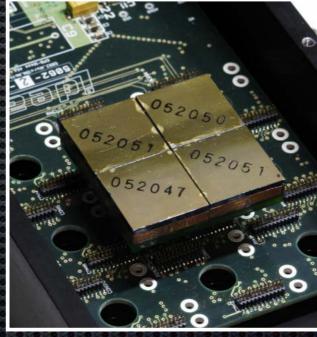

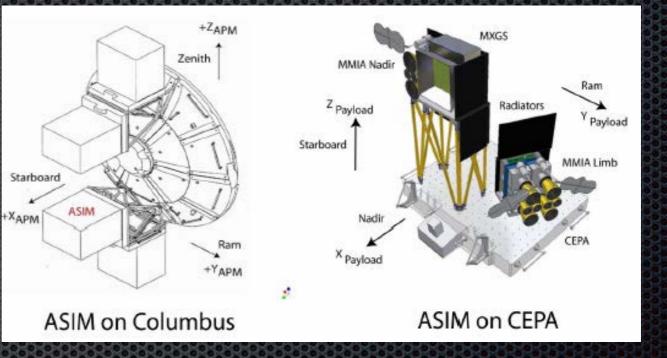

# XA1.83 – ASIM

The XA 1.83 is an application specific integrated circuit (ASIC) that has been designed for the readout of CZT pixelated radiation detectors

Each CZT pixel measures energy from 20 keV to 360 keV A total of 128 ASICs (16384 channels) of XAs will be used in the Atmosphere Space Interaction Monitor (ASIM).

Trigger address encoding

65536 channels can be daisy-chained

Temperature drift compensation

Also used in LumaGEM Molecular Breast Imaging camera

XA1.83

To:

### XA1.83

| Parameter                  | Value                      | Comment                                                                                                                       |

|----------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Number of Input Channels   | 128                        | Readout for 128 pixels                                                                                                        |

| Input charge dynamic range | 012.5 fC                   | Negative charge, readout of anodes                                                                                            |

| Power consumption          | 0.5 mW/channel             | 64 mW total (nominal setting)                                                                                                 |

| Electronic noise of CSA    | 130 e + 20 e/pF            | At 0.5-µs shaping time.                                                                                                       |

|                            |                            | Measured energy resolution is 5.4<br>keV FWHM at 122 keV in CZT pixels                                                        |

| Threshold                  | 0.3 fC, negative charge    | 10 keV in CZT                                                                                                                 |

| Rate capability, maximum   | 20 kHz 100 kHz per<br>ASIC | Highest rate tested with this ASIC is<br>20 kHz. Depending on system<br>configuration, >100 kHz is expected<br>to be possible |

| Detector Capacitance       | 0 pF 10 pF                 | Optimized for 4pF                                                                                                             |

| Detector Leakage Current   | 0 nA – 100 nA              | Positive current out of the<br>preamplifiers                                                                                  |

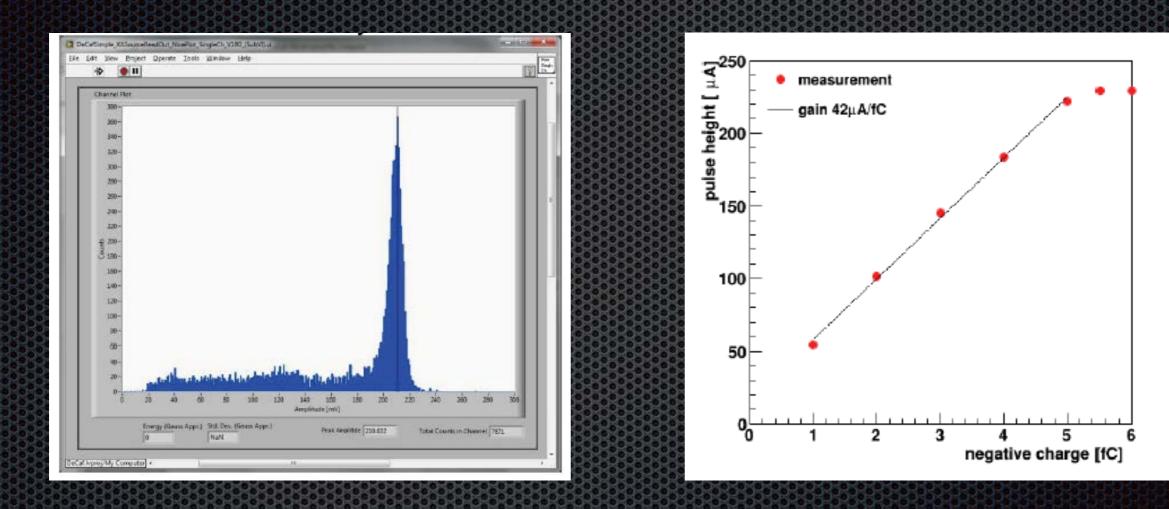

### XA1.83

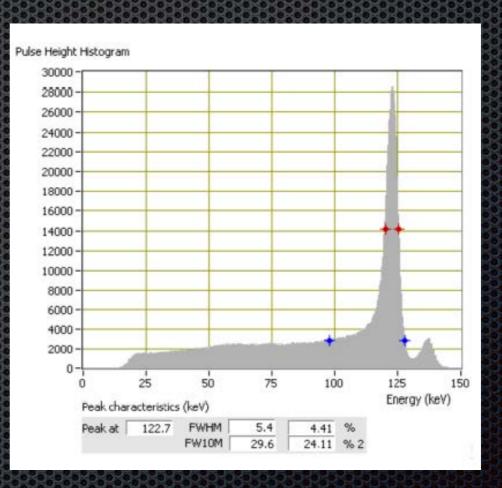

## 5.4 keV FWHM at Co-57 122 keV, all pixels summed.

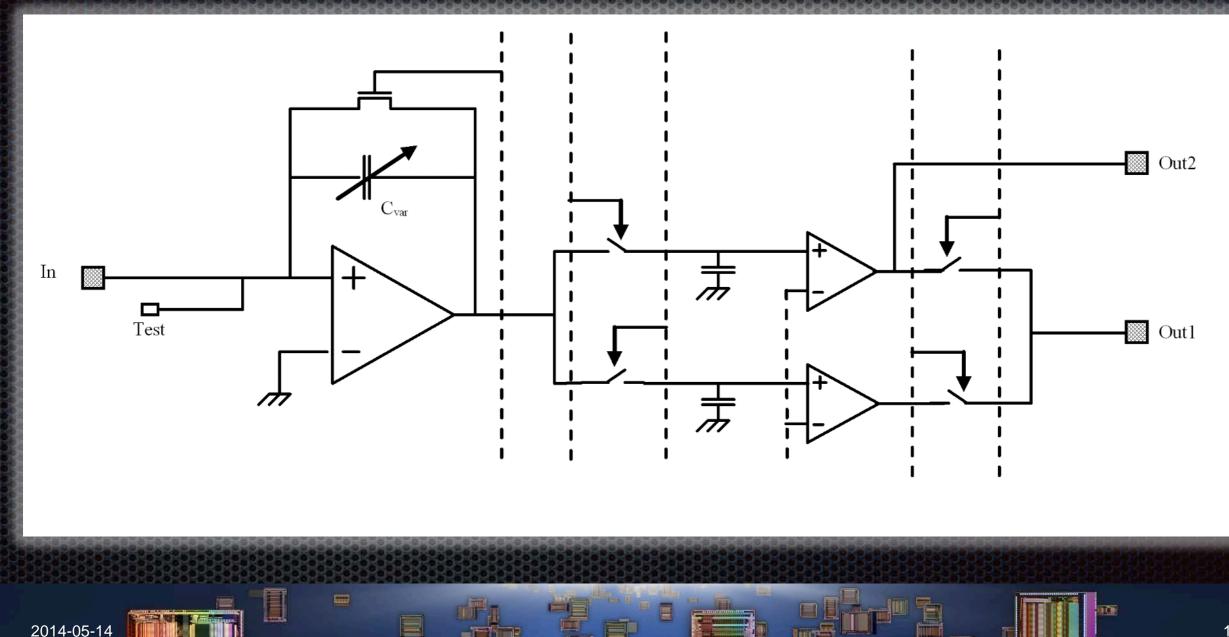

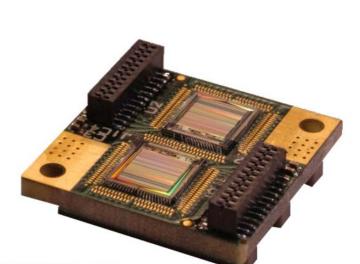

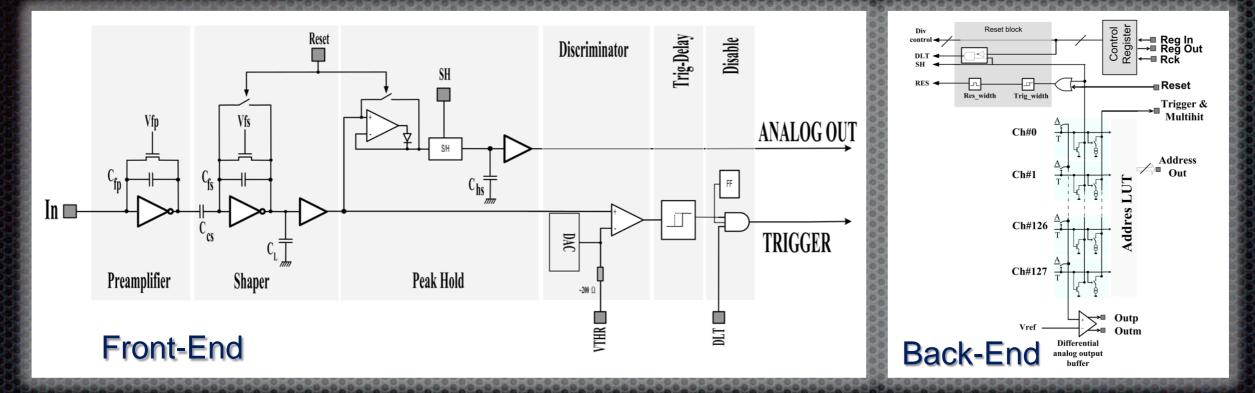

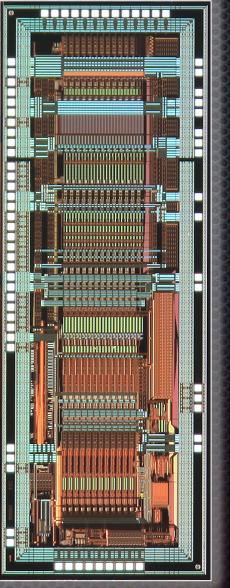

## IDE 4281

The IDE 4281 is an application specific integrated circuit (ASIC) that has been designed for the readout of CdTe/CZT radiation detectors in space.

Single photon spectroscopy of x-rays and  $\gamma$ -rays with energy between 3.5 keV and 140 keV @100 kHz per chip

12 channels

Programmable peaking time

Trigger address encoding

19 mW idle/25 mW maximum

Radiation hard by design

The ASIC was designed for the STIX detector unit. STIX is one of 10 instruments on board Solar Orbiter, a confirmed M-class mission of the European Space Agency to be launched in 2017. STIX has 32 pixelated CdTe detectors for detection of hard x-ray emissions from 4 keV to 150 keV. STIX foresees using the IdeF-X HD chip [Meuris et al., IEEE TNS, April 2008]. The IDE 4281 was an alternative chip solution for STIX.

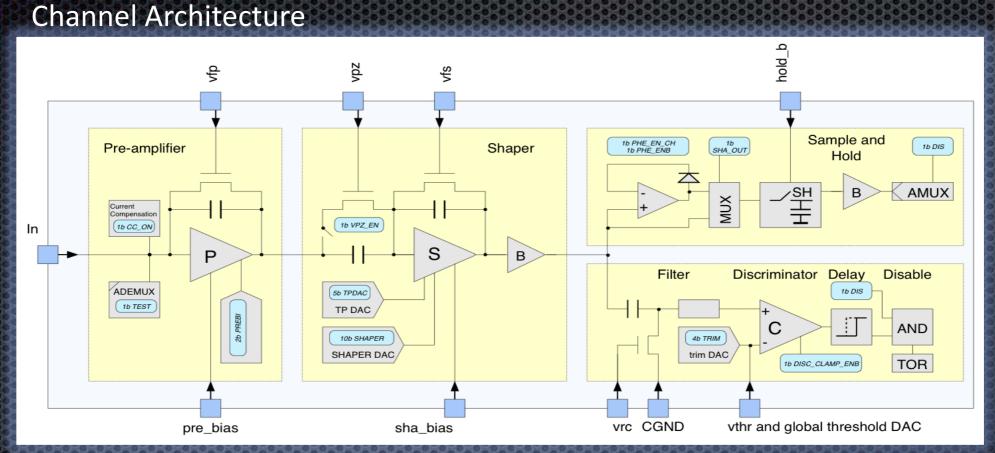

# IDE 4281

Charge Sensitive Pre-amplifier (P)

- Programmable Shaper (S), Pole-Zero Cancellation

- Stretcher (peak-hold devices), sample and hold (SH)

- Analogue Multiplexer Readout (AMUX)

- Comparators (C), programmable reference

- Mono-stable Trigger Outputs, Trigger OR (TOR)

#### **Radiation tolerant/hardened library**

- Full custom guard rings against SEL

- Epitaxial layer process against SEL

- Triple redundant flip-flops correct for SEU

- Sub-µm CMOS technology improves TID

- SEL/SEU LET<sub>th</sub> > 67.7 MeVcm2/mg

### IDE 4281

Pulse height spectrum from a channel at +21°C, γ from Am-241, eV-Products CZT.