## ARBUS MathWorks®

## **Accelerating FPGA Development**

Harnessing the Power of HDL Coder and Collaborative Integration with NanoXplore

#### Yanitsa Stoyanova

Digital Design and Verification Engineer Airbus Defence and Space

#### Stephan van Beek

European Technical Specialist SoC/FPGA Design Flows MathWorks

© 2023 The MathWorks, Inc.

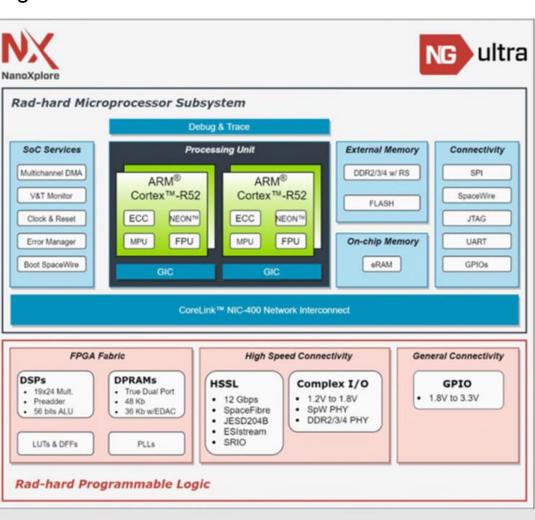

## Project, feasibility studies

H2020 OPERA Project has received funding from the European Union's H2020 research and innovation program under grant agreement N°821969

Space Qualification and Validation of High Performance European Rad-Hard FPGA

AIRBUS

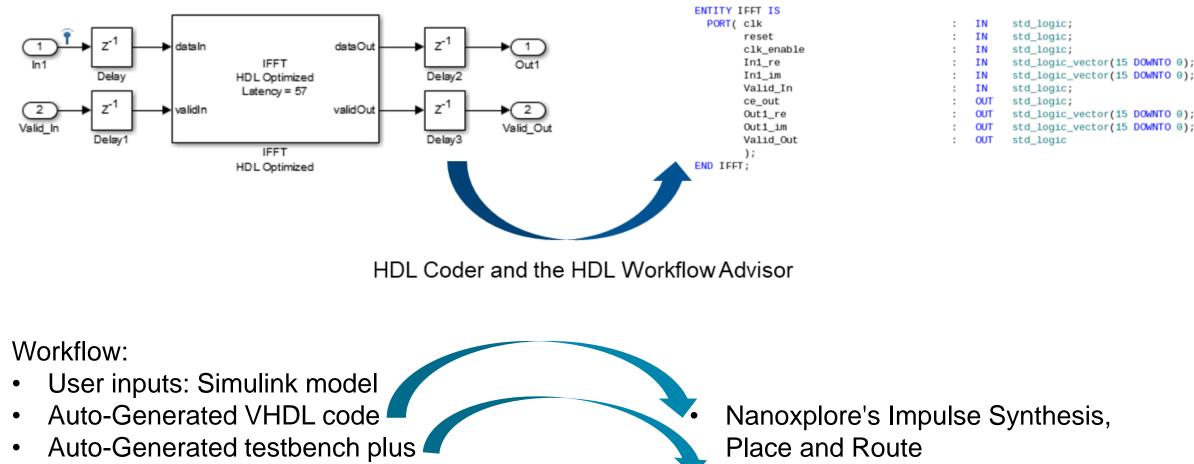

## **Digital Signal Processing Algorithms Flow with HDL Coder**

stimuli vectors for RTL simulations

Netlist simulations

#### AIRBUS

**AIRBUS**

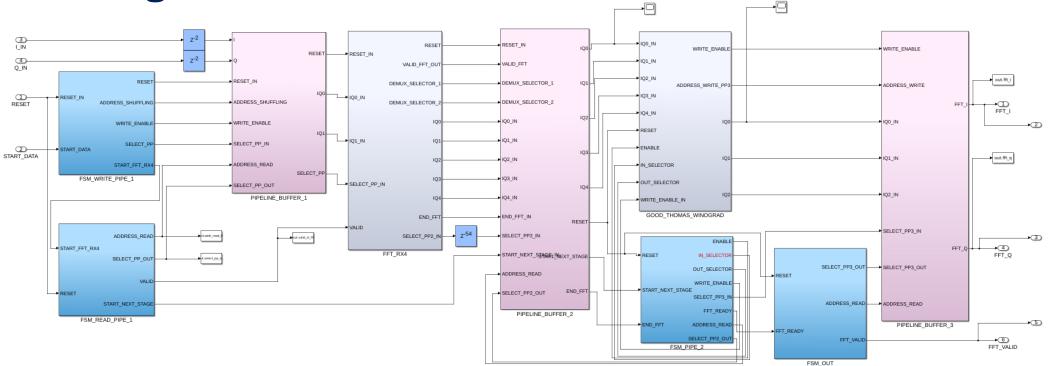

## FFT240 design model

#### Workflow:

- User inputs: Simulink model

- Auto-Generated VHDL code

- Auto-Generated testbench plus stimuli vectors for RTL simulations

- Nanoxplore's Impulse Synthesis,

- Place and Route

- Netlist simulations

## **FFT240 design requirements**

#### Required : 180 MHz

| NxMap 22.2.0.4         |        | fft240, no cor | istraints |      | orplanning,<br>ng driven | fft240, floorplanning,<br>timing driven |          |  |  |

|------------------------|--------|----------------|-----------|------|--------------------------|-----------------------------------------|----------|--|--|

| Ressource              | total  | abs relative   |           | abs  | relative                 | abs                                     | relative |  |  |

| 4-LUT                  | 505344 | 2988           | 0.59%     | 7959 | 1.57%                    | 7959                                    | 1.57%    |  |  |

| DFF                    | 505344 | 5807           | 1.15%     | 7078 | 1.40%                    | 7079                                    | 1.40%    |  |  |

| Carry                  | 126336 | 1374           | 1.09%     | 1120 | 0.89%                    | 1120                                    | 0.89%    |  |  |

| RFB                    | 2632   | 64             | 2.43%     | 0    | 0.00%                    | 0                                       | 0.00%    |  |  |

| DSP                    | 1344   | 22             | 1.64%     | 31   | 2.31%                    | 31                                      | 2.31%    |  |  |

| BRAM                   | 672    | 20             | 2.98%     | 24   | 3.57%                    | 24                                      | 3.57%    |  |  |

|                        |        |                |           |      |                          |                                         |          |  |  |

| clk (post syn) in MHz  |        | 213,995        |           | 206  | ,954                     | 206,954                                 |          |  |  |

| clk (post rout) in MHz |        | 131,19         | 9         | 178  | ,285                     | 183,993                                 |          |  |  |

## Garbage in = Garbage out

- Following good coding patterns is important (= good modelling patterns)

- Fortunately .... HDL Coder produces good code for NanoXplore Why is that??

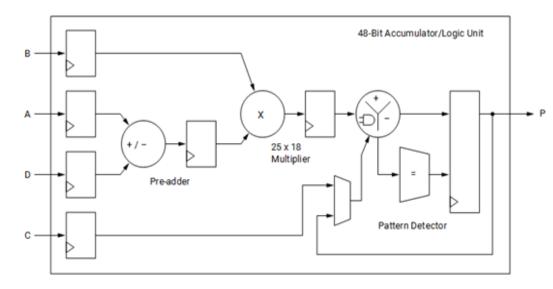

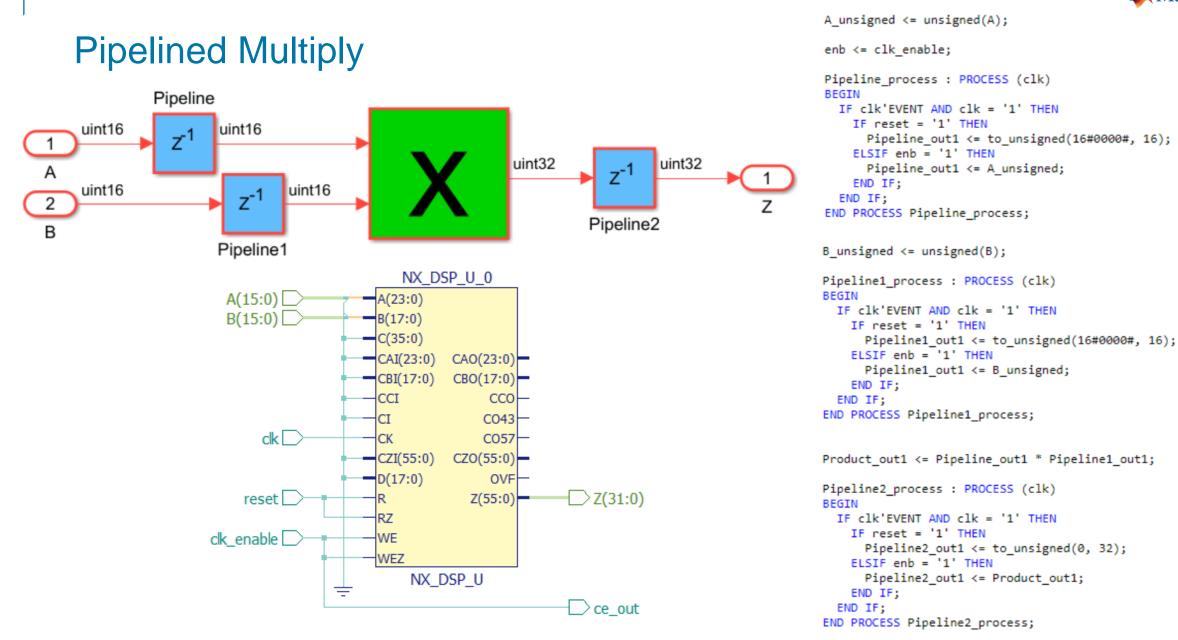

## DSP architecture NG Ultra and Xilinx are 'similar'

| Tool and Device             |                   |   |  |  |  |  |  |  |  |

|-----------------------------|-------------------|---|--|--|--|--|--|--|--|

| Synthesis Tool:             | Xilinx Vivado     |   |  |  |  |  |  |  |  |

| Family:                     | Artix UltraScale+ | • |  |  |  |  |  |  |  |

| Package:                    | <empty></empty>   | • |  |  |  |  |  |  |  |

| Objectives Setting          | js                |   |  |  |  |  |  |  |  |

| Target Frequency (MHz): 150 |                   |   |  |  |  |  |  |  |  |

#### Hardware-Efficient Pipelining Settings

Adaptive pipelining

Xilinx

NanoXplore

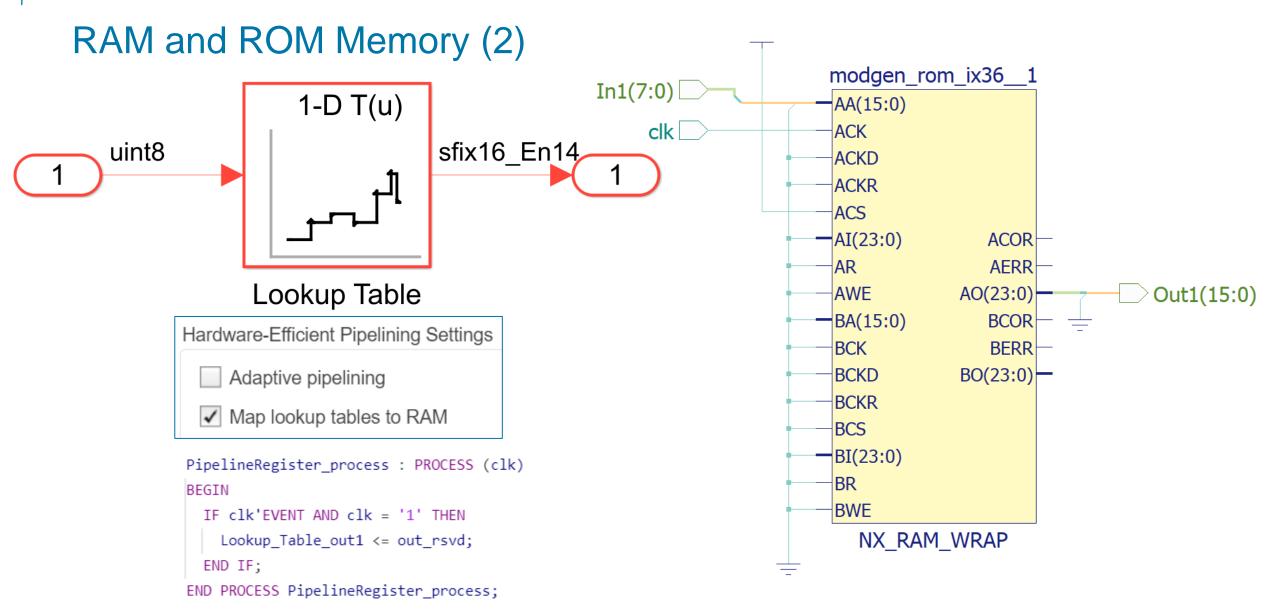

Map lookup tables to RAM

**Distributed Pipelining Settings**

Distributed pipelining

7

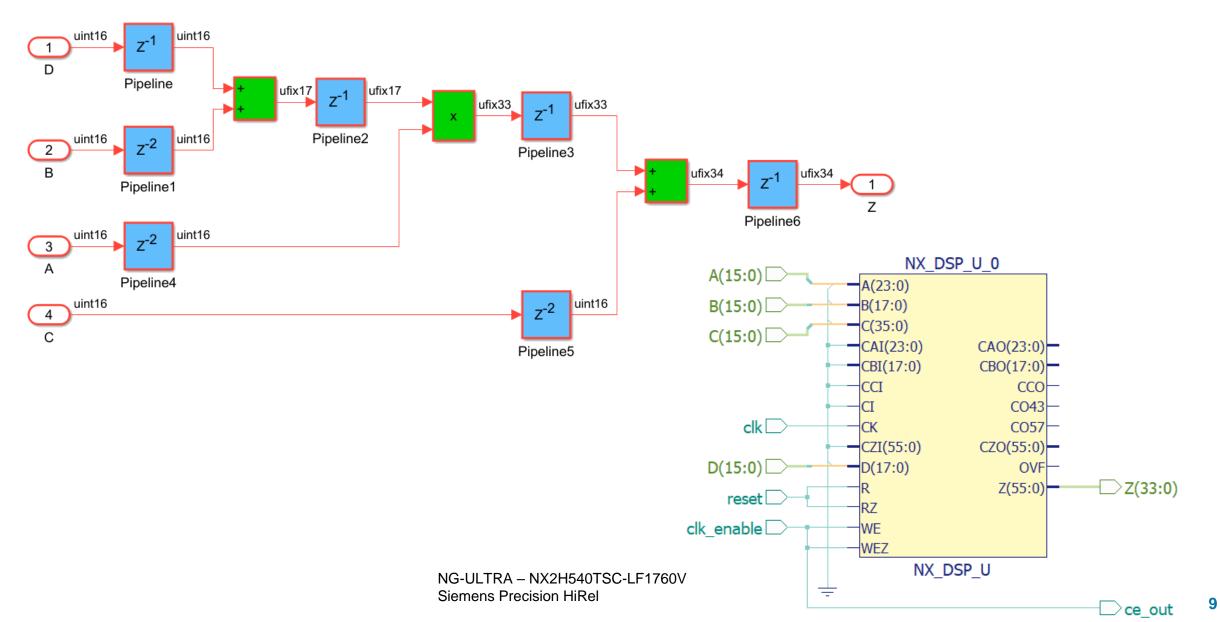

NG-ULTRA – NX2H540TSC-LF1760V Siemens Precision HiRel

Z <= std\_logic\_vector(Pipeline2\_out1);</pre>

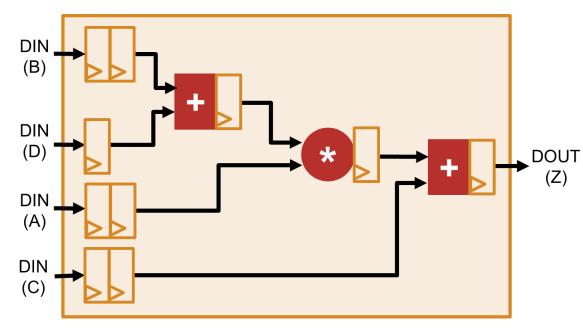

## Pipelined Multiply-Add with Pre-Adder

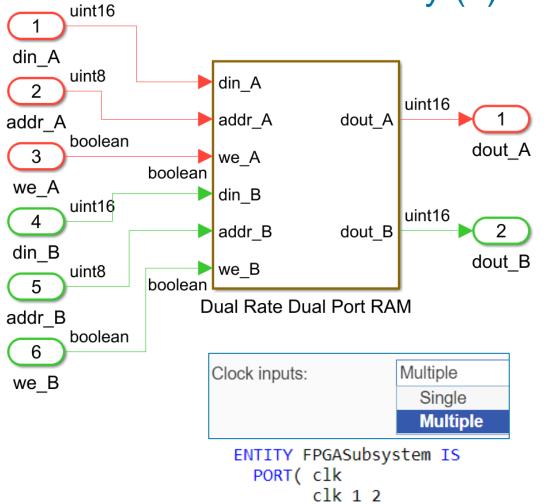

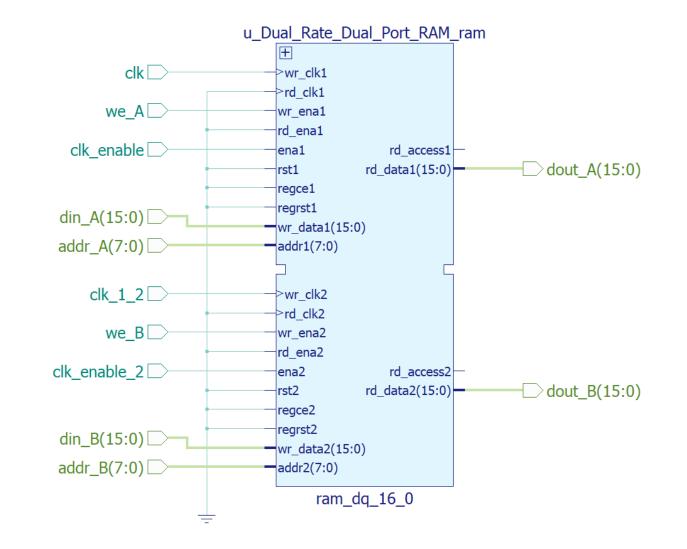

## RAM and ROM Memory (1)

clk\_enable clk\_enable\_2

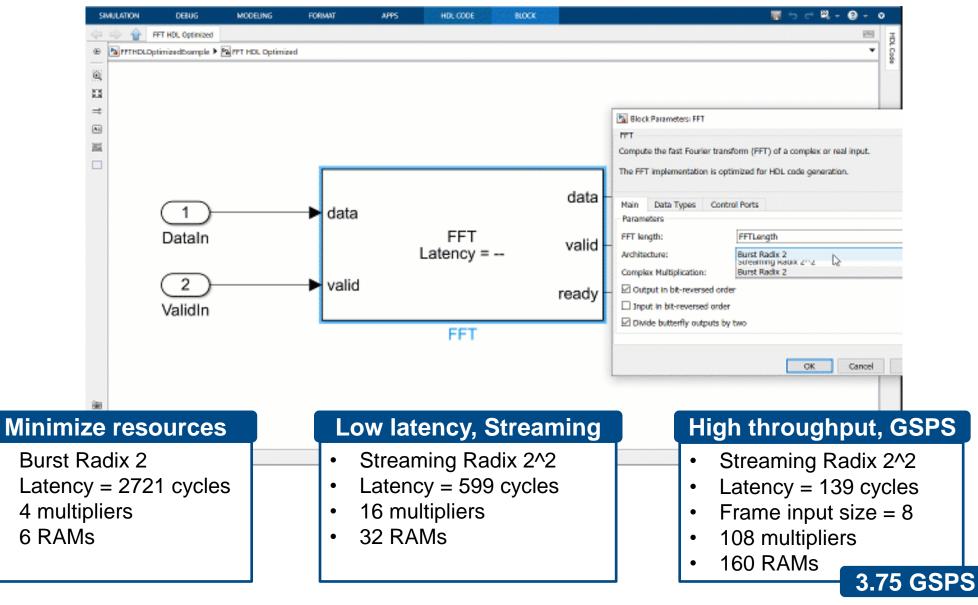

## **FFT Implementation Exploration**

٠

.

•

٠

| Collaboration with                                                                                                                                                                                                                                                                                                                                                                                                                          | NanoXplore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | N                                                                                                | lultipliers                                                                                                                               |                                | 16                |                                                                               |                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A                                                                                                | dders/Subtracto                                                                                                                           | rs                             |                   | 191                                                                           |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R                                                                                                | egisters                                                                                                                                  |                                |                   | 647                                                                           |                                                                 |

| sfix16_En13 (c) D1                                                                                                                                                                                                                                                                                                                                                                                                                          | sfix25_En13 (c) D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | То                                                                                               | otal 1-Bit Registe                                                                                                                        | ers                            |                   | 8504                                                                          |                                                                 |

| data<br>Dataln FFT                                                                                                                                                                                                                                                                                                                                                                                                                          | data $1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                | AMs                                                                                                                                       |                                |                   | 32                                                                            |                                                                 |

| DataIn FFT Latency =                                                                                                                                                                                                                                                                                                                                                                                                                        | DataOut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N                                                                                                | Iultiplexers                                                                                                                              |                                |                   | 461                                                                           |                                                                 |

| 2 valid                                                                                                                                                                                                                                                                                                                                                                                                                                     | valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                  | I/O Bits                                                                                                                                  |                                |                   | 86                                                                            |                                                                 |

| alidIn                                                                                                                                                                                                                                                                                                                                                                                                                                      | ValidOut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                  | atic Shift operat                                                                                                                         | ors                            |                   | 8                                                                             |                                                                 |

| FFT51                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                  | ynamic Shift ope                                                                                                                          |                                |                   | 0                                                                             |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                  |                                                                                                                                           |                                |                   |                                                                               | +                                                               |

| Instance Name                                                                                                                                                                                                                                                                                                                                                                                                                               | Out Net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Mode                                                                                             | AREG I BRE                                                                                                                                | G   CREG                       | ADREG             | MREG   PR                                                                     | +<br>EG                                                         |

| Instance Name                                                                                                                                                                                                                                                                                                                                                                                                                               | Out Net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                  | AREG   BRE                                                                                                                                | G   CREG                       |                   |                                                                               | EG  <br>+                                                       |

| L.  u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0                                                                                                                                                                                                                                                                                                                                                                                                      | )   RETIMED_rtlcGen22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B*A                                                                                              | 2   2                                                                                                                                     | 0                              | I - I             |                                                                               | +<br>EG  <br>+<br>                                              |

| L.  u_FFT.u_SDF1_3_1.u_MOL4.NX_DSP_U_0<br>2.  u_FFT.u_SDF1_3_1.u_MOL4.NX_DSP_U_1                                                                                                                                                                                                                                                                                                                                                            | )   RETIMED_rtlcGen22<br>L   RETIMED_rtlcGen18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B*A<br>  B*A                                                                                     |                                                                                                                                           | 2G   CREG<br>  0<br>  0<br>  1 |                   |                                                                               | +<br>EG  <br>+<br> <br>                                         |

| .   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.  u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.  u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2                                                                                                                                                                                                                                                                                                                  | 0   RETIMED_rtlcGen22<br>L   RETIMED_rtlcGen18<br>2   dinXTwdl_re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | B*A<br>  B*A<br>  A*B-C                                                                          | 2   2<br>  2   2<br>  0   0                                                                                                               | 0                              | -  <br> -  <br> - | 0   0<br>0   0<br>1   1                                                       | +<br>EG  <br>+<br> <br> <br>                                    |

| u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2 u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3 u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4 u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3                                                                                                                                                                                                                                                                                  | D   RETIMED_rtlcGen22<br>L   RETIMED_rtlcGen18<br>2   dinXTwdl_re<br>3   dinXTwdl_im                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B*A<br>  B*A                                                                                     | 2   2<br>  2   2<br>  0   0                                                                                                               | 0                              |                   | 0   0<br>0   0<br>1   1<br>1   1                                              | EG  <br>+<br> <br> <br> <br> <br>                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B*A<br>  B*A<br>  A*B-C<br>  A*B+C                                                               | 2   2<br>  2   2<br>  0   0<br>  0   0                                                                                                    | 0<br>  0<br>  1<br>  1         |                   | 0   0<br>0   0<br>1   1                                                       | EG  <br> +<br> <br> <br> <br> <br> <br>                         |

| L.  u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.  u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.  u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.  u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3                                                                                                                                                                                                                                                                        | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A                                                      | 2   2<br>  2   2<br>  0   0<br>  0   0<br>  2   2                                                                                         | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>  0   0<br>  1   1<br>  1   1<br>  0   0                             | +<br>EG  <br> <br> <br> <br> <br> <br> <br>                     |

| L.  u_FFT.u_SDF1_3_l.u_MUL4.NX_DSP_U_0<br>2.  u_FFT.u_SDF1_3_l.u_MUL4.NX_DSP_U_1<br>3.  u_FFT.u_SDF1_3_l.u_MUL4.NX_DSP_U_2<br>4.  u_FFT.u_SDF1_3_l.u_MUL4.NX_DSP_U_3<br>5.  u_FFT.u_SDF1_5_l.u_MUL4.NX_DSP_U_0<br>6.  u_FFT.u_SDF1_5_l.u_MUL4.NX_DSP_U_1<br>7.  u_FFT.u_SDF1_5_l.u_MUL4.NX_DSP_U_2                                                                                                                                          | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A                                             | 2   2     2   2     0   0     0   0     2   2     2   2     2   2     2   2                                                               | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>  0   0<br>  1   1<br>  1   1<br>  0   0<br>  0   0                  | +<br>EG  <br> <br> <br> <br> <br> <br> <br> <br>                |

| 1.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3<br>5.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_0<br>6.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_1<br>7.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_2<br>8.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_3                                                                                        | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A<br>  A*B-C<br>  A*B+C                       | 2   2     2   2     0   0     0   0     2   2     0   0     2   2     2   2     0   0                                                     | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>  0   0<br>  1   1<br>  1   1<br>  0   0<br>  0   0<br>  1   1       | +<br>EG  <br>      |

| 1.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3<br>5.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_0<br>6.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_1<br>7.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_2<br>8.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_3<br>9.   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_0                                             | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  A*B              | 2   2     2   2     0   0     0   0     2   2     0   0     2   2     2   2     0   0     2   2     0   0     0   0                       | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>0   0<br>1   1<br>1   1<br>0   0<br>0   0<br>1   1<br>1   1          | +<br>EG  <br>      |

| 1.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3<br>5.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_0<br>6.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_1<br>7.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_2<br>8.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_3<br>9.   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_0                                             | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   Complex4Multiply_mult2_im_pipel_5n0r<br/>L   Complex4Multiply_mult2_re_pipel_5n0r</pre>                                                                                                                                                                                                                                                                                                                                                             | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  A*B              | 2   2     2   2     0   0     0   0     2   2     2   2     2   2     2   2     0   0     1   1                                           | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>0   0<br>1   1<br>1   1<br>0   0<br>0   0<br>1   1<br>1   1<br>1   1 | EG  <br> <br> <br> <br> <br> <br> <br> <br> <br>                |

| 1.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3<br>5.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_0<br>6.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_1<br>7.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_2<br>8.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_3<br>9.   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_0<br>0.   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_1  | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   Complex4Multiply_mult2_im_pipel_5n0r<br/>L   Complex4Multiply_mult2_re_pipel_5n0r</pre>                                                                                                                                                                                                                                                                                                                                                             | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  A*B              | 2   2     2   2     0   0     0   0     2   2     2   2     2   2     2   2     0   0     1   1                                           | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>0   0<br>1   1<br>1   1<br>0   0<br>0   0<br>1   1<br>1   1<br>1   1 | EG  <br>           |

| 1.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3<br>5.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_0<br>6.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_1<br>7.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_2<br>8.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_3<br>9.   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_0<br>0_   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_1  | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   Complex4Multiply_mult2_im_pipel_5n0r<br/>L   Complex4Multiply_mult2_re_pipel_5n0r</pre>                                                                                                                                                                                                                                                                                                                                                             | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>1   A*B<br>1   A*B | 2   2     2   2     0   0     0   0     2   2     2   2     2   2     1   1     1   1                                                     | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>0   0<br>1   1<br>1   1<br>0   0<br>0   0<br>1   1<br>1   1<br>1   1 | EG  <br>           |

| 1.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3<br>5.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_0<br>6.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_1<br>7.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_2<br>8.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_3<br>9.   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_0<br>0_   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_1  | <pre>D   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re<br/>3   dinXTwdl_re<br/>3   dinXTwdl_im<br/>D   Complex4Multiply_mult2_im_pipel_5n0r<br/>L   Complex4Multiply_mult2_re_pipel_5n0r<br/>2   for Wultiply_triangle = 0.0000000000000000000000000000000000</pre>                                                                                                                                                                                                                                                                    | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>1   A*B<br>1   A*B | 2   2     2   2     0   0     0   0     2   2     2   2     2   2     1   1     1   1                                                     | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>0   0<br>1   1<br>1   1<br>0   0<br>0   0<br>1   1<br>1   1<br>1   1 | EG  <br> |

| 1.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_0<br>2.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_1<br>3.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_2<br>4.   u_FFT.u_SDF1_3_1.u_MUL4.NX_DSP_U_3<br>5.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_0<br>6.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_1<br>7.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_2<br>8.   u_FFT.u_SDF1_5_1.u_MUL4.NX_DSP_U_3<br>9.   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_0<br>10_   u_FFT.u_SDF1_7_1.u_MUL4.NX_DSP_U_1 | <pre>0   RETIMED_rtlcGen22<br/>L   RETIMED_rtlcGen18<br/>2   dinXTwdl_re<br/>3   dinXTwdl_im<br/>0   RETIMED_rtlcGen48<br/>L   RETIMED_rtlcGen44<br/>2   dinXTwdl_re<br/>3   dinXTwdl_re<br/>3   dinXTwdl_im<br/>0   Complex4Multiply_mult2_im_pipel_5n0r<br/>L   Complex4Multiply_mult2_re_pipel_5n0r<br/>2   for Multiply_mult2_re_pipel_5n0r<br/>2   for Multiply_mult2_re_pipel_5n0r<br/>2   for Multiply_mult2_re_pipel_5n0r<br/>3   for Multiply_mult2_re_pipel_5n0r<br/>3   for Multiply_mult2_re_pipel_5n0r<br/>3   for Multiply_mult2_re_pipel_5n0r<br/>2   for Multiply_mult2_re_pipel_5n0r<br/>3   for Multiply_mult2_re_pipel_5n0r</pre> | B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>  B*A<br>  B*A<br>  A*B-C<br>  A*B+C<br>1   A*B<br>1   A*B | 2   2<br>  2   2<br>  0   0<br>  0   0<br>  2   2<br>  2   2<br>  2   2<br>  2   2<br>  0   0<br>  0   0<br>  1   1<br>  1   1<br>  1   1 | 0<br>  0<br>  1<br>  1<br>  0  |                   | 0   0<br>0   0<br>1   1<br>1   1<br>0   0<br>0   0<br>1   1<br>1   1<br>1   1 | EG                                                              |

## FFT HDL - Optimized

Frequency without constraints :

• 135MHz @ worstcase

Frequency with floorplanning:

• 136MHz @ worstcase

Frequency with advanced floorplanning:

- 146MHz @ worstcase

- 150MHz can easily be reached

- 155-160MHz will be the limit

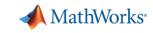

## FFT HDL - Optimized

#### 150MHz

| 1             | Domain           | ! | Freque         | ency   | !           | Hold/Removal                   | Summary                            |       | Setup/Recovery               | Summary                            |             | Status          |       |

|---------------|------------------|---|----------------|--------|-------------|--------------------------------|------------------------------------|-------|------------------------------|------------------------------------|-------------|-----------------|-------|

| Source        | Target           | F | tequired  <br> | Actual | Slack  <br> | Minimum Data  <br>Arrival Time | Minimum Required  <br>Relationship | Slack | Maximum Data<br>Arrival Time | Maximum Required  <br>Relationship | Slack  <br> | Delay  <br>Path | Total |

| Input         | MWCLK (Rising)   | 1 | - 1            | -      | -           | -1.434ns                       | -                                  | -     | 6.682ns                      | -                                  | -           | - [             | - #   |

| MWCLK (Rising | )   Output       | 1 |                |        | -           | 12.713ns                       | -                                  | -     | 19.301ns                     | -                                  | -           | - [             | - #   |

| MWCLK (Rising | ) MWCLK (Rising) |   |                |        |             |                                |                                    |       |                              | 6.666ns                            |             |                 |       |

| Total         |                  |   |                |        |             |                                |                                    |       |                              | 3                                  |             | -               |       |

## FFT HDL - Optimized

#### 150MHz

### **Concluding remarks**

# ARBUS + NX + + =