# NX FPGA Software Flow Impulse - Origins

27/11/2023

### Agenda

• The Origins

• Why Impulse is an advanced EDA Tool?

# The Origins

Since 2014

# Background

#### Alpine Peaks

Tacul

Jorasses

Cervin

#### Ambition

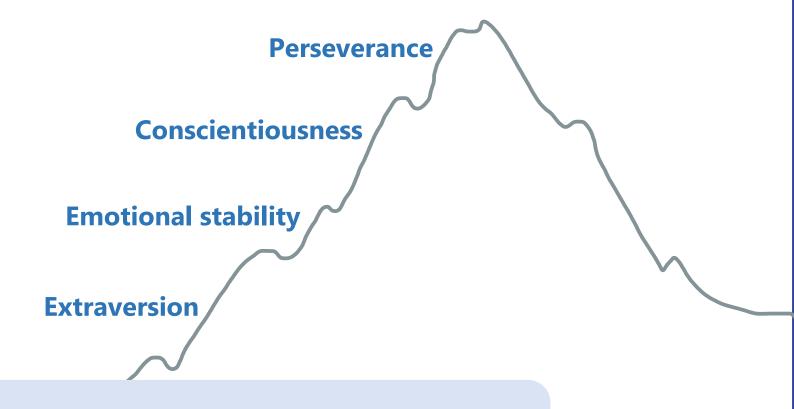

#### EDA software developer = Mountain climber

"One is not born, but rather becomes, an EDA software developer"

## Software Engineering Approach

- ✓ "Hello world"

- √ Feasibility

- ✓ Solved Synthesis & Routability problems

- ✓ Scalability Large matrix support

- ✓ Better memory handling

- ✓ Better Synthesis & Routability

- ✓ Ease of use

- ✓ Interface rethink to be user friendly

- ✓ Better Synthesis & Routability

- ✓ Advanced tools & reporting

- ✓ Knight Rider on NG-MEDIUM

- ✓ First deployment on end-users

- √ NG-ULTRA support

- ✓ Multiple design closures on NG-**MEDIUM**

- ✓ ULTRA300 support

- ✓ Big design closure on NG-ULTRA

- ✓ Over 100 end users

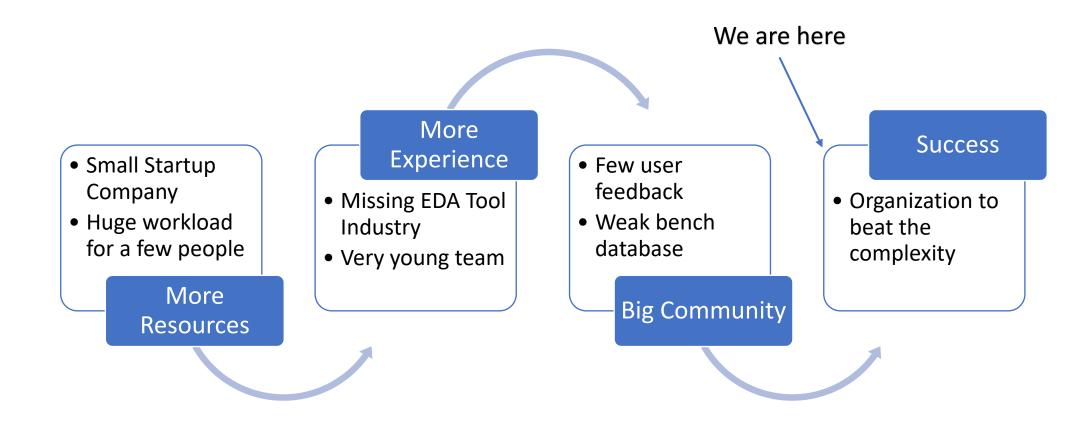

# Improving Every Day

Challenge: Performance

- Small Startup Company

- Huge workload for a few people

More Resources

### More Experience

- Missing EDA Tool Industry

- Very young team

- Few user feedback

- Weak bench database

**Big Community**

#### Success

Organization to beat the complexity

## Improving Every Day

Challenge: Performance

# Impulse

NX FPGA Software Flow

### Why you should use Impulse?

- Intuitive and easy to use

- Constant improvements and addition of new features

- Reactive support to guide users efficiently

- Open Minded and Open Source friendly

### Discover Impulse\*

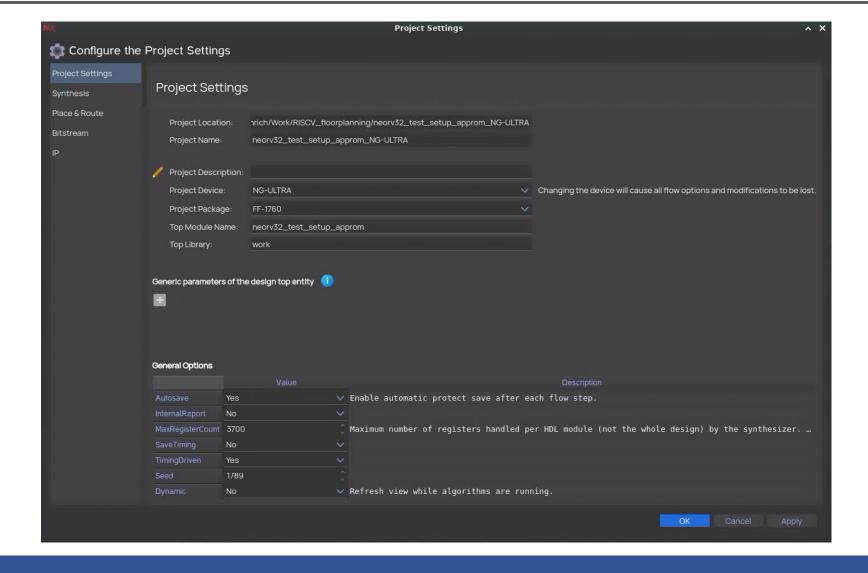

#### New UI

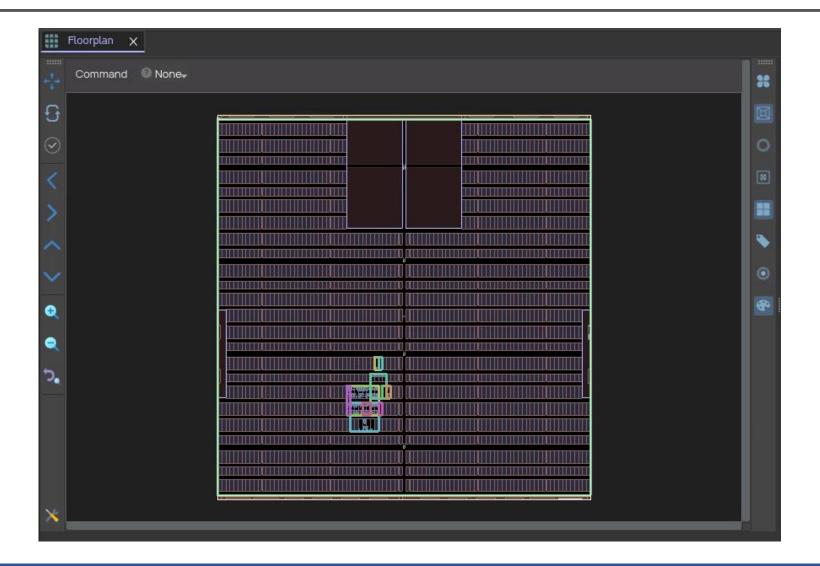

- ✓ Floorplanning

- ✓ Project Management

- ✓ Sources files Edition

- ✓ Constraints Edition

- ✓ Logs and Messages Navigator

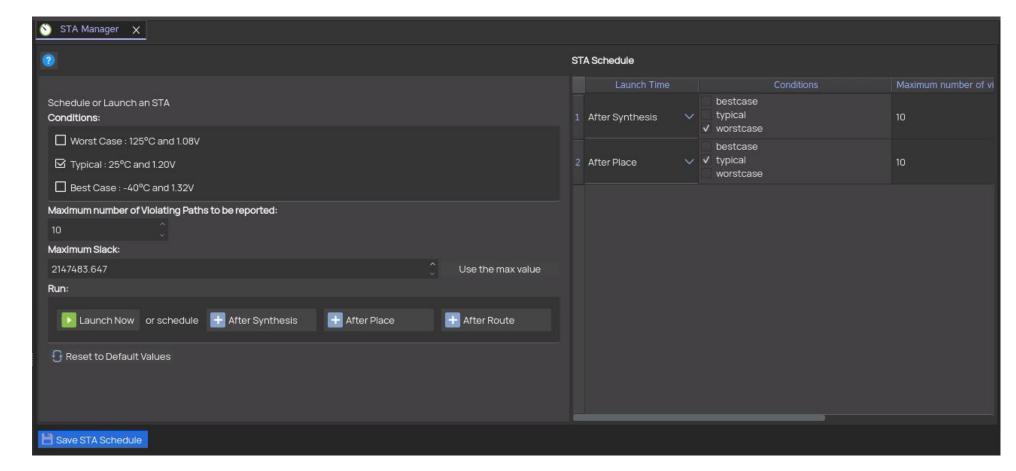

- ✓ STA Scheduler

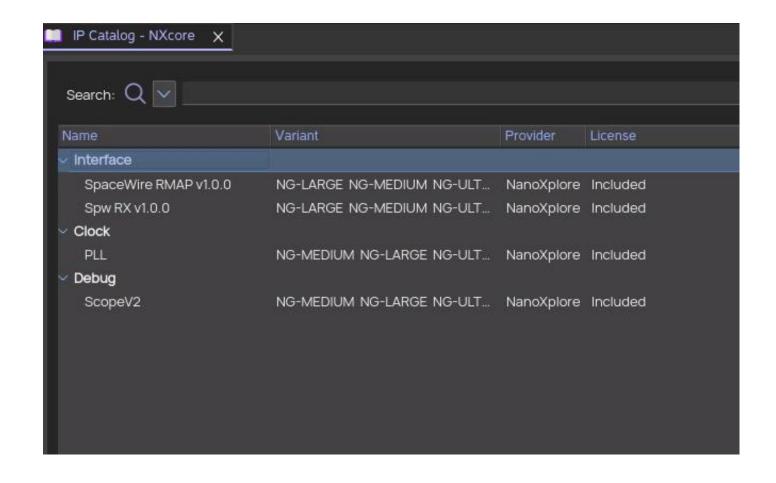

- ✓ Integrated IP Catalog

- ✓ Reports Reader

- ✓ Design & Hierarchy Complexity Report

- ✓ Preplace IP Methodology

- ✓ Faster STA Execution

\*: Probably the best EDA Tool in the world

# Basics: Project Settings

## Basics: IP Catalog

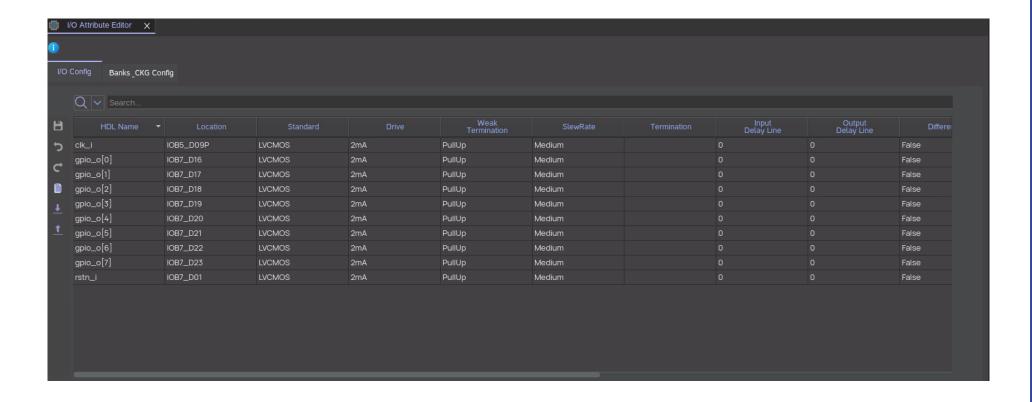

#### Basics: I/O Editor

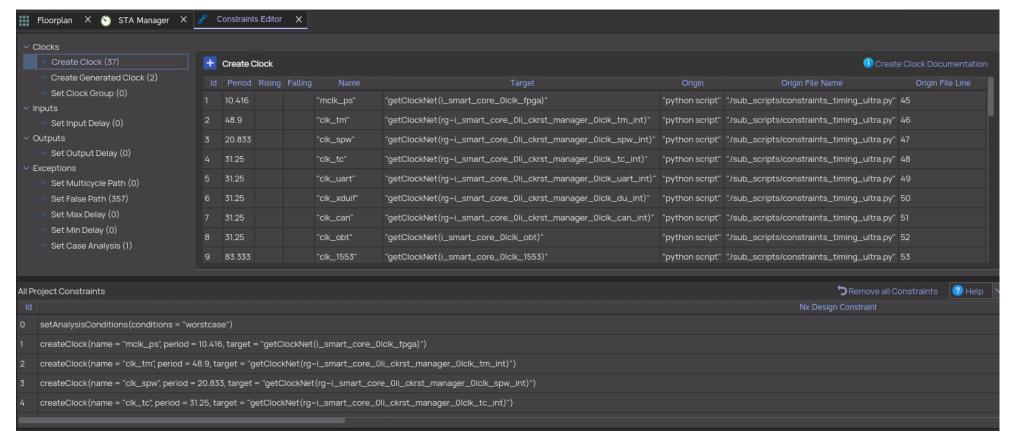

#### **Basics: Constraints Editor**

# Basics: Floorplan

### Basics: STA Manager

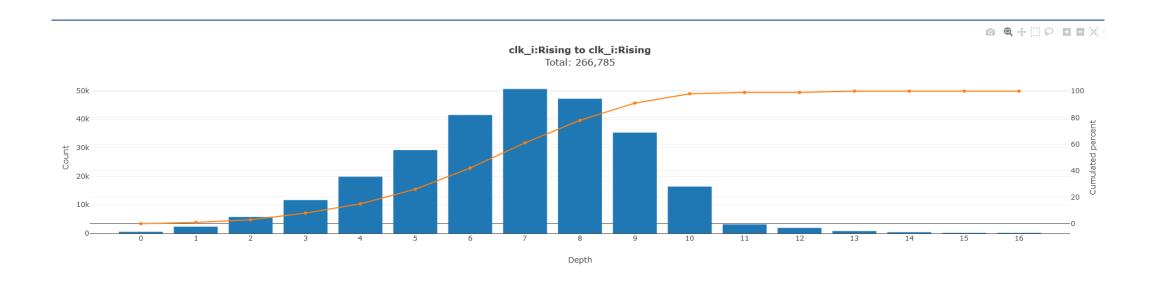

## Advanced: Design Complexity

Is the design FPGA friendly?

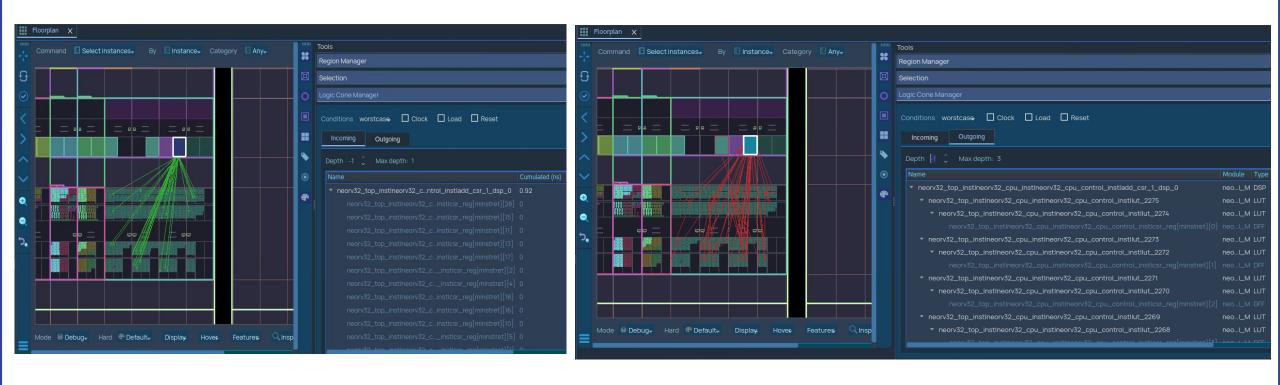

### Advanced: Logic Cone Manager

• Why instances are placed like this?

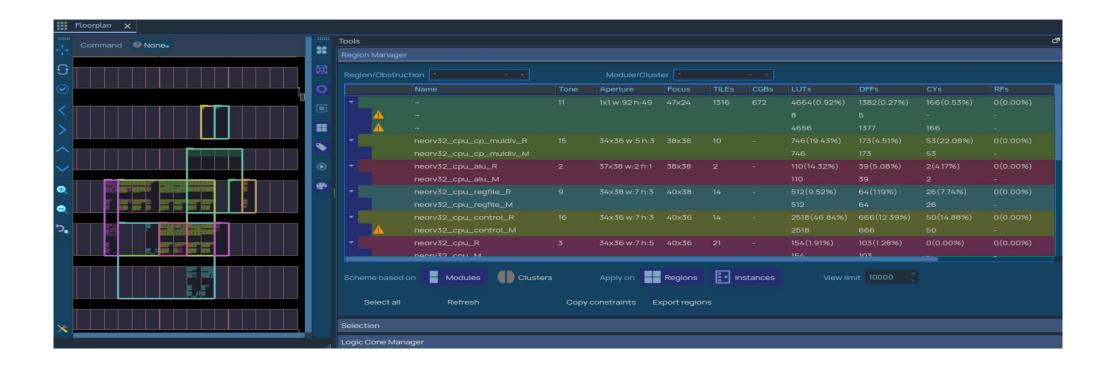

### Advanced: Regions

Let's help Impulse a little bit

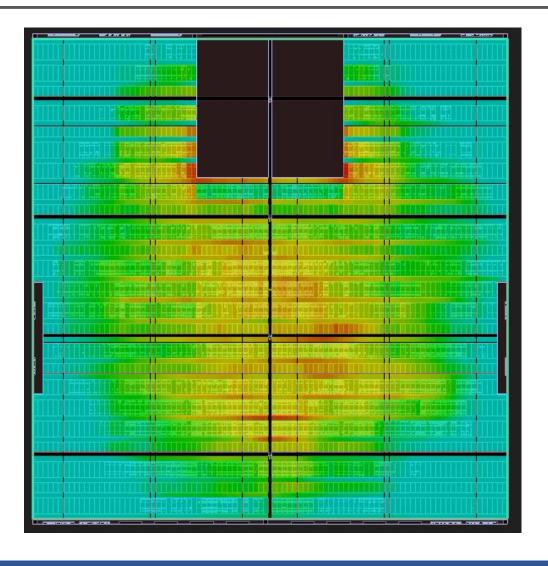

# Advanced: Congestion Map

• Impulse helps you creating regions

### Advanced: Python Console

Ipython is also here for help

```

□ □ X

\square A^{+} A^{-}

p = getProject()

p.modifyRegion(

Docstring:

Modifies an existing region identified by its name.

Signatures:

modifyRegion(name, column, row, width, height)

modifyRegion(name, column, row, width, height, exclusive)

Arguments:

(string): the region name

name

(unsigned): the region left abscissa

column

Python Console Message

(unsigned): the region top ordinate

row

width

(unsigned): the region width

(unsigned): the region height

height

exclusive (boolean): set if the region is exclusive

Return value:

None

builtin function or method

Type:

```

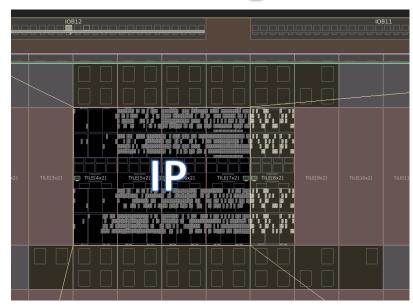

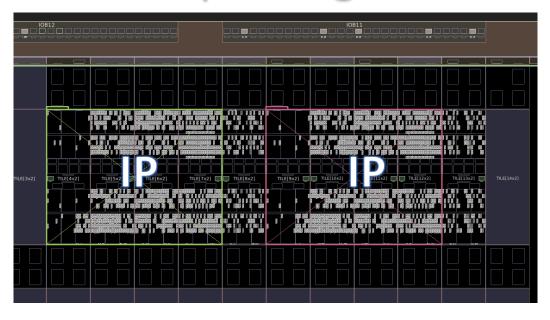

### Advanced: Prerouted IP

Bottom Up Design Closure

#### IP Design

#### Top Design

### Advanced: Open Mind

Always seeking for external collaboration

- Use DesignXplore\* to explore netlist

- Script everything with Python

- Objective:

- Invite all European universities and research institutes to be part of the European FPGA Adventure

- ... stay tuned

## ... And many more features

Please contact our support team\*

\*: Probably the best Support Team in the world

### Roadmap Impulse

List is not exhaustive

#### 23.5 (Dec 23)

- Improved Synthesis

- Prerouted IP Flow

- Improved PY console

- STA Reports in JSON

#### 24.1 (Jun 24)

- Clustering

- DesignXplore

- Schematic view

- Improved Log management

#### 24.3 (Dec 24)

- Multiple Run Management

- SystemVerilog Support

- DSP Core Generator

#### 25.1 (Jun 25)

- EQV Check Support

- New IO Editor

- NX Board GUI

- New STA Engine

### Roadmap IPs

• List is not exhaustive

#### 23.5 (Dec 23)

- SpaceWire RMAP

- 12C

- DDR2 Controller (ng-med)

#### 24.1 (Jun 24)

- Aurora

- JESD204B

- ESIstream

- GPIO

- DDR3 Controller

- AXI Bridges

#### 24.3 (Dec 24)

- Ethernet 1Gbit

- ...

- Waiting for requests

#### 25.1 (Jun 25)

- ...

- ➤ Waiting for requests

# Summary

### Summary

- ✓ Built a solid organization around software

- ✓ Impulse UI is a success and still improving

- ✓ Still got the ambition!

- Very confident about reaching higher performances

Objective:

Mont Blanc

# Thank You