# **STAR-Dundee**

20 Years of Spacecraft Networking Innovation

# SpaceFibre IP Core for BRAVE FPGAs

Marti Farras Casas, Albert Ferrer Florit

www.star-dundee.com @S

@STAR\_Dundee

### Contents

- SpaceFibre technology

- BRAVE Transceivers Verification

- Simulation Model

- Synthesis Results

- SpFi Post Synthesis Simulation

- Resource Utilisation

- Hardware Validation

# SpaceFibre for payload data-handling

- Spacecraft onboard data-handling network technology

- Connects together instruments, data compressor, data processors, data storage, downlink transmitter and control computer on-board a spacecraft

- Very high performance

- 6.25 Gbit/s per lane and higher depending on SerDes

- Multi-lane capability

- Increases link bandwidth Quad lane link at 6.25 Gbit/s per lane gives 25 Gbit/s

- Arbitrary number of lanes with graceful degradation when a lane fails.

- In-built Quality of Service

- Bandwidth reservation, priority and scheduling

- Fault detection, isolation and recovery capabilities

- At the link level enabling rapid error recovery (a few microseconds)

- Provides data integrity and reliable data delivery

# SpaceFibre for payload data-handling

- Low-latency broadcast messages

- For time distribution, synchronisation, event signaling, error notification, etc.

- Runs over electrical or optical cables

- Few m electrical, 100 m fibre optic

- Small implementation footprint

- Taking a few percent of a recent radiation tolerant FPGA

- Added as both data & control planes in SpaceVPX Vita 78 recently released

# SpaceFibre IP Cores General Features

- Configurable

- Number of lanes, virtual channels, ports

- High performance

- Optimised for radiation hardened FPGAs

- Easy to use

- AXI4-Stream interface for each Virtual Channel

- Reference designs for RTG4, PolarFire, KUS, Versal, BRAVE...

#### Safe

- Extensive verification and validation

- Tested in radiation environment

- TRL 9: Flying in operational missions

# SpaceFibre IP Cores General Features

- Use of EDAC protection in memories

- Guaranteed, straightforward, timing closure

- Lane rate only limited by Serdes (e.g. up to 3.125 Gbps on RTG4)

- For the whole temperature and voltage range (i.e. fast & slow corners)

- With EDAC and SET filters

- Does not require specific placement or timing constraints.

- Even with more than 80% FPGA utilisation

- Low latency

- Less than 400 ns for Broadcasts (including 250ns due to SerDes latency)

- Streaming frame sending option

- Compact design

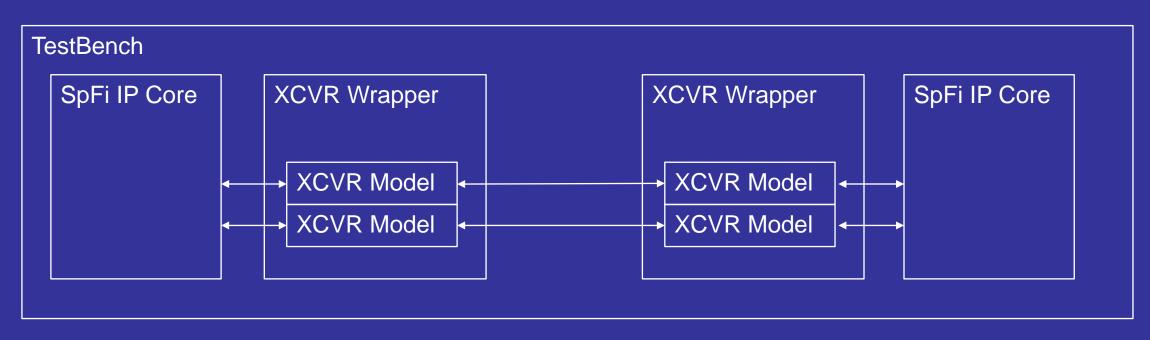

- STAR-Dundee carried out verification of SerDes

- Using simulation model

- Prior to manufacture (NG-Large)

- Verified main functionality of PCS and PMA Verilog models

- For both NG-Ultra and NG-Large simulation models

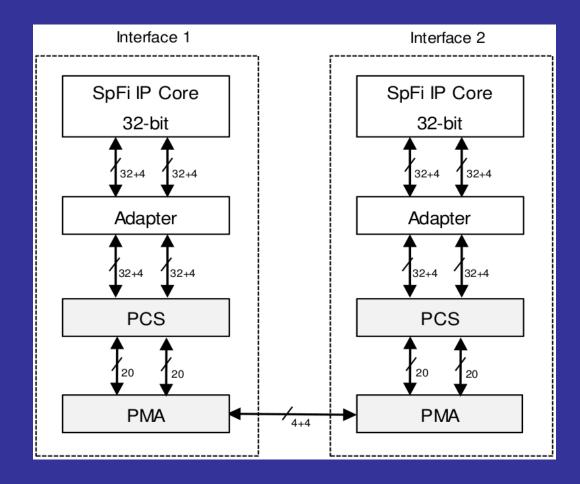

- BRAVE transceivers connected to SpFi Multi-Lane:

- 8B10B Encoding

- Comma detection with K28.7 and K28.5

- Rate adjustment using SKIP control words

- Transmit electrical idle capability (PMA)

- Loss Of Signal detection capability (PMA)

- Interface PCS with STAR-Dundee SpFi IP Core

- Control signals

- Word realignment

- Behavioural simulation

- SpFi optimisations for BRAVE FPGAs

- SpFi ⇔ XCVR logic

- XCVR behaviour

| 👍 LINK_READY                 | -No Data- |                                      |                  |       |                                         |                   |

|------------------------------|-----------|--------------------------------------|------------------|-------|-----------------------------------------|-------------------|

| ■                            | -No Data- | 0                                    |                  |       | <u>8</u> 0                              |                   |

|                              | -No Data- |                                      |                  |       |                                         |                   |

|                              | -No Data- |                                      |                  |       |                                         |                   |

|                              | -No Data- |                                      |                  |       |                                         |                   |

|                              | -No Data- |                                      |                  |       |                                         |                   |

| — Lane 0 ————                | _         |                                      |                  |       |                                         |                   |

| ↓ tx0_rst_n_i                | -No Data- |                                      |                  |       |                                         |                   |

| 🛯 🍫 tx0_ctrl_char_is_k_i     | -No Data- | 00                                   | 01               |       |                                         |                   |

| ∎🤣 tx0_data_i                | -No Data- | 000000000000000                      | 00000004646CEBC  |       |                                         |                   |

| 🛨 🔩 rx0_ctrl_char_is_comma_o | -No Data- | 00                                   | 04               |       |                                         |                   |

| ₽-4 rx0_ctrl_char_is_k_o     | -No Data- | 00 00                                | 04               |       |                                         |                   |

| 🛨 🔩 rx0_data_o               | -No Data- | 000000000000 00000000000000000000000 | 0000000CEBC4646  |       | (                                       |                   |

| — Lane 1 ———                 | _         |                                      |                  |       |                                         |                   |

| ↓ tx1_rst_n_i                | -No Data- |                                      |                  |       |                                         |                   |

| ∎� tx1_ctrl_char_is_k_i      | -No Data- | 00                                   | 01               |       |                                         |                   |

| ∎� tx1_data_i                | -No Data- | 000000000000000                      | 00000004646CEBC  | ***** | (                                       |                   |

| ••                           | -No Data- | 00                                   | 04               |       |                                         |                   |

| • x1_ctrl_char_is_k_o        | -No Data- | 00 100                               | 04               |       |                                         |                   |

| ∎                            | -No Data- | 000000000000 ( 000000000000000000000 | 0000000CEBC4646  |       | ······································  |                   |

| — Lane 3 —                   | _         |                                      |                  |       |                                         |                   |

| ↓ tx3_rst_n_i                | -No Data- |                                      |                  |       |                                         |                   |

| ±∲ tx3_ctrl_char_is_k_i      | -No Data- | 00                                   | (01              |       | 00                                      | 101               |

| ∎                            | -No Data- | 000000000000000                      | (00000004646CEBC |       | 000000000000000000000000000000000000000 | 1000000004646CEBC |

| • •                          | -No Data- | 00                                   | 04               |       |                                         | 01                |

| • • • rx3_ctrl_char_is_k_o   | -No Data- |                                      | 04               |       |                                         | 01                |

| trx3 data o                  | -No Data- |                                      | 0000000CEBC4646  |       |                                         | 00000004646CEBC   |

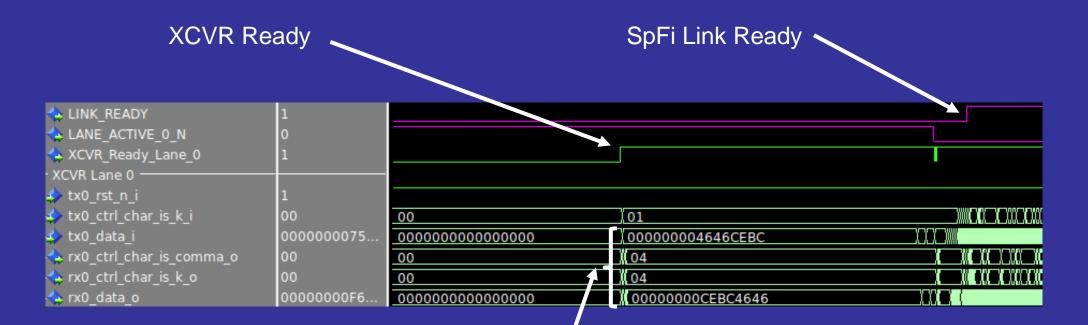

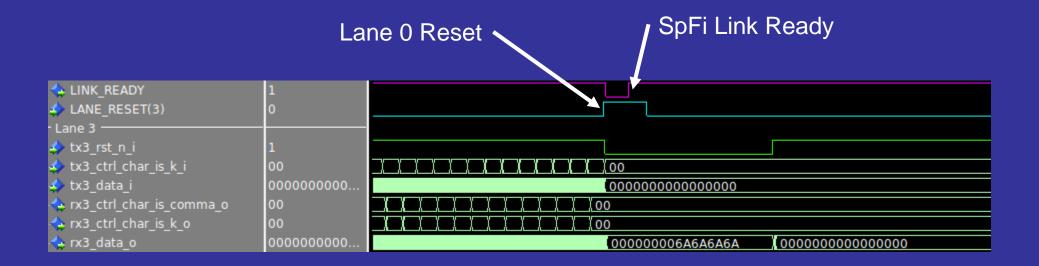

#### SpFi Link Initialisation

Exchange SpFi INIT Words

- Graceful degradation

- Automatically spreading the traffic over the remaining working lanes

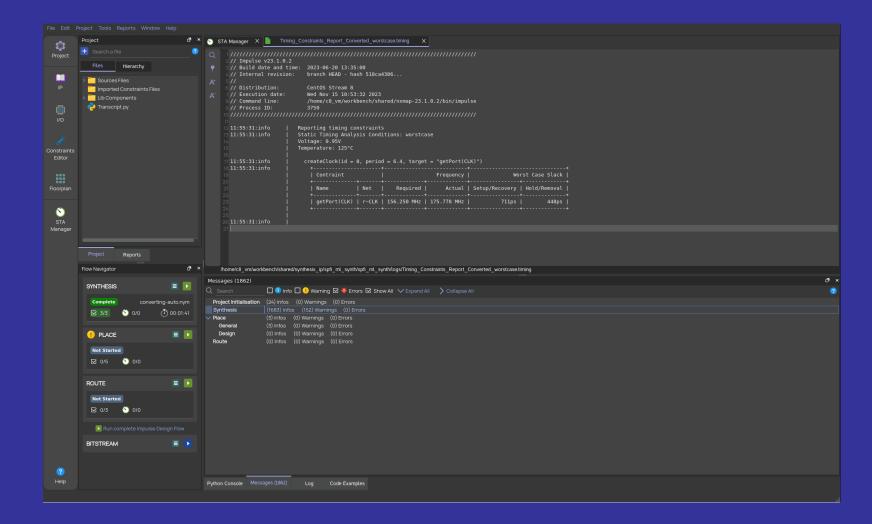

# Synthesis

#### SpaceFibre Multi-Lane IP Core synthesis

- Initial resource usage

- Initial timing values

- Memory inference

# Synthesis Results

- Post-synthesis simulation

- SpFi IP Core in loopback

- Verify memory inference

| a sim - Default ;                                                 | 📥 👍 link_ready         | -No Data-              |                |

|-------------------------------------------------------------------|------------------------|------------------------|----------------|

| ▼ Instance Design uni                                             |                        | -No Data-              |                |

| i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_cy(nx_s    | si 💠 L0_st_clear_line  | -No Data-              |                |

| 🧧 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_rfb_u(n  | L0_st_disabled         | -No Data-              |                |

| 🧧 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 [nx_ram(sin | LU_St_Walt             | -No Data-              |                |

| 🧧 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1nx_ram(sin   | LU_SL_Started          | -No Data-              |                |

| 🔄 i spfi ml brave i spfi ml 1 spfi intf 1 spfi link 1 nx ram(sin  |                        | -No Data-<br>-No Data- | L              |

| 🔄 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  |                        | -No Data-              |                |

| 🔄 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1nx_ram(sin   | Eo_sc_connected        | -No Data-              |                |

| 📕 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  |                        | -No Data-              |                |

| 📕 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  |                        | -No Data-              |                |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  |                        |                        |                |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n                      |                        |                |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n 🍫 VC0_AXI_TX_TVALID  | 1                      |                |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n 🗉 🤣 VC0_AXI_TX_TDATA | 64'hFFFFFFF            | FFFFFFFFFFFFFF |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n 🔶 VCO_AXI_RX_TVALID  | 1                      |                |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n 🗜 🛧 VCO_AXI_RX_TDATA | 64'hFFFFFFF            | FFFFFFFFFFFFFF |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n                      |                        |                |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n                      |                        |                |

| 🚽 i_spfi_ml_brave_i_spfi_ml_1_spfi_intf_1_spfi_link_1 nx_ram(sin  | n                      |                        |                |

| i_SERDES_RX_WORD_1_14_iob nx_iob_i(nx                             | x                      |                        |                |

| i_VC0_AXI_TX_TDATA_30_iob nx_iob_i(nx                             | x                      |                        |                |

# Synthesis Results

- Post-synthesis resource usage

- Resource usage for different configurations

- ~ 2% of resource utilisation

# Synthesis Results

- Post-synthesis timing estimation

- Constrained for 6.25 Gbit/s link speed

- Similar timing results for different configurations

- Max clock speed of about 175 MHz (> 6.25 Gbit/s)

| 11:55:31:info<br>11:55:31:info | Reporting timing c<br>  Static Timing Anal<br>  Voltage: 0.95V<br>  Temperature: 125°C<br> |       |             |             |                |                |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------|-------|-------------|-------------|----------------|----------------|--|--|

| 11:55:31:info<br>11:55:31:info | <pre>createClock(id = 0, period = 6.4, target = "getPort(CLK)")</pre>                      |       |             |             |                |                |  |  |

| 11:55:51: (110                 | Contraint                                                                                  |       | Ì           | Frequency   |                | rst Case Slack |  |  |

|                                | Name                                                                                       | Net   | Required    | Actual      | Setup/Recovery | Hold/Removal   |  |  |

|                                | getPort(CLK)                                                                               | r~CLK | 156.250 MHz | 175.778 MHz |                | 448ps          |  |  |

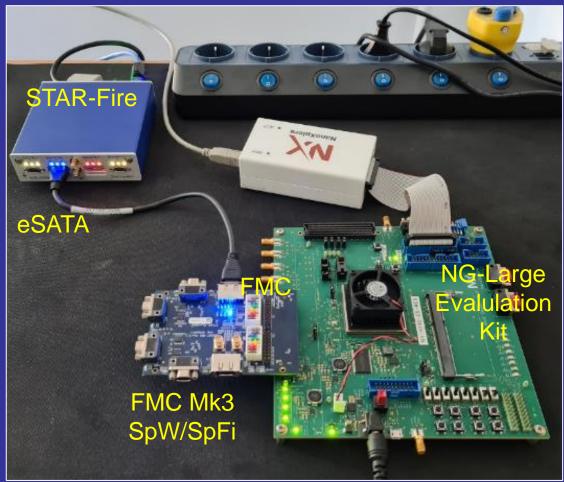

# Hardware Validation

- Successful link connection established with STAR-Fire unit

- 2 Gbps setup

- Correct data transmission without any data errors

- Retry events periodically appear

- Feedback from this experiment provided to NanoXplore

- The final validation of the IP to be completed soon

- Reference design with SerDes configuration, clock scheme details, memory instantiation (EDAC), etc. provided with IP

- NG-Ultra validation

- Reference design ready for validation as soon as hardware is available.

#### NanoXplore NG-Large Evaluation Kit

# STAR-Dundee's SpaceFibre IP Cores successfully verified and compatible with BRAVE transceivers

Provide support and reference designs for STAR-Dundee SpaceFibre IP Cores

Full validation on NG-Ultra as soon as hardware is ready