#### RISC-V in payload Control & Data Processing

NanoXplore BRAVE days November 29, 2023

**Technolution**

Dr. ir. Gerard Rauwerda Gerard.Rauwerda@technolution.nl

- Technolution **Gouda**

- Technolution Deventer **Deventer**

- Phase to Phase **Arnhem**

- Technolution Nordics

Gothenburg

- TNL USA & TNL Nanotech Wilmington, San Jose

**TNL**

#### **Advanced electronics and embedded systems**

- Ruggedized design / security by design

- Sensor and sensor interface design

- Data acquistion, handling, processing and storage, including Al

- Networking, wired and wireless data- and telecommunications

- Post-quantum encryption technology

- Information driven control and decision support (automated)

- Distributed embedded control systems

High-speed electronics design and testing

## RISC-V

# NX NanoXplore MICROCHIP AMDZ intel

#### Vendor-independent FPGA design

Technolution Advance

Technolution Prime

Technolution Perform

High-speed data acquisition & control

Classified line encryption

Condition monitoring for electric motors

## RISC-V® at Technolution (since 2014)

- We develop supplier-independent Programmable Logic designs

- Implemented in

- FreNox RISC-V IP

- RISC-V processor family, 100% developed by Technolution

- No dependencies on open-source implementations

- Implemented in NLD/NATO/EU classified security

#### **Embedded processor**

- hardware

- RV32I(M)

- 32bits, mul/div

- 5 stages Harvard arch

- cache or internal RAM

- IO space

- software

- Bare metal

- FreeRTOS

- ThreadX

#### **Application processor**

- hardware

- RV32IMA (S-mode)

- 32bits, mul/div, atomic, supervisor

- 5 stages Harvard arch

- iMMU, dMMU (1 128 entries)

- 8 way associative cache (4 32k)

- cache coherency (DMA)

- IO space

- software

- Linux

- Buildroot

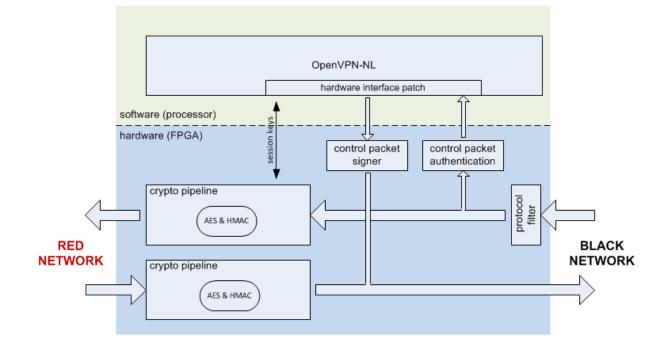

# **Secure line encryption**

- Hardware VPN solution (NLD/NATO/EU restricted)

- Control flow in software / N RISC-V°

- Data encryption in hardware logic

# **Secure line encryption**

- Hardware VPN solution (NLD/NATO/EU restricted)

- Control flow in software / N RISC-V°

- Data encryption in hardware logic

- ⇒ Full understanding of our custom implementation

- ⇒ Transparency for customer/evaluator

- ⇒ Lifecycle management (transparency & portability)

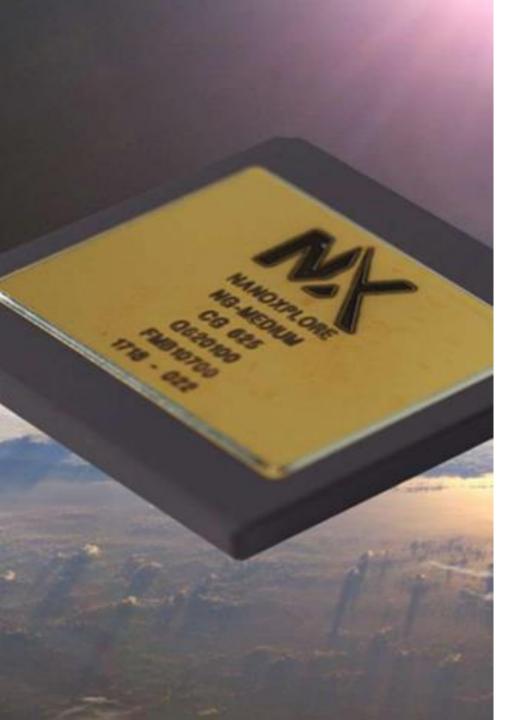

#### Radiation hardened FPGA

- Europe needs

non-dependent access to

critical space technologies

- European radiation-hard FPGA

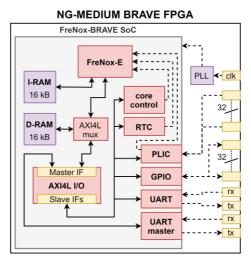

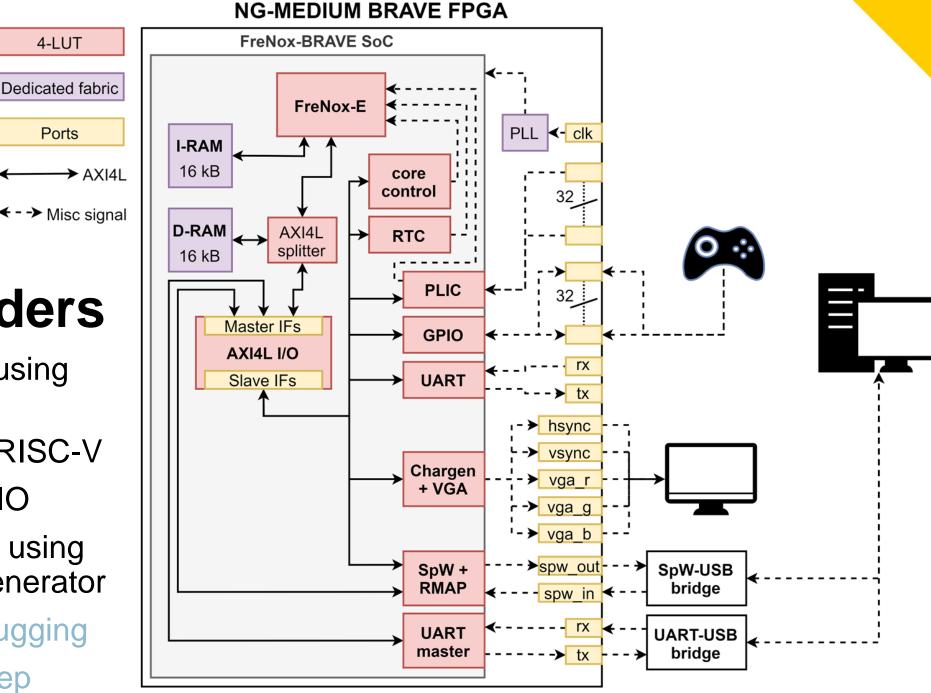

FreNox-E SoC implemented and demonstrated in NG-Medium RH-FPGA

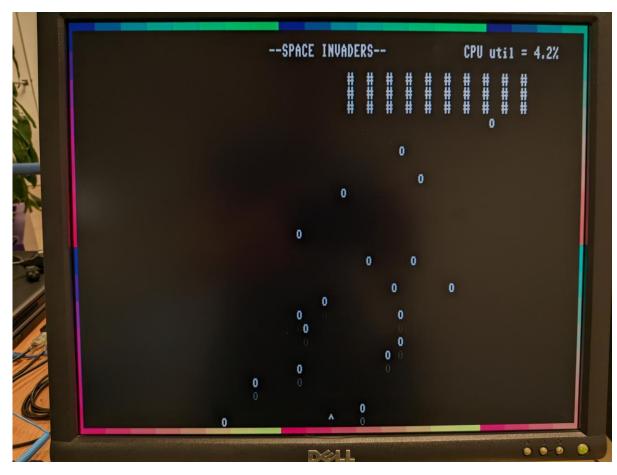

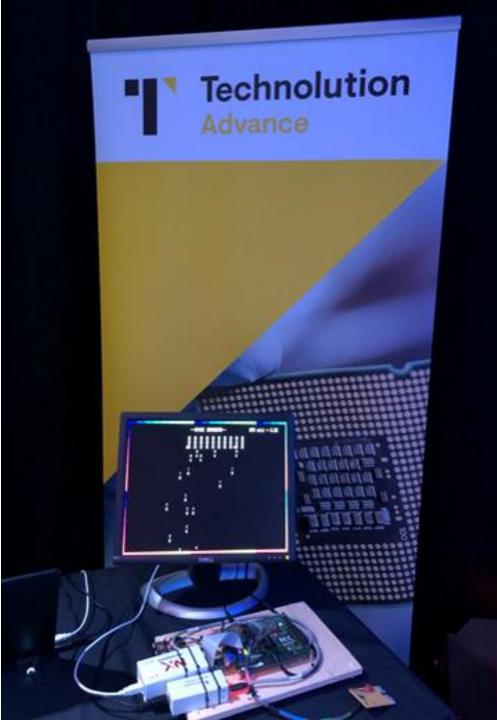

### Demo Space Invaders

- Upload software using SpW-RMAP

- Run software on RISC-V

- Control using GPIO

- Output to monitor using VGA character generator

- GDB remote debugging

- RISC-V in lock-step

### Demo Space Invaders

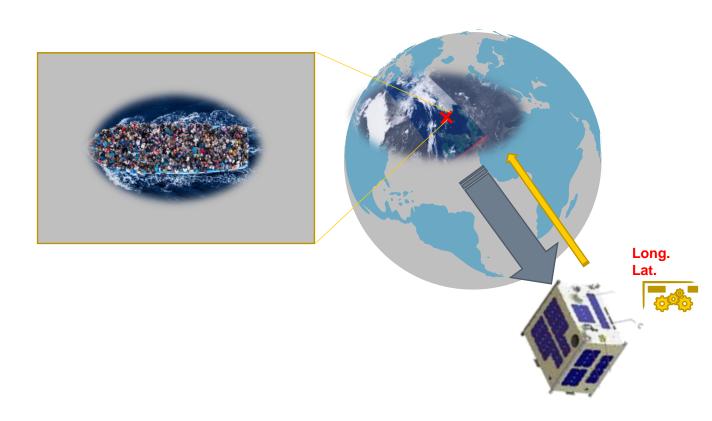

### **Earth Observation – Real-time information**

- Data reduction

- Edge processing close to sensor

- Compute and send only relevant data

- Can embed several instruments

- Low Latency

- Removing need for ground-based processing

- e.g. LEO latency is 25ms (500ms in GEO)

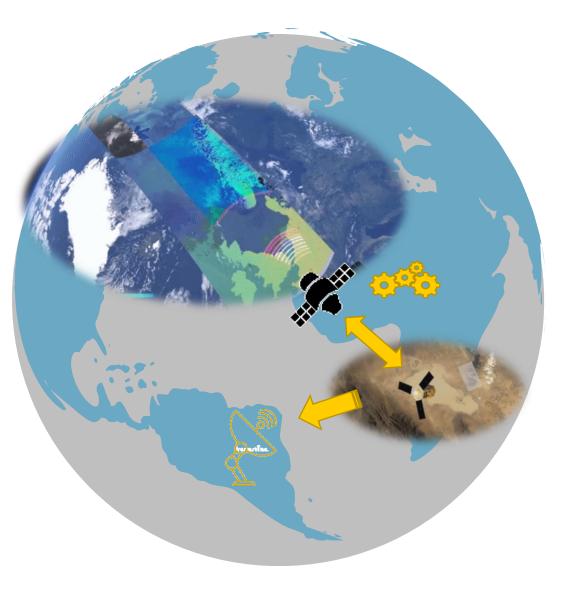

#### **Earth Observation – Constellation space**

- Constellation space -Distributed system of satellites

- Use first satellite to detect anomalies

- Ask second satellite to zoom-in

- Distributed edge processing to reduce latency and down-link data

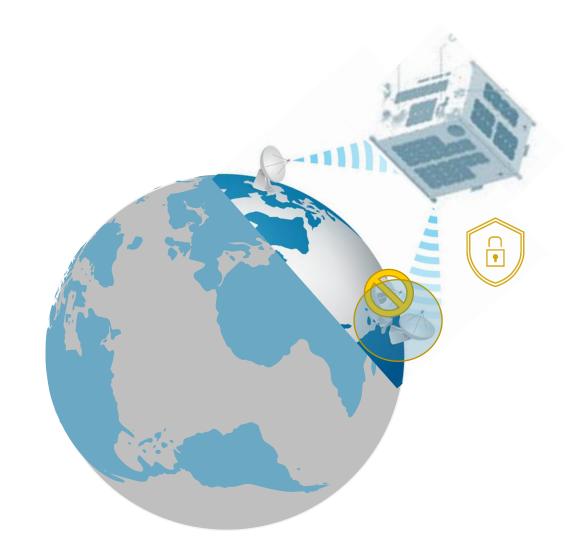

### **Earth Observation – Data protection**

- Satellite-as-a-Service & Constellation-as-a-Service

- Data are valuable

- Data are critical

- Encrypt instrument data

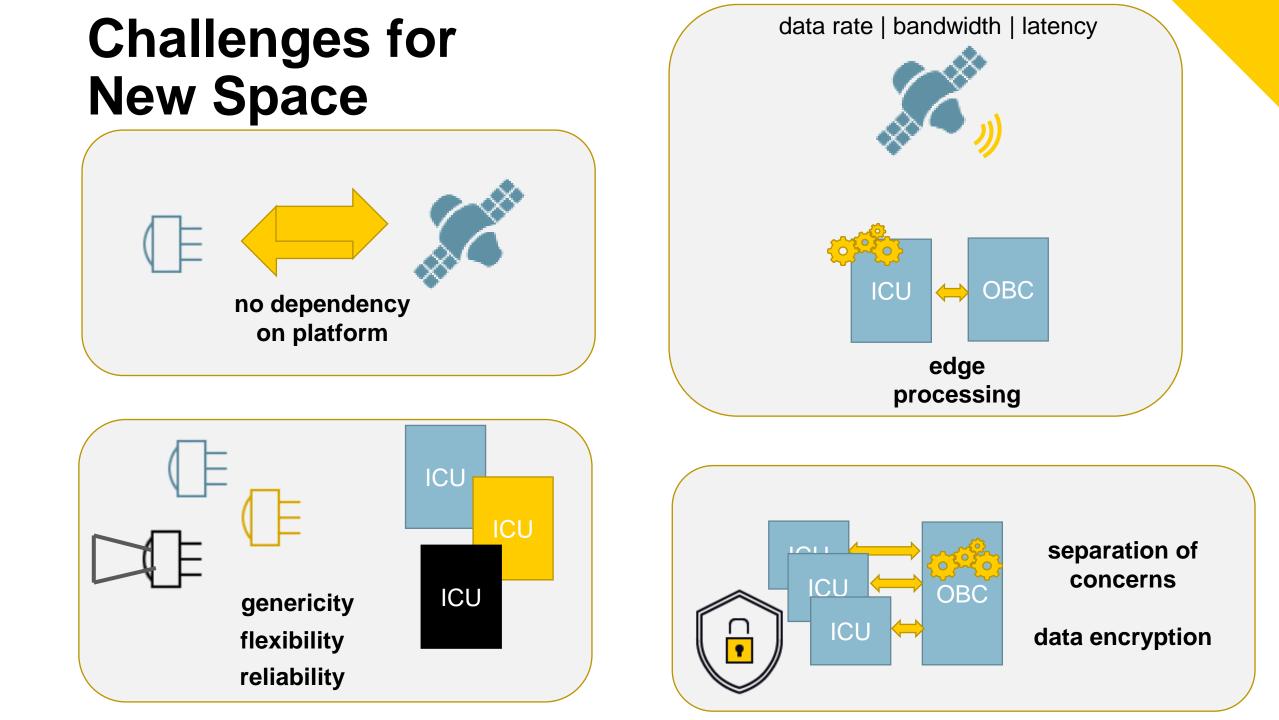

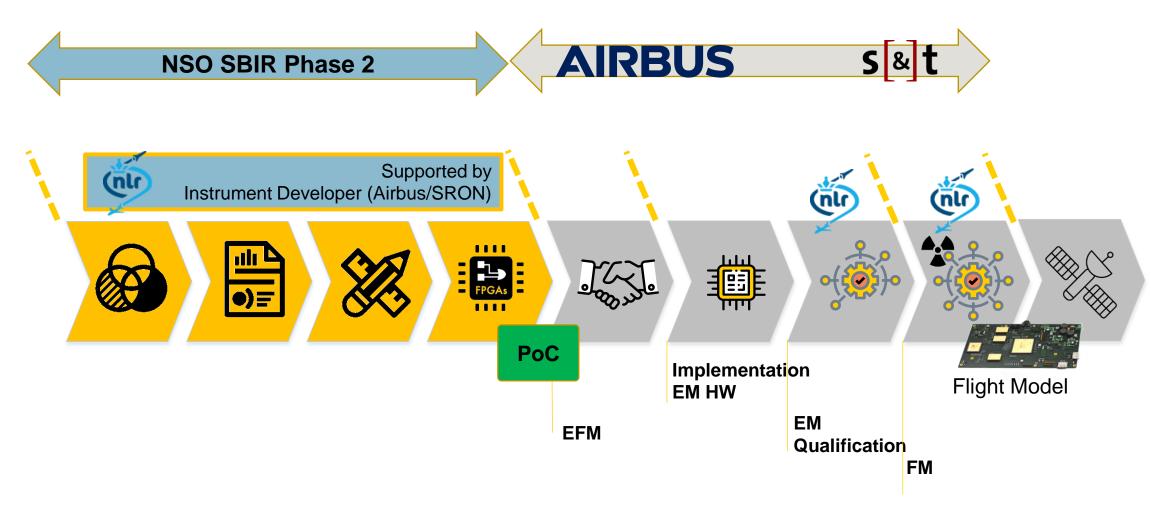

## **Small Business Innovation Research**

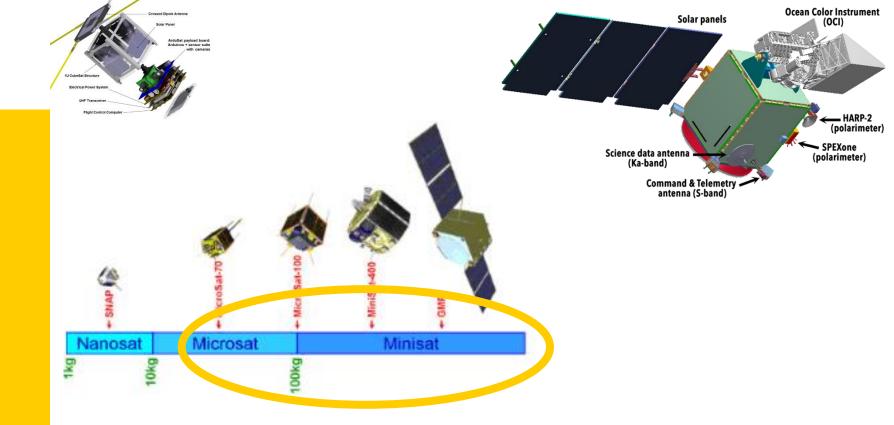

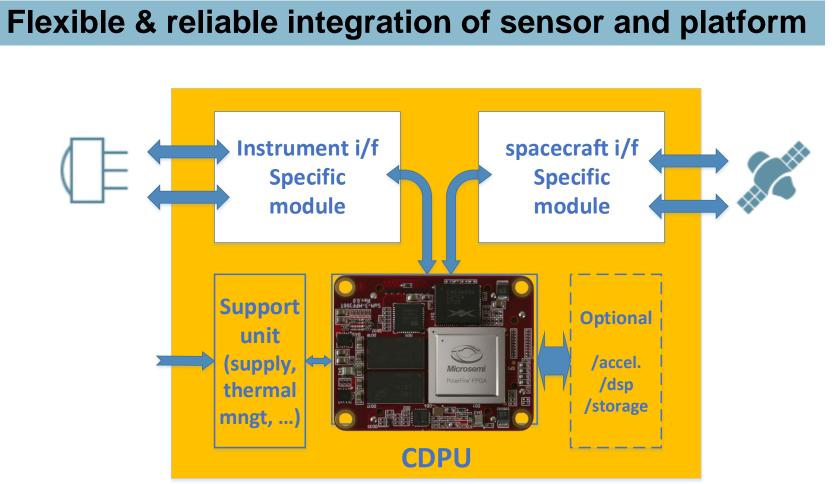

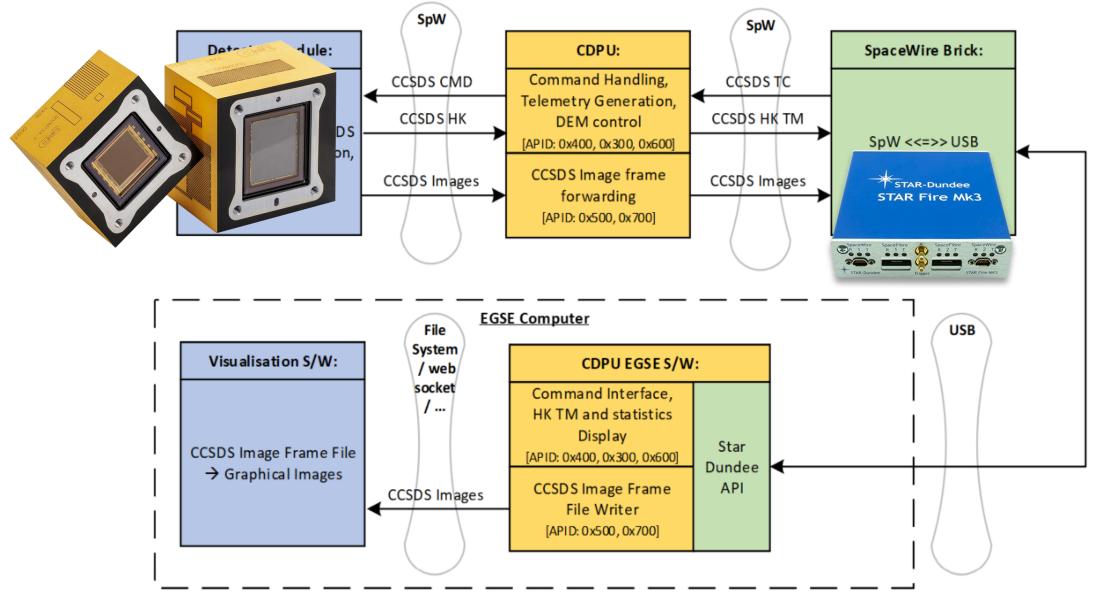

#### CDPU: Control & Data Processing

#### for SmallSat instruments

Space cesa

Technolution

- >5y in-orbit life-time

- high quality & reliability

- flexibility

- modular electronics

- in-orbit reconfigurability

- in-orbit edge computing (image processing, encryption, <u>instrument autonomy</u>, ....)

#### CDPU: Control & Data Processing

#### for SmallSat instruments

Space Cesa

**Technolution**

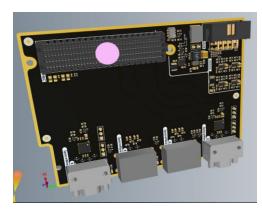

#### **CDPU Evaluation Kit**

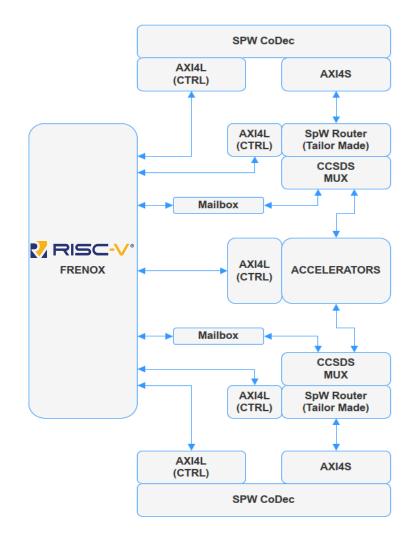

# **CDPU FPGA Functional Design**

- Programmable logic design

- FreNox RISC-V

- SpW interface IP

- SpFi interface IP

- Interconnect infrastructure; accelerator extensions

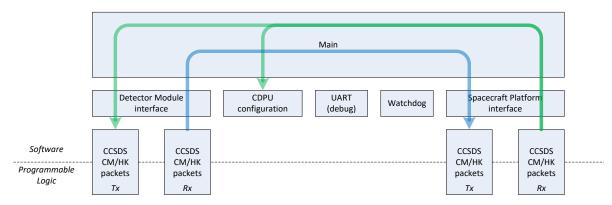

- Embedded software design

- TC/TM handling

### **CDPU Demo – Instrument Integration**

# What's next?

FreNox-E SoC demonstrated in NG-Medium RH-FPGA

FreNox-E SoC demonstrated in PolarFire FPGA for CDPU

# Thanks for your attention!

#### Dr. ir. Gerard Rauwerda

**Business Developer**

#### **Technolution Advance**

Burgemeester Jamessingel 1 2803 WV Gouda The Netherlands

Gerard.Rauwerda@technolution.nl

+31 182 59 4000

technolution-advance