## FPGAs for space: Rad Hard, Rad Tol and COTS considerations

David Merodio Codinachs TEC-EDM

BRAVE Days, ESTEC, 28/11/2023

ESA UNCLASSIFIED - For ESA Official Use Only

####

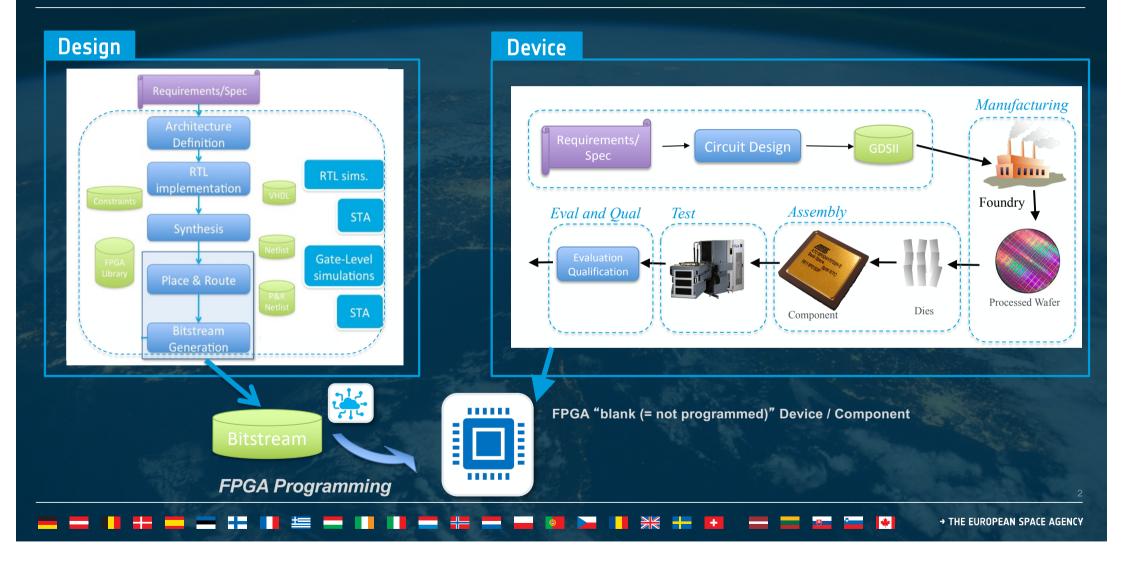

# FPGA – Device and Design definition in the presentation • esa

### **FPGAs** goal

### The programmed FPGAs are intended to:

- Perform the envisaged complex functions

- At the expected time and performance

- Without interruptions (or with an availability that has minimum and quantified interruptions identified)

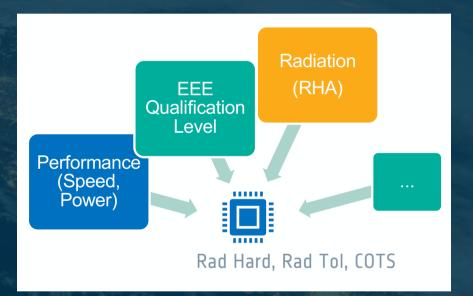

# FPGAs on-board: many choices, the selection is a complex problem

01

→ THE EUROPEAN SPACE AGENCY

- On-board processing requirements:

- Advanced Functionality <sup>(\*)</sup>

- Performance (speed, power)

- Space environment (mission-dependent)

- High-performance FPGA Devices :

- are key to implement those on-board requirements

- Selection trade-off:

# Trade-off depends on many requirements and factors (related to Mission Class)

\*

(\*) Example of complex functions:

EDHPC Tutorial: Satellite Radio Frequency payloads and Instruments – Overview and challenges for data and signal processing - https://indico.esa.int/event/445/sessions/1599/

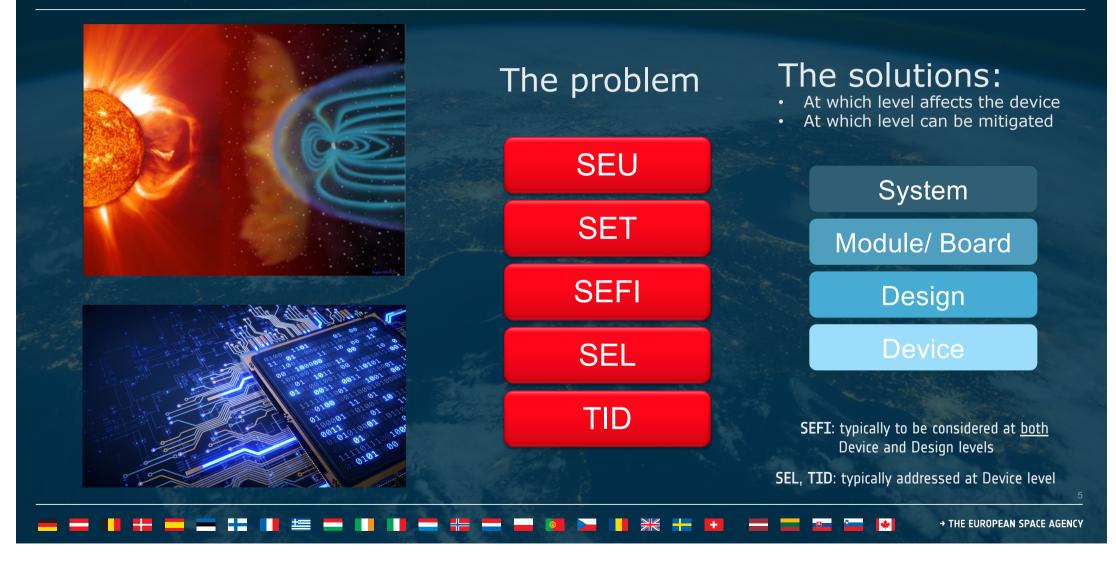

### **FPGA for Space - radiation**

# Radiation mitigation strategy – Device and design levels .

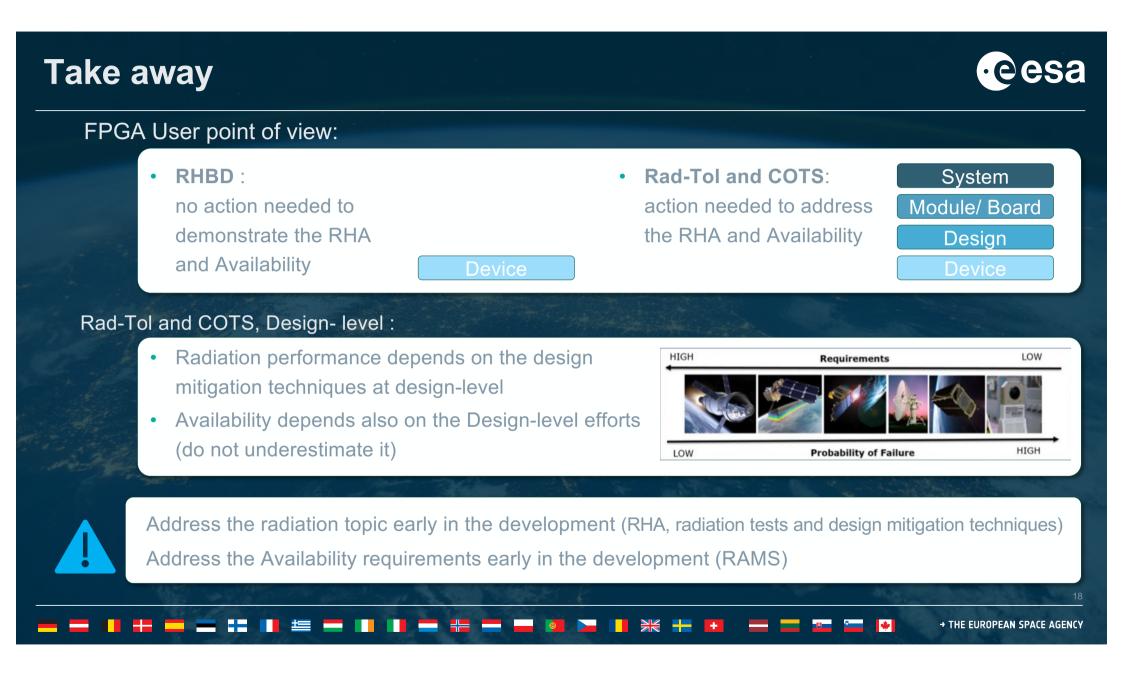

# Rad-Hard by Design (RHBD)

ESA UNCLASSIFIED – For ESA Official Use Only

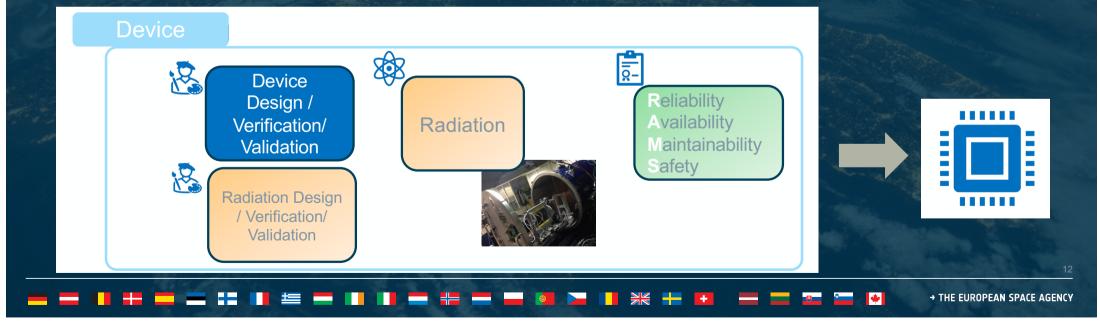

### **RHBD FPGA Device – Vendor role**

### Rad-Hard By Design (RHBD) Device

- The FPGA Device vendor:

- designs/ verifies and validates the device (i.e. component), including both the functionality and design mitigations against radiation<sup>(\*)</sup>

- Performs radiation tests to validate the radiation requirements (RHA)

- Provides Reliability and Availability data

- Radiation events have no impact on availability (RAMS) at Device level, as the event rates are extremely low

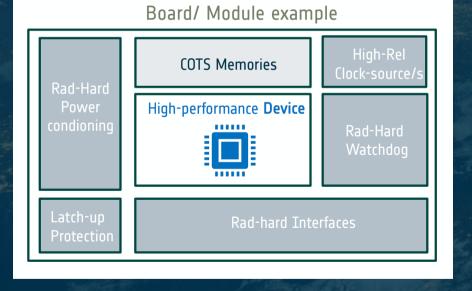

Andule/ Board

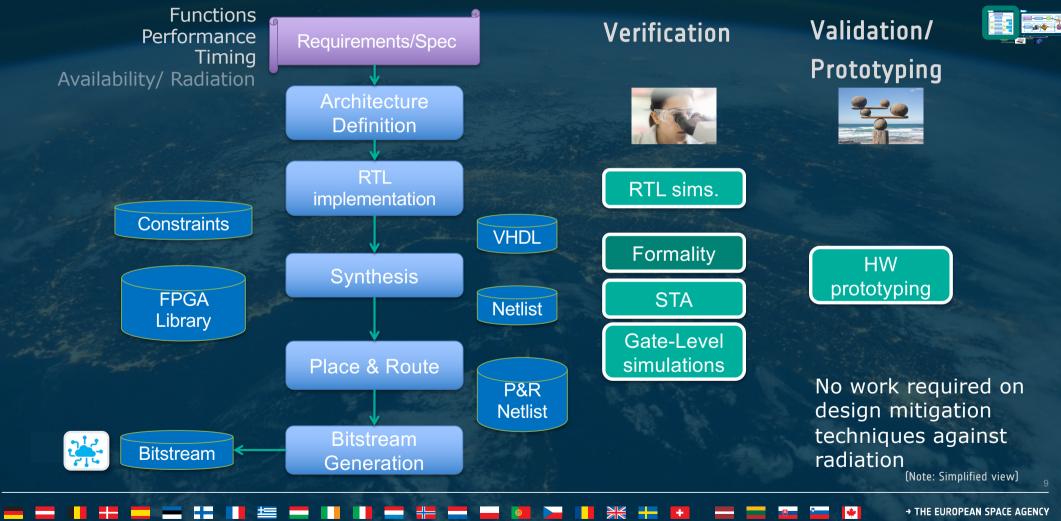

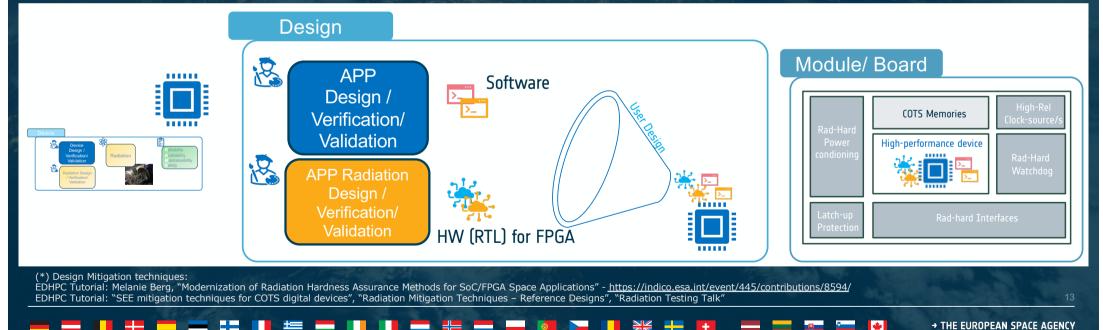

## RHBD FPGA device: FPGA design team tasks overview

·eesa

### **RHBD – FPGA user/ customer role**

### Rad-Hard By Design (RHBD) Device

- The FPGA Device user/ customer:

- designs/ verifies and validates the **design functionality** on the device and on the module/ board

- No need to perform extra radiation tests to validate the radiation requirements (RHA)

- No need (or very minimal) to work on Reliability and Availability data, as it does not impact the higher-level

# Non Rad-Hard by Design (RHBD)

ESA UNCLASSIFIED – For ESA Official Use Only

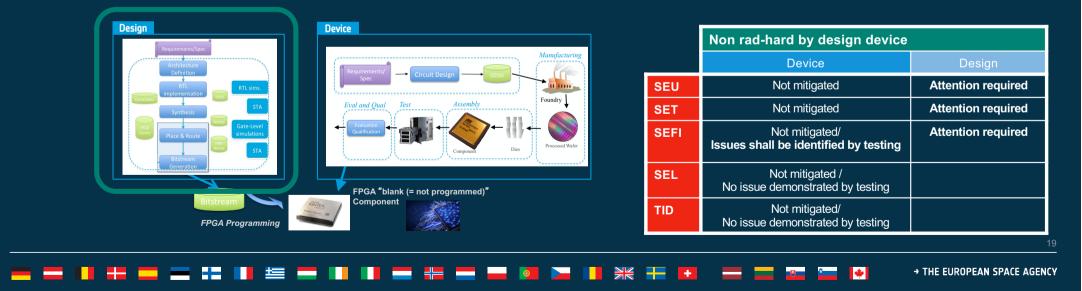

## Non RHBD – Vendor role

### Non Rad-Hard By Design (RHBD) Device

- The FPGA Device vendor:

- designs/ verifies and validates the device (i.e. component) functionality; without addressing (or limited) the design mitigations against radiation

- Performs radiation tests to validate the radiation requirements; but results might be dependent on the design

- Provides Reliability and Availability data; but it might be design-dependent

- Radiation events might have an impact on availability (RAMS) at Device level due to design-dependency

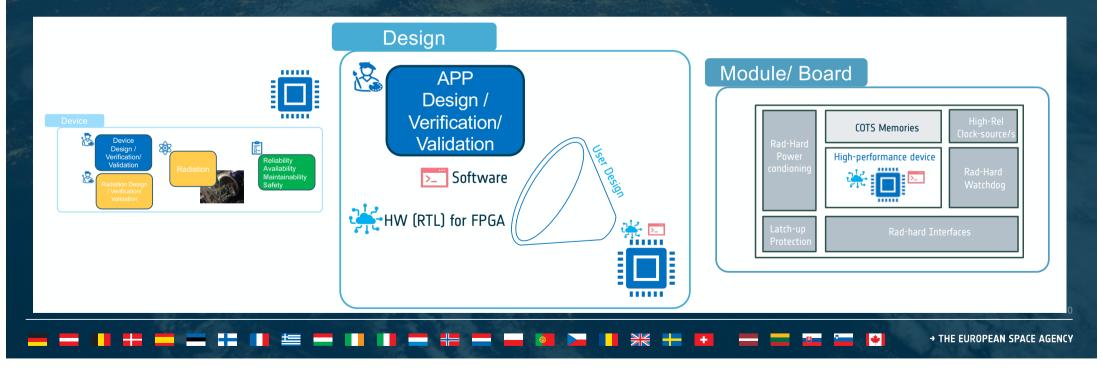

### Non RHBD – FPGA user/ customer role

# esa

Module/ Board

### Non Rad-Hard By Design (RHBD) Device

- The Device user/ customer:

- designs/ verifies and validates the design functionality and the design mitigation techniques<sup>(\*)</sup> on the device and on the module/ board

- Performs radiation tests to validate the design-dependent potential impact radiation performance (and other methods)

- Design-dependent mitigation techniques to be analysed on the Reliability and Availability data

Radiation Design mitigation techniques strategy, some questions to be addressed :

- How much design-dependent mitigation is needed?

- How many radiation events will produce an error? (i.e. calculation of error rate)

- Which errors influence which functions and what are the recovery times for each of them?

- Do the functions error rate comply with the mission availability requirements? (RAMS)  $FIT = \lambda_{FIT}$

💳 💶 📲 💳 🚍 📕 🏣 🔜 📕 💶 📲 🚍 😓 ன 🔤 🔤 🖬 🚺 💳 🛨

# Non RHDB FPGAs - FPGA design mitigation verification

**Challenge**: Define the *FPGA designer* radiation mitigation strategy depending on the mission requirements

#### **Radiation events:**

Not every radiation SEE event is an error

#### Challenge:

- Assuming every event is an error leads to a (very) pessimistic assumption

- How to know which events will produce an error? It is a complex problem

More information, for example: EDHPC Tutorial: Melanie Berg, "Modernization of Radiation Hardness Assurance Methods

for SoC/FPGA Space Applications" - <u>https://indico.esa.int/event/445/contributions/8594/</u>

#### **Challenge:**

Design-level radiation-induced Errors have impact on the availability

More information, for example: EDHPC Tutorial: Richard Jansen, "Radiation Testing Talk" https://indico.esa.int/event/445/contributions/8603/attachments/5600/9131/EDHPC%20tutorial%20-%20Microelectronics%20Radiation%20Mitigation%20v4.pdf

Radiation Verification

### Radiation Validation/ Prototyping

Hardware-based

Radiation testing

of the application

Fault Injetion

Simulation-based Fault Injetion

### 👝 🚍 📕 🕂 🔤 🚍 🚼 📕 🏣 🔲 📕 🗰 👫 📥 🛶 🚳 🚬 🚺 💥 🖶 🔂 🔤 🔤 😵 🔸 THE EUROPEAN SPACE AGENCY

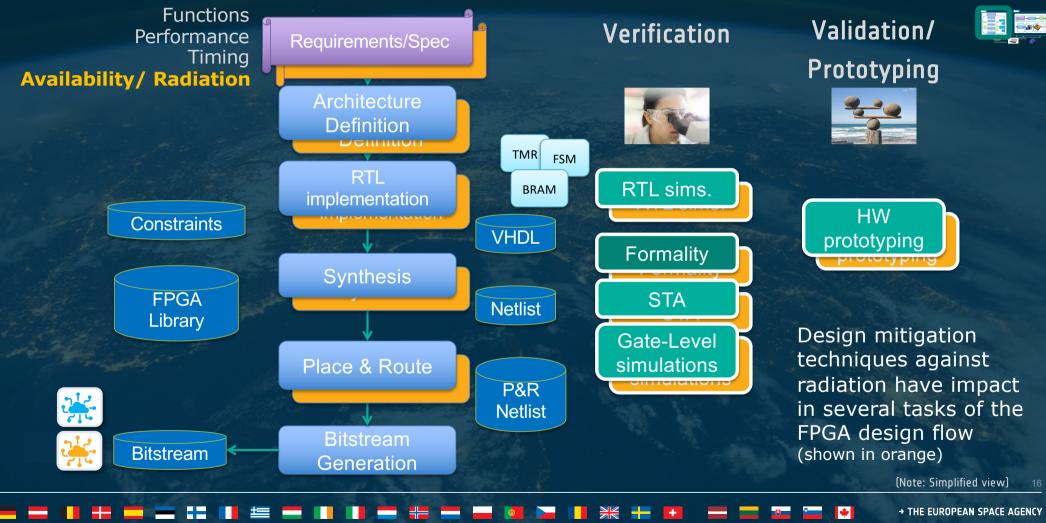

# Non RHBD FPGA device: FPGA design team tasks overview

·eesa

ESA UNCLASSIFIED – For ESA Official Use Only

### 👝 👝 📕 🕂 📩 🔤 🚛 🚼 🚺 🚝 🛶 🚺 🔚 🚃 ∺ 🔤 🔤 🚳 🚬 🚺 💥 🕂 🖬 💷 💳 😻 → The European space agency

### **FPGA** for space - radiation

#### The FPGA team has to account the effort for design mitigation techniques when not using RHDB FPGA:

- Consolidate assessment that there are no issues due to SEL and TID

- Check potential design mitigation at board-level for device SEFI/s

- Radiation mitigation strategy for SEU/SET/MBU:

- Define, implement, verify and validate the design mitigation techniques

- Consider the impact on the availability of the functions implemented