# FPGA Architect & Model Based Engineering

Adam@AdiuvoEngineering.com

# Devices are getting large

481,000 LUTs

899,840 LUTs

331,000 LUTs

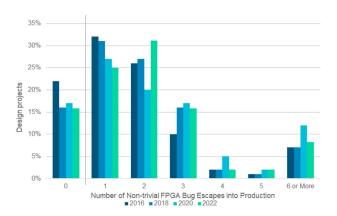

## We are not getting better at designing

#### FPGA projects are performing no better than ASIC

#### Root cause of FPGA functional flaws

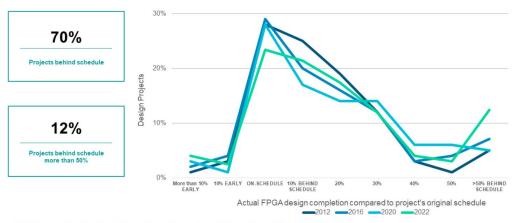

#### Most FPGA projects miss schedule

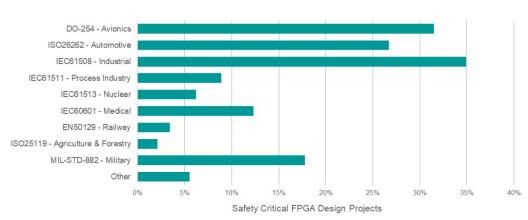

#### FPGA project adoption of various functional safety standards

We cannot keep designing as we have been.

"Insanity is doing the same thing over and over again and expecting different results."

#### Adiuvo Model Based Flow

Adiuvo has completed two projects recently for Space Industry using model-based techniques. What we have seen is on time development and fewer bugs.

#### **Applications**

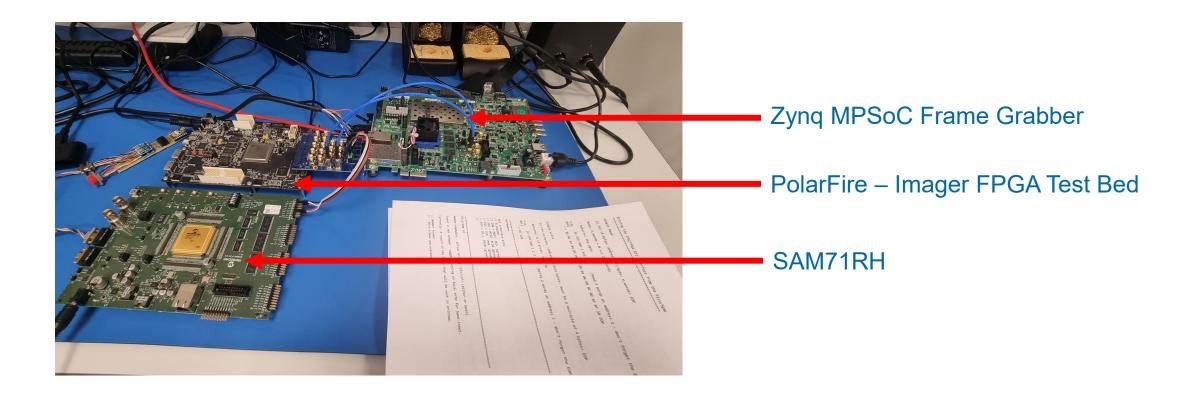

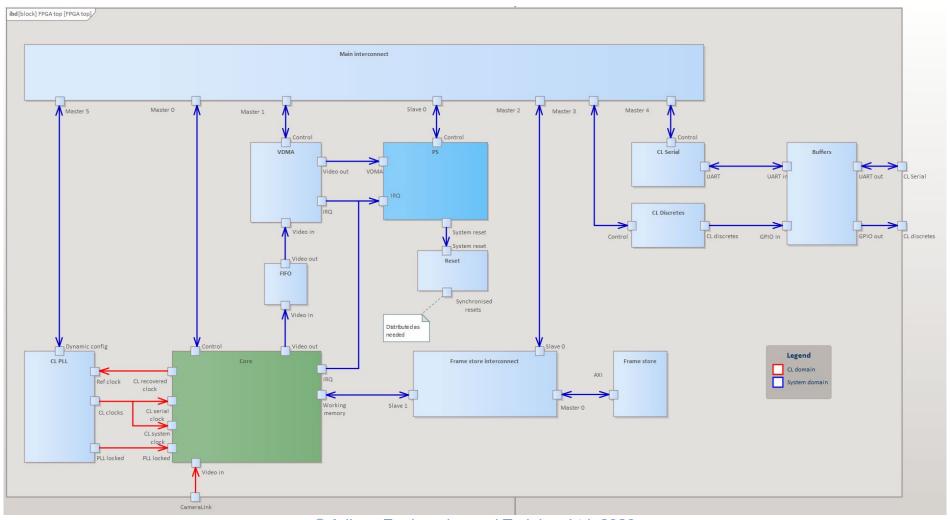

- 1. Space Imager based around PolarFire and SAM71RH– Complex image sensor interface, DDR4, Binning, Frame Subtraction, Output over Serdes Adiuvo developed FPGA and SW applications.

- 2. Terrestrial / Space Laser Communications based around Xilinx MPSoC Camera Interfacing, Image Processing, Spot detection, Histograms etc. Adiuvo Developed FPGA and SW.

Recently shared with a Adiuvo Client to help with their PolarFire Project

## Camera Development Project

#### Adiuvo Model Based Flow

#### Adiuvo Model Based Flow

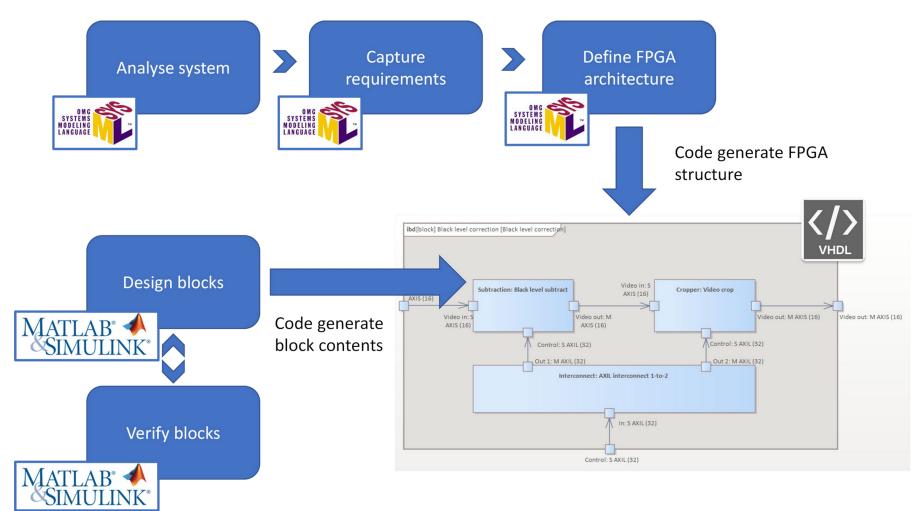

Basis of the model-based flow is an internally based architecting tool

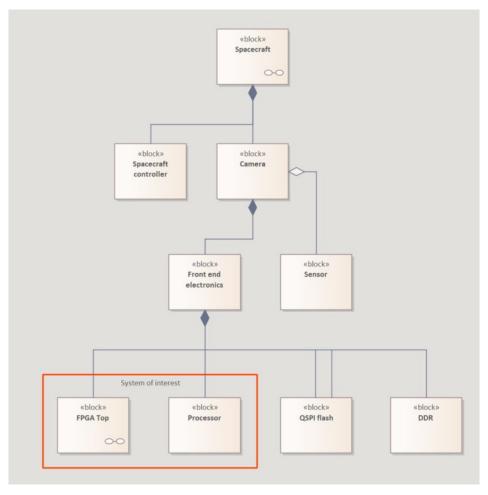

Our workflow typically starts with us developing a 'system level' model that allows us to explore issues at the system level and to help us understand the context in which the FPGA is operating.

We can use that model for design reviews e.g. SRR / PDR and get customer buy in to the solution

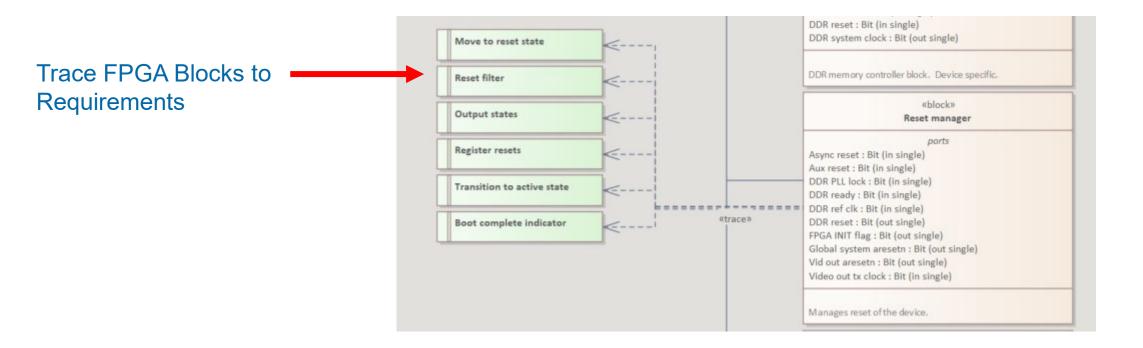

Robust design that traces directly back to our requirements and also to the higher-level system design

Adiuvo has invested heavily in the ability to code generate the SysML model

## **Context Diagram**

# **Enter Requirements**

| OAKI CEC BIOCK.                                                                                                                                                                                 |            |          |        |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--------|--------|

| ☑ External video clock                                                                                                                                                                          | Functional | Proposed | Medium | Medium |

| The FPGA when the [Video output timing] register is set to 'external clock', shall clock the [High speed serial video output] at the same rate as the [External serial reference clock.REFCLK]. |            |          |        |        |

| ☑ Internal video clock                                                                                                                                                                          | Functional | Proposed | Medium | Medium |

| The FPGA when the [Video output timing] register is set to 'internal clock', shall clock the [High speed serial video output] at 2.5 Gbps.                                                      |            |          |        |        |

| ☑ Boot complete indicator                                                                                                                                                                       | Functional | Proposed | Medium | Medium |

| The FPGA <b>shall</b> indicate when the boot process has completed by asserting the signal <b>[FPGA boot flag.FPGA_INIT]</b> once boot has completed.                                           |            |          |        |        |

| ☑ Move to reset state                                                                                                                                                                           | Functional | Proposed | Medium | Medium |

| The FPGA, when not in the boot state, <b>shall</b> transition to the reset state when the signal [ <b>System reset.FPGA_RESETN</b> ] is asserted for more than 10 primary system clock cycles.  |            |          |        |        |

| ☑ Output states                                                                                                                                                                                 | Functional | Proposed | Medium | Medium |

| The FPGA, when in the reset state, <b>shall</b> ensure that all outputs from the device are held in their inactive state.                                                                       |            |          |        |        |

| ☑ Register resets                                                                                                                                                                               | Functional | Proposed | Medium | Medium |

| The FPGA, when in the reset state, <b>shall</b> ensure that the following software programmable registers are in the following states:                                                          |            |          |        |        |

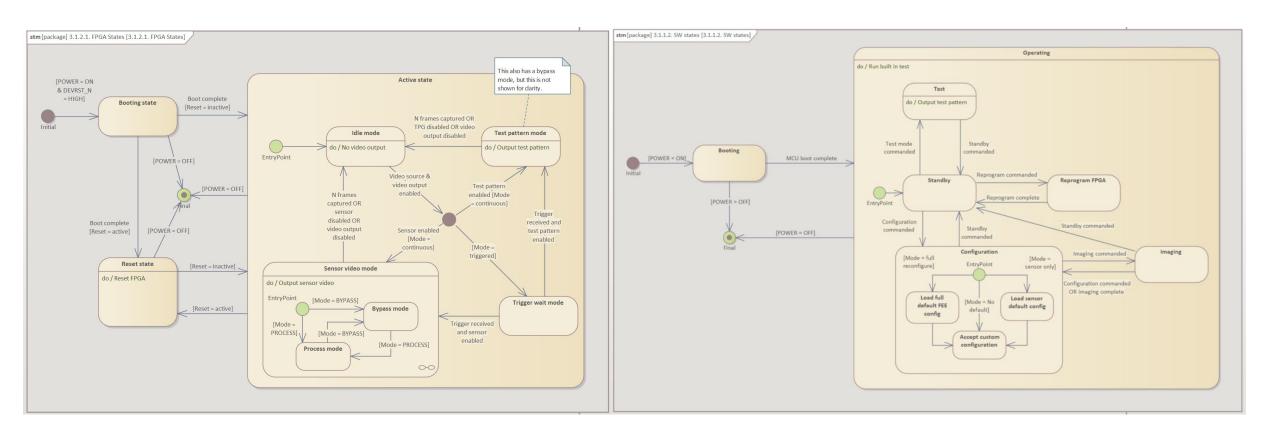

### System Model - Behavior - FPGA & SW

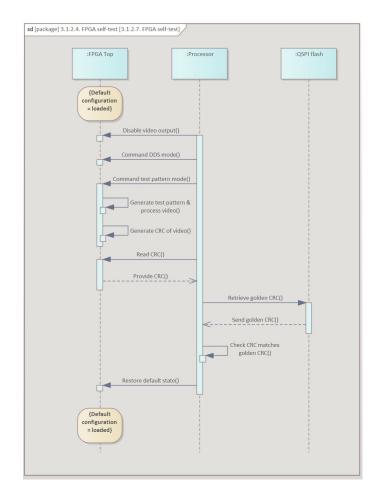

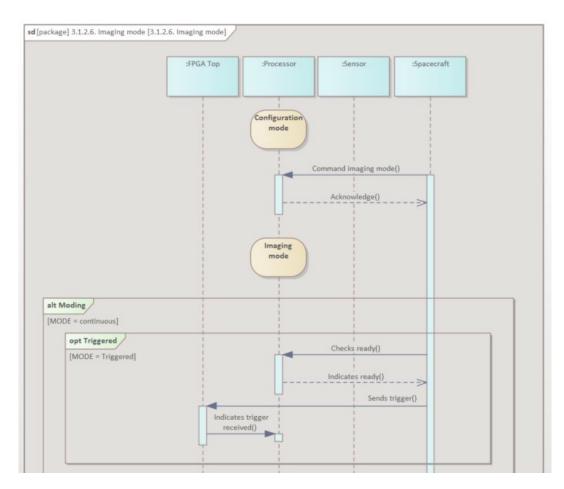

## System Model – Sequences

#### **FPGA Context**

#### **FPGA Context**

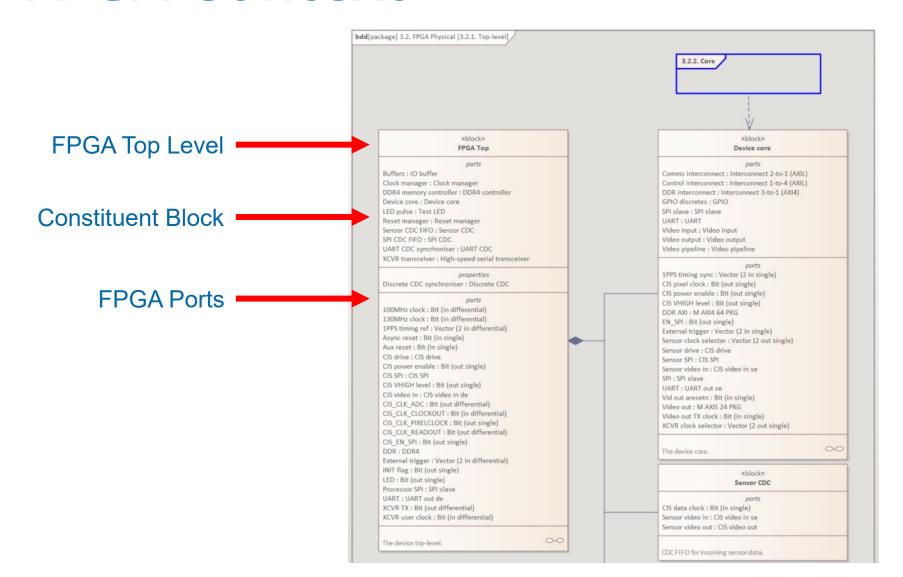

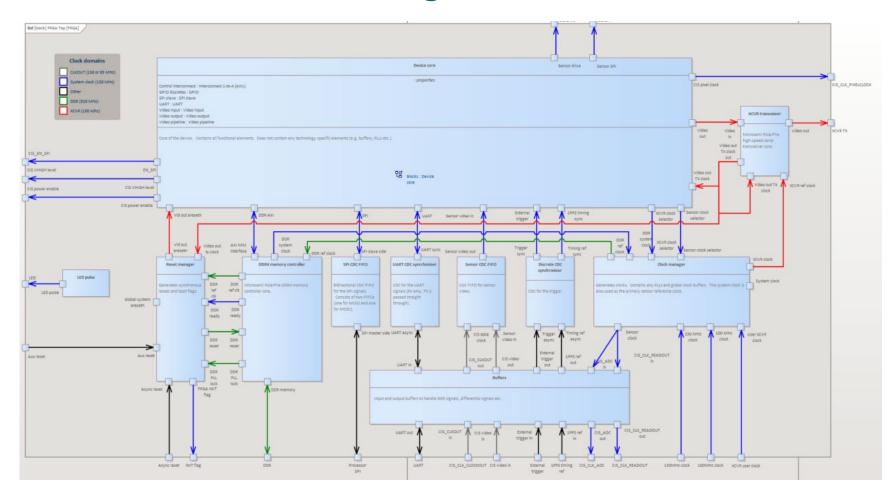

## FPGA Architecture - Project One

Interface aware

AXI4 AXILite Serdes Custom – Logic

Define in interface diagram

## FPGA Architecture - Project One

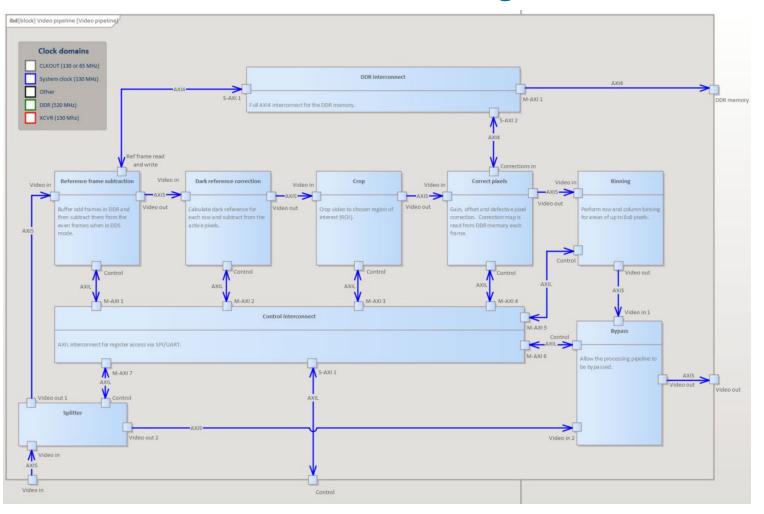

## FPGA Architecture - Project Two

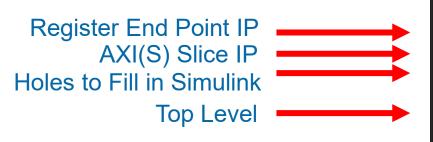

#### **Code Generation**

SysML code generation - XML from EA then Python

- Generates VHDL

- All interfaces are created as per definition

- Registers inserted where defined in model

- AXI Networks implemented using Adiuvo Interconnects (Technology Ind)

- Pulls in Adiuvo IP blocks

- Generates ModelSim Compile scripts

- Generate ICD C, Python, VHDL, SystemVerilog and CSV

### **Code Generation - HDL**

| Name          | Date modified    | Туре        | Size |

|---------------|------------------|-------------|------|

| endpoints     | 04/06/2023 15:50 | File folder |      |

| slices        | 04/06/2023 15:50 | File folder |      |

| stubs         | 04/06/2023 15:50 | File folder |      |

| pwm.vhd       | 03/02/2023 10:41 | VHD File    | 7 KB |

| robot_top.vhd | 03/02/2023 10:41 | VHD File    | 3 KB |

| aurt.vhd      | 03/02/2023 10:41 | VHD File    | 4 KB |

|               |                  |             |      |

### What does the Code Look Like?

```

architecture rtl of robot_top is

--Internal signals

signal s sys clk this : std ulogic;

signal s_sys_aresetn_this : std ulogic;

signal s pwm pwm : std ulogic vector(6 downto 0);

signal s axil 32 pkg mosi maxil uart : work.axil 32 pkg.r axil mosi;

signal s axil 32 pkg miso maxil uart : work.axil 32 pkg.r axil miso;

signal s rx uart this : std ulogic;

signal s_tx_uart_this : std_ulogic;

□ begin

--Internal signal assignments

o pwm0 <= s pwm pwm;

o tx uart <= s tx uart this;

s sys clk this <= i sys clk;

s_sys_aresetn_this <= i_sys_aresetn;

s rx uart this <= i rx uart;

--pwm instantiation

u pwm : entity work.pwm

port map (

i sys clk => s sys clk this,

i_sys_aresetn => s_sys_aresetn_this,

o pwm => s pwm pwm,

i axil 32 pkg mosi saxil => s axil 32 pkg mosi maxil uart,

o_axil_32_pkg_miso_saxil => s_axil_32_pkg_miso_maxil_uart

u uart : entity work.uart

port map (

i sys clk => s sys clk this,

i_sys_aresetn => s_sys_aresetn_this,

o axil 32 pkg mosi maxil => s axil 32 pkg mosi maxil uart,

i axil 32 pkg miso maxil => s axil 32 pkg miso maxil uart,

i rx uart => s rx uart this,

o tx uart => s tx uart this

end rtl;

```

```

---Entity declaration

entity uart core is

port (

i_sys_clk : in std_ulogic;

i sys aresetn : in std ulogic;

o axil 32 pkg mosi maxil : out work.axil 32 pkg.r axil mosi;

i axil 32 pkg miso maxil : in work.axil 32 pkg.r axil miso;

i rx uart : in std ulogic;

o tx uart : out std ulogic

Lend uart core;

architecture rtl of uart_core is

begin

--Dummy signal assignments to outputs - delete as needed

o_axil_32_pkg_mosi_maxil.s_axi awaddr

<= (others => '0');

o_axil_32_pkg_mosi_maxil.s_axi awprot

<= (others => '0');

o axil 32 pkg mosi maxil.s axi awvalid <= '0';

o axil 32 pkg mosi maxil.s axi wdata

<= (others => '0');

o axil 32 pkg mosi maxil.s axi wstrb

<= (others => '0');

o_axil_32_pkg_mosi maxil.s axi wvalid

o axil 32 pkg mosi maxil.s axi bready

<= '0':

o_axil_32_pkg_mosi_maxil.s_axi_araddr

<= (others => '0');

o axil 32 pkg mosi maxil.s axi arprot

<= (others => '0');

o_axil_32_pkg_mosi_maxil.s_axi arvalid

<= '0':

<= '0':

o_axil_32_pkg_mosi_maxil.s_axi_rready

o_tx_uart <= '0';

end rtl;

```

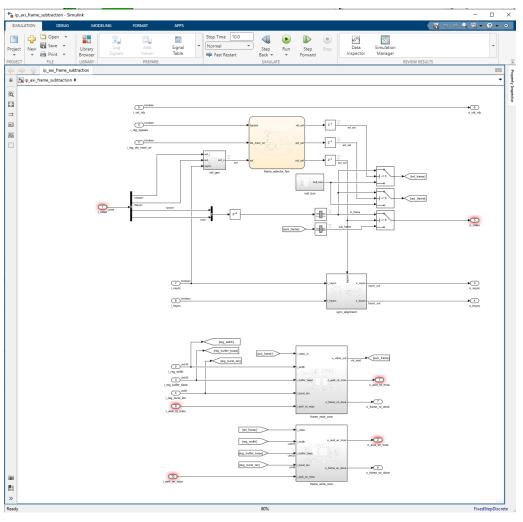

#### Simulink HDL Coder - Frame Subtraction

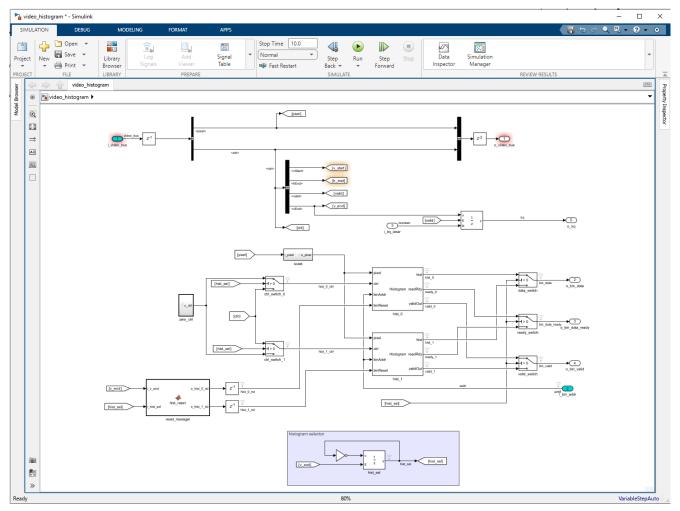

## Simulink HDL Coder - Histogram

### What does HDL Code OP look like?

```

c_2_process : PROCESS (i_clk, i_aresetn)

BEGIN

IF i aresetn = '0' THEN

alpha reg 2 <= (OTHERS => '0');

ELSIF i clk'EVENT AND i clk = '1' THEN

alpha reg 2(0) <= ctrl vStart;

alpha reg 2(1) \le alpha reg 2(0);

END IF:

END PROCESS c 2_process;

ctrl vStart 1 <= alpha reg 2(1);

c 3 process : PROCESS (i clk, i aresetn)

BEGIN

IF i aresetn = '0' THEN

alpha reg 3 <= (OTHERS => '0');

ELSIF i clk'EVENT AND i clk = '1' THEN

alpha reg 3(0) <= ctrl vEnd;

alpha reg 3(1) \le alpha reg 3(0);

END IF:

END PROCESS c 3 process;

ctrl vEnd 1 <= alpha reg 3(1);

c_4_process : PROCESS (i_clk, i_aresetn)

BEGIN

IF i aresetn = '0' THEN

alpha reg 4 <= (OTHERS => '0');

ELSIF i clk'EVENT AND i_clk = '1' THEN

alpha reg 4(0) <= ctrl valid;

alpha_reg_4(1) <= alpha_reg_4(0);

END IF;

END PROCESS c 4 process;

```

```

CASE is frame selector fsm IS

WHEN IN active frame =>

sf internal predicateOutput := hdlcoder to stdlogic((sof AND bypass) = '1');

IF sf internal predicateOutput = '1' THEN

is_frame_selector_fsm_next <= IN_bypass_ref;

ref sel <= '1';

act sel <= '0';

out sel <= '1';

b sf internal predicateOutput := hdlcoder to stdlogic((sof AND ( NOT bypass)) = '1');

IF b_sf_internal_predicateOutput = '1' THEN

is frame selector fsm next <= IN ref frame;

ref sel <= '1';

act sel <= '0';

out sel <= '0';

ref sel <= '0';

act sel <= '1';

out sel <= '0';

END IF:

END IF;

WHEN IN bypass act =>

sf internal predicateoutput 0 := hdlcoder to stdlogic((sof AND bypass) = 'l');

IF sf_internal_predicateoutput_0 = '1' THEN

is frame selector fsm next <= IN bypass ref;

ref sel <= '1';

act sel <= '0';

out_sel <= '1';

b sf internal predicateoutput 0 := hdlcoder to stdlogic((sof AND ( NOT bypass)) = '1');

IF b sf internal predicateoutput 0 = '1' THEN

is frame selector fsm next <= IN ref frame;

ref sel <= '1';

act sel <= '0';

out sel <= '0';

ref sel <= '1';

act sel <= '0';

out sel <= '1';

END IF;

END IF;

```

## **Conclusion & Wrap Up**

- Model Based approach is helping on time delivery & quality of design

- Major benefit is functionality designed and verified in single environment of Simulink.

- Code is portable frees us from Vendor Which HLS would not do.

- Need to decide on what we do with Adiuvo FPGA Architect tool

- Develop, Open Source, Keep as internal advantage!

- Question?

www.adiuvoengineering.com

info@adiuvoengineering.com