# **LC-link** by mec

#

## Evaluation of the DARE65T platform: technology study, IP library development and Demonstrator ASIC design

## VAN DE BURGWAL, Marcel GORBUNOV, Maxim BERTI, Laurent

IC-Link, customized solutions for innovative chip manufacturing

## Tambara, Lucas

Part 2

# Validation, characterization and irradiation testing of the DARE65T platform

<u>Marcel van de Burgwal</u>, El Hafed Boufouss, Bastien Vignon, Laurent Berti, Michael Kakoulin Imec.IC-link ASIC Design

Continuation of article presented on AMICSA 2022

ເງຍ

#### Outline

- DARE65T platform (imec)

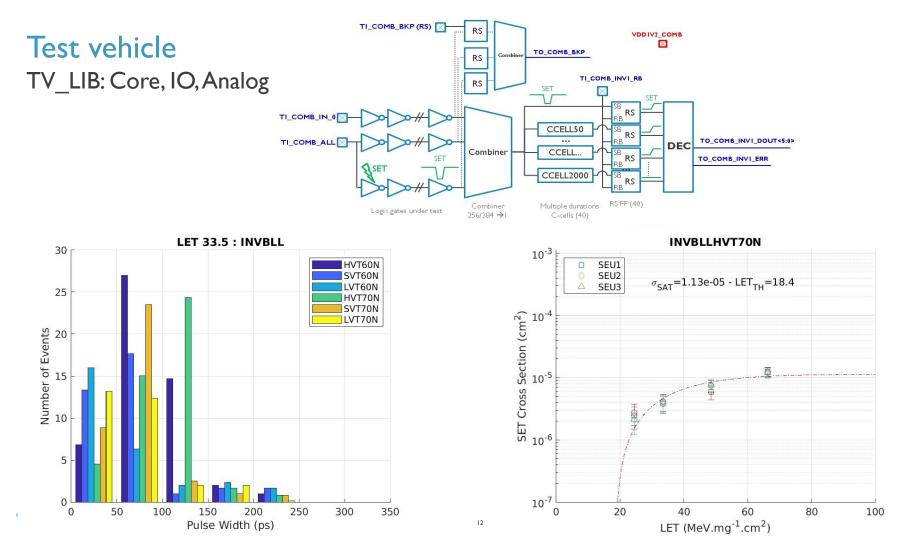

- Test Vehicles (imec)

- Demonstrator (Frontgrade Gaisler)

#### Analog design kit DARE65T\_ADK

Schematic RH rules checks

(script)

Layout RH rules checks (Calibre)

SET simulation environment (Striker & prober)

Customer analogue IP design

unec

#### Standard cell library DARE65T\_CORE

|                                                                             | Туре                                        | #   |

|-----------------------------------------------------------------------------|---------------------------------------------|-----|

|                                                                             | Non-SET hardened combinational cells        | 52  |

| <ul> <li>Multi-VT (HVt, SVt, LVt) support</li> </ul>                        | SET hardened combinational cells - 25 MeV   | 7   |

| digital/analogue on ton 9 design flow support                               | SET hardened combinational cells - 40 MeV   | 7   |

| <ul> <li>digital/analogue-on-top &amp; design flow support</li> </ul>       | SET hardened combinational cells - 60 MeV   | 7   |

| I2 track library – 0,2 um pitch                                             | Non-SET hardened sequential cells           | 9   |

|                                                                             | SEU hardened sequential cells <sup>2)</sup> | 5   |

| <ul> <li>SET &amp; SEU hardened cells for clock &amp; reset tree</li> </ul> | ANTENNA cells                               | I   |

| <ul> <li>SET hardened combinational cells</li> </ul>                        | TIEH and TIEL                               | 2   |

|                                                                             | Non-SEU hardened clock gating cells         | I   |

| <ul> <li>SEU hardened flipflops and latches (DICE)</li> </ul>               | SEU hardened clock gating cells             | 3   |

| Raw gate density ~344 kGates/mm <sup>2</sup>                                | Filler cells                                | 8   |

|                                                                             | Total                                       | 102 |

# IO libraries (I)

| Library      | Main features                                                                                   |  |

|--------------|-------------------------------------------------------------------------------------------------|--|

| DARE65T_IO   | Uni- and bidirectional LVCMOS cells                                                             |  |

|              | cold-spare feature                                                                              |  |

|              | slew rate control                                                                               |  |

|              | <ul> <li>programmable drive strength and pull up/down</li> </ul>                                |  |

|              | <ul> <li>supports 1.8/2.5V &amp; 3.3 V supply voltage (maximum supply voltage 3.63V)</li> </ul> |  |

|              | ESD: 2 kV HBM                                                                                   |  |

|              | <ul> <li>Support cells (supply, fillers, corners, breakers)</li> </ul>                          |  |

| DARE65T_LVDS | Transmitter and receiver IO cells                                                               |  |

|              | <ul> <li>based on 2.5 V overdrive 3.3 transistors</li> </ul>                                    |  |

|              | <ul> <li>2.5 and 3.3 V voltage supply</li> </ul>                                                |  |

|              | • up to 400 Mbps (200 MHz)                                                                      |  |

| Library      | Main features                                                                                 |  |

|--------------|-----------------------------------------------------------------------------------------------|--|

| DARE65T_SSTL | • SSTL18 cells - single ended and differential receiver and transmitter (JESD8-15A compliant) |  |

|              | • 1.8V $\pm$ 5% supply voltage                                                                |  |

|              | <ul> <li>DDR2-800 support</li> </ul>                                                          |  |

|              | • SSTL15 cells - single ended and differential receiver and transmitter (JESD79-3F compliant) |  |

|              | • 1.5V $\pm$ 5% supply voltage                                                                |  |

|              | Impedance calibration support                                                                 |  |

|              | <ul> <li>DDR3-800 support</li> </ul>                                                          |  |

#### SRAMs

| Library       | Main features                                                                      |  |

|---------------|------------------------------------------------------------------------------------|--|

| DARE65T_SPRAM | SPRAM compiler                                                                     |  |

|               | • Highly configurable: 32 up to 32k rows, 8 up to 64 columns, byte lane WE control |  |

|               | <ul> <li>Optional guard ring generation</li> </ul>                                 |  |

| DARE65T_DPRAM | OPRAM hard macro instances                                                         |  |

|               | <ul> <li>5 configurations (512x40 up to 8192x40)</li> </ul>                        |  |

|               | <ul> <li>Custom SRAM bitcell: 1.9 x 2.75 μm2</li> </ul>                            |  |

# Analogue IPs

| Library        | Main features                                                                                |

|----------------|----------------------------------------------------------------------------------------------|

| DARE65T_PLL    | 25 - 100 MHz reference frequency                                                             |

|                | • 6.25 - 1200 MHz output frequency                                                           |

|                | <ul> <li>Supply voltage 1.2V</li> </ul>                                                      |

| DARE65T_IVREF  | <ul> <li>I.2V and 2.5 supply voltages</li> </ul>                                             |

|                | 0.6V output reference voltage                                                                |

|                | Reference current output                                                                     |

|                | <ul> <li>Accuracy (before trimming) ± 2,5 %</li> </ul>                                       |

| DARE65T_ADC    | I0-bit resolution                                                                            |

|                | Integrated temperature sensor                                                                |

|                | <ul> <li>Supply voltage 1.2V</li> </ul>                                                      |

| DARE65T_DDRPHY | DDR3.0 PHY with up to 600 Mbit/s data rate                                                   |

|                | <ul> <li>Embedded DLL, impedance calibration and byte lane delay training support</li> </ul> |

|                | • 96 bit data, up to 8 ranks                                                                 |

|                | Integrated bump grid                                                                         |

#### Implementation on test vehicles

Technology devices

#### Core, IO & Analog IP

SRAM

#### Test vehicle TV\_DEV:Technology study

- TID irradition until 300krad (SiO<sub>2</sub>)

- Conclusions:

- No significant effects for decap, diode, resistors

- Up to 10% leakage variation for CORE transistors

- Up to 6mV threshold shift for IO transistors

- All variation as expected

| Devi           | ces  | Test                                       | TID effect @ 300krad(SiO <sub>2</sub> )                             |

|----------------|------|--------------------------------------------|---------------------------------------------------------------------|

| Decoupling cap |      | I <sub>LEAK</sub>                          | <1%                                                                 |

| Diode          |      | I <sub>LEAK</sub>                          | <1%                                                                 |

| Bipolar        |      | $\mathrm{V}_{\text{BE}}{=}f(I_{\text{E}})$ | Bias current >10uA: marginal drift<br>Bias current >100uA: no drift |

|                | CORE | I <sub>ON</sub>                            | <1%                                                                 |

| NMOS           |      | I <sub>LEAK</sub>                          | Up to 10% for small gate length                                     |

|                |      | $ V_{TH} $                                 | Up to 3mV for small gate length                                     |

| INIVIOS        | Ю    | I <sub>ON</sub>                            | <1%                                                                 |

|                |      | I <sub>LEAK</sub>                          | <1%                                                                 |

|                |      | V <sub>TH</sub>                            | Up to -5mV for small gate length                                    |

| PMOS           | CORE | I <sub>ON</sub>                            | <1%                                                                 |

|                |      | I <sub>LEAK</sub>                          | Up to -10% for small gate length                                    |

|                |      | $ V_{TH} $                                 | <1%                                                                 |

|                | ю    | I <sub>ON</sub>                            | <1%                                                                 |

|                |      | I <sub>LEAK</sub>                          | <1%                                                                 |

|                |      | $ V_{TH} $                                 | Up to 6mV for small gate length                                     |

| Resistor       | RNP  | R                                          | <1%                                                                 |

|                | RPP  | R                                          | <1%                                                                 |

|                | RSNP | R                                          | <1%                                                                 |

|                | RSPP | R                                          | <1%                                                                 |

Note: TID effects less than 1% are close to the noise floor and are considered as "no effect"

#### Test vehicle

#### SRAM\_TV: SPRAM, DPRAM

- TID no effects observed until 300 krad(SiO<sub>2</sub>)

- SEE

- No SEL observed

- No SETs observed in periphery

- Critical threshold ~1.5MeV/mg/cm<sup>2</sup>

SEE - Static irradiation (all-0, all-1, checkerboard)

SEE - Dynamic irradiation: continuous read, correct, write iteration and capturing errors in realtime

#### 13

## DARE65T Library development

Conclusion

- Technology:

- 65nm CMOS technology is hardly impacted by TID up to 300 krad(SiO<sub>2</sub>)

- No SEL observed during 3 test vehicle irradiations (up to 70 MeV/mg/cm<sup>2</sup>)

- Libraries:

- DARE65T platform offers a complete analog/mixed signal library and design tools for Digital and Analog ASICs

- Std cell, IOSRAM, SSTL, LVDS, PLL, current/voltage reference, ADC and DDR3 PHY

- All libraries were electrically characterized and tested under irradiation (SEE and TID)

- Design updates were made to resolve all IP weaknesses

- DARE65T is ready for complex ASIC implementations

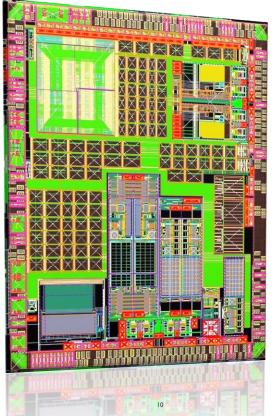

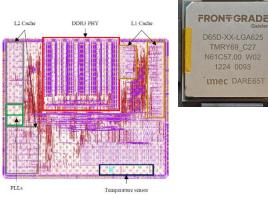

DARE65T's demonstrator ASIC developed in a collaboration between Imec and Frontgrade Gaisler.

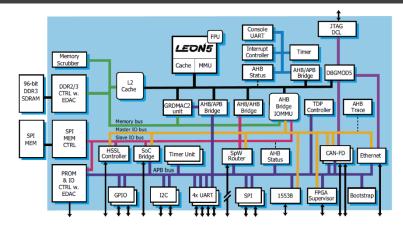

#### LEON5FT-based SoC:

- 1x LEON5FT processor core with:

- Integer unit with 8-stage dual-issue pipeline.

- 4x4 KiB instruction and 4x4 KiB data L1 caches connected to a 128-bit multi-layer bus.

- Double-precision IEEE-754 floating point unit.

- Memory Management Unit (MMU).

- 128 KiB L2 cache, 512-bit cache line, 2-ways.

- 96-bit DDR2/3 SDRAM with Reed-Solomon EDAC.

- SpaceWire router with 4 external links.

- High-speed serial link SpaceFibre controller (no on-chip Serializer/Deserializer transceiver).

- 1x 10/100/1000 Mbit Ethernet interface.

- Other interfaces, such as MIL-STD-1553B (1x), CAN-FD (2x, with CANOpen support), UART (4x), SPI (2x), I2C (2x), GPIOs, FPGA supervisor (GRSCRUB), SoC bridge, etc.

- Timers and watchdog.

- JTAG and Ethernet debug communication links.

- System frequency of 200 MHz.

#### Work performed:

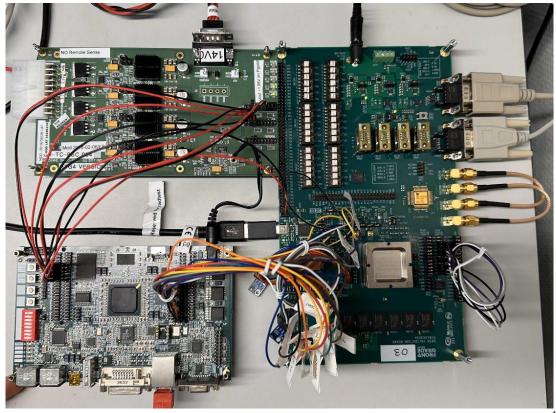

- Test platform development:

- Validation board.

- Test software.

- Functional validation of samples.

- Heavy ion SEE testing.

- TID testing.

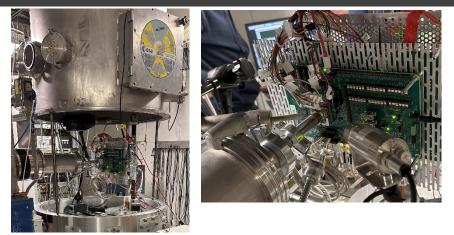

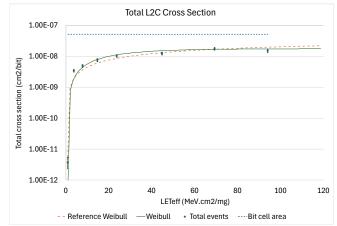

#### Heavy ion SEE testing:

- RADEF/JYU, Finland.

- 0.94 ≤ LET (MeV·cm²/mg) ≤ 94.01.

- Fluences =  $\sim 1 \times 10^7$  p/cm<sup>2</sup> per LET.

- Main results:

- SEL immunity up to an LET of 94.1 MeV·cm<sup>2</sup>/mg (tested with elevated temperature - ~100 °C – and maximum supply voltages).

- SEU results collected with the device operating in dynamic mode in agreement with reference data from the DARE65T library.

- All upsets in the cache memories were handled by the built-in fault-tolerance features of the D65D, with no evidence of error build-up observed.

- Functional results (SEFI and SDC) obtained through the execution of multiple software test cases aimed at exercising the majority of the hardware blocks of the D65D.

- Data will be presented at RADECS 2025.

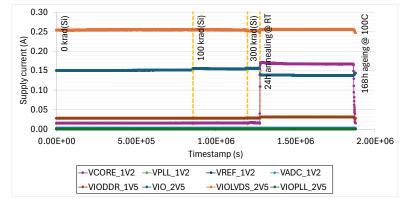

#### TID testing:

- ESA's ESTEC Co-60, The Netherlands.

- Dose rate:

- 426 rad(SiO<sub>2</sub>)/h from 0 to 100 krad(SiO<sub>2</sub>).

- 2170 rad(SiO<sub>2</sub>)/h from 100 to 300 krad(SiO<sub>2</sub>).

- Main results:

- No TID-induced failures were observed in any test sample at any test step.

- No evidence of time-dependent effects was observed in any sample after the accelerated ageing test step regardless of the biasing mode.

- Results obtained reinforce the TID tolerance of 300 krad(SiO<sub>2</sub>) of the DARE65T library.

#### Conclusion

- Evaluation of DARE65T was successful validated up to TRL 6 by Frontgrade Gaisler

- DARE65T offers standalone mixed signal libraries for Analog and Digital design flows

- Robust against TID effects up to 300krad(SiO2)

- SEE hardened cells

- For more info: <u>https://www.imeciclink.com/en/asic-services/asic-design/dare</u>

# LC-Link by mec

Lucas Antunes Tambara (lucas.a.tambara@gaisler.com)

ar

THANK YOU!

Marcel van de Burgwal (marcel.vandeburgwal@imec.be)

Customized solutions for innovative chip manufacturing