# Company Overview

June 11th, 2024

## Agenda

• What is NanoXplore?

What are our Products?

• What is our Ecosystem?

### European Leader in FPGA and SoC FPGA

- French Based Company

- Paris

- Montpellier

- 120+ Employees with more than 90% R&D Engineers

- Components Made in EU

- ITAR Free Technology

### Advanced products for an advanced market

- Amazing radiations results

- No need for design mitigations (28 nm)

- STMicroelectronics foundry

- European Sovereignty

- ITAR Free

- High Density FPGAs

- High Performances

- (HSSL)

Cryptographic Services

## Key Markets

Mission

First mission for the company is to offer SoC FPGA for Hi-Rel markets

- Focusing on key market differentiators like ITAR free, radiation hardening, very high reliability, etc

- Become quickly a clear leader on Space, Defense and Avionic market

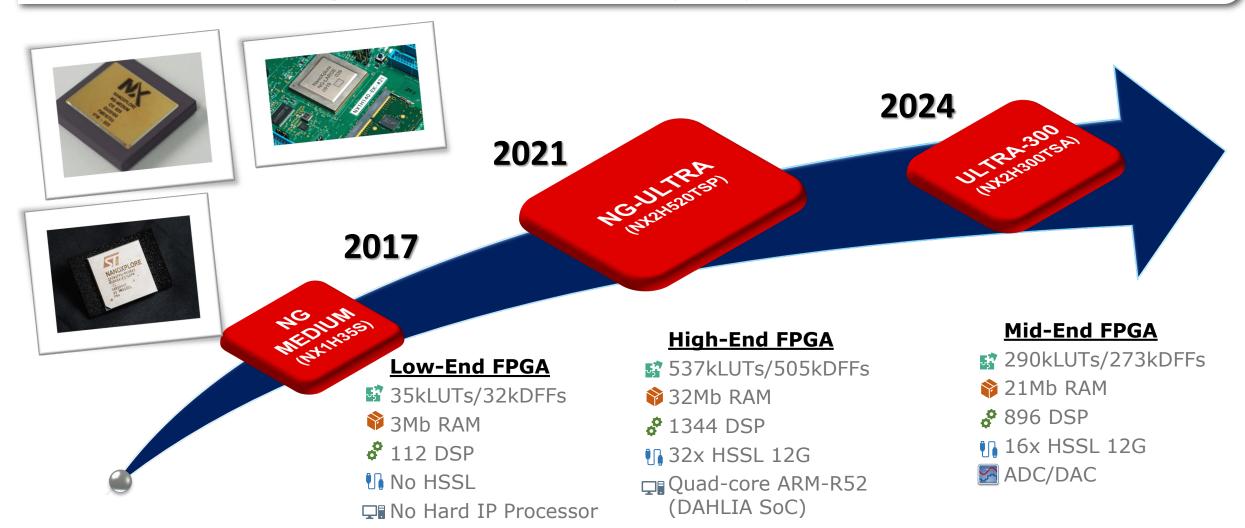

### NX Products – Overview

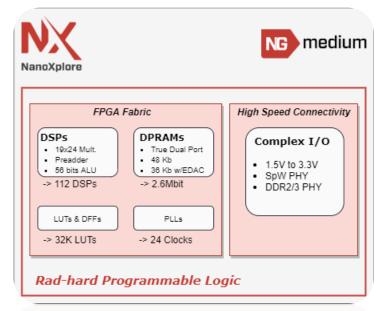

## medium

65 nm

#### **Low-End FPGA**

- 35kLUTs/32kDFFs

- 3Mb RAM

- 112 DSP

- **No HSSL**

- □ No Hard IP Processor

- Companion chip

#### **ESCC9000** qualified

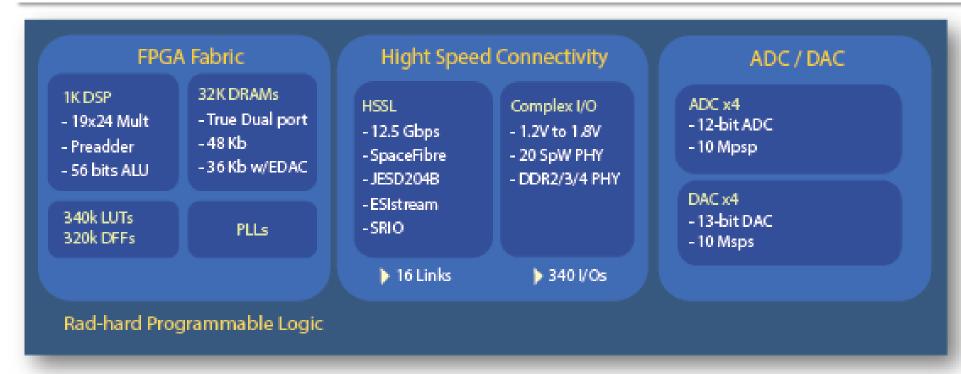

#### ultra 300

28 nm

#### **Mid-End FPGA**

- 290kLUTs/273kDFFs

- 21Mb RAM

- 896 DSP

- 16x HSSL 12G

- ADC/DAC

- Payload

- **Platform**

- Sensor control

- Power control loop

28 nm

#### **High-End FPGA**

- 537kLUTs/505kDFFs

- 32Mb RAM

- 1344 DSP

- 32x HSSL 12G

- Quad-core ARM-R52 (SoC)

- Payload

- **Platform**

#### Flight Heritage – DORN (Change'6)

#### Flight Heritage – to come

SVOM – June 22, 2024

SMILE – 20245

GALILEO CMCU – 2025

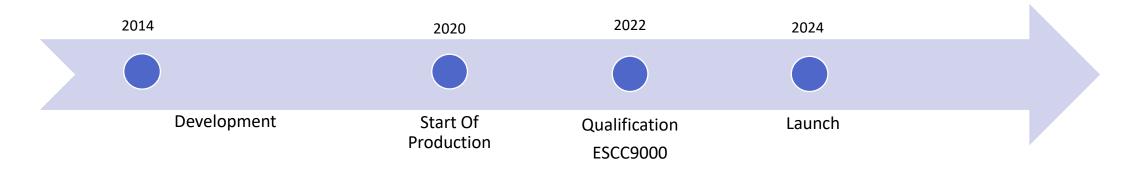

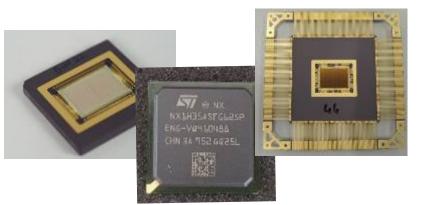

### NG-MEDIUM

- First Commercial Product

- 65nm technology

- Supply chain running for both space and general applications

- SpW & DDR2 PHY hard-coded

## NG-MEDIUM Family

Small FPGA made for Space

ESCC9000

Ceramic QFP-352 & LGA-625

High Level Immunity

Space: Class 1 & Class 2

#### Commercial grade SoC FPGA

**JEDEC**

Leadfree Plastic BGA 625

High Level Immunity

Space Constellations **Avionics** Military & Defense

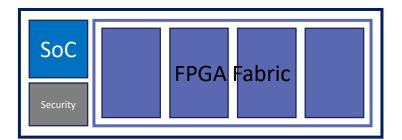

## NG-ULTRA

- 2 grades :

- ESCC9030

- JEDEC

- Dual SoC component :

- Quad Cortex-R52 @600MHz

- FPGA Fabric

- 28nm technology

- Amazing Radiation Testing Results

- Supply chain running

- First flight models already delivered

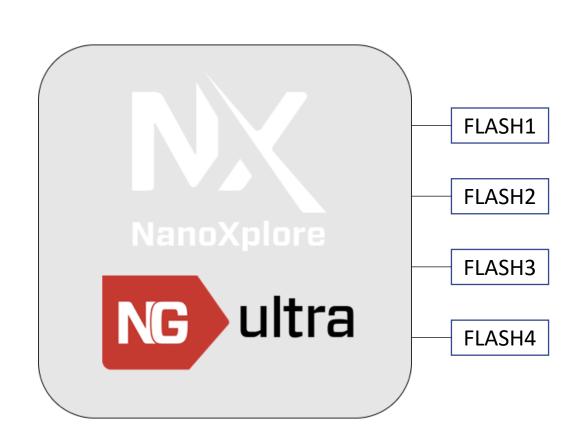

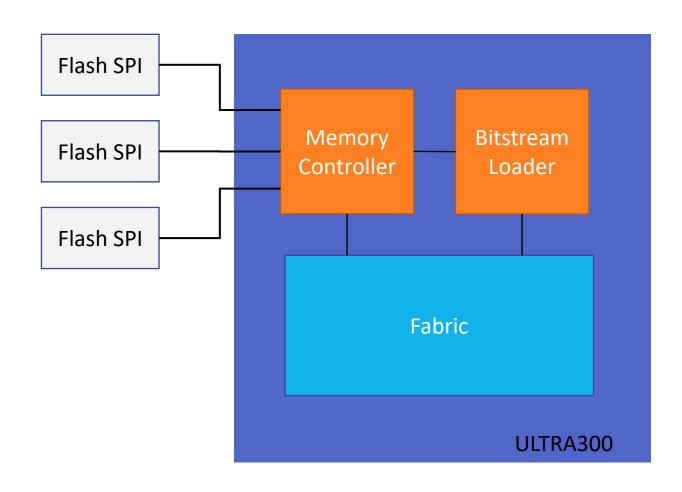

## NG-ULTRA Configuration

FLASH Loading

- 4 parallel SPI interfaces controlled by the boot loader

- FLASH mode:

- SEQUENTIAL

- TMR

- Parallel read

- NG-ULTRA performs the majority-voting

- The last memory can be used for an application purpose

## Radiation tests

All sessions

#### **NG-ULTRA FPGA Radiation test campaigns overview**

2020 U U 2021 Jun .023 2 Apr

2023 Sep

2023 U U

UCLouvain / HIF (BE)

UCLouvain / HIF (BE)

RADEF Jyväskylä (FI)

Protons

Vancouver (CA)

**DEMETER Test chips**

NG-ULTRA V1 1<sup>st</sup> prototypes

Parts thickness:  $50, 70 \mu m$ Tilt and roll possible NG-ULTRA V2 final

Parts thickness:  $\underline{100~\mu m}$  Tilt and roll not possible or high energies

## NG-ULTRA

**ESCC** Qualification

- ESCC process flow is running

- TID will be done in september

- Qualification expected in Q1/2025

## NG-ULTRA Family

All-rounder FPGA made for Space

ESCC9030

SnPb Organic BGA 1760

Fully Immune

Space Grade Capacitors

Space: Class 1 & Class 2

#### General purpose FPGA

**JEDEC**

Leadfree Organic BGA 1760

Fully Immune

General Purpose Capacitors

Space : Constellations **Avionics** Military & Defense

#### **NG-ULTRA**

### Activities and availability

- New die with HSSL fix

- Final phase of internal testing activities

| Part Number                                | Designation                       | Status |

|--------------------------------------------|-----------------------------------|--------|

| NG-ULTRA SPACE SnPb ORGANIC PACKAGE FF1760 |                                   |        |

| NX2H540BTSC-FF1760PR                       | NX2H540 FF1760 Prototype          | Q3′24  |

| NX2H540BTSC-FF1760M                        | NX2H540 FF1760 3 temp tested Part | Q3′24  |

| NX2H540BTSC-FF1760E                        | NX2H540 FF1760 eq. ESCC9030       | Q4'24  |

|                                            | NG-ULTRA EVAL KIT                 |        |

| NX2H540BTSC-EK                             | NX2H540BTSC Evaluation Kit        | Q3′24  |

- JEDEC version is on final definition phase

- First parts expected by Q4'2024 : NX2H540BTSC-FFG1760IS

- Our latest product : our All-Rounder

- HSSL @ 12 Gbps, compatible with SpaceFibre, JESD204B, ESIstream, SRIO

- ADC and DAC

- 2 Great Formats: BGA 484 (27mm\*27mm) and BGA 1152 (35mm\*35mm)

- Benefits from NG-ULTRA experience

- Radiation / Library / Testing / Supply Chain

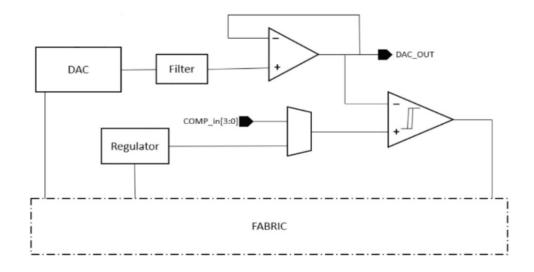

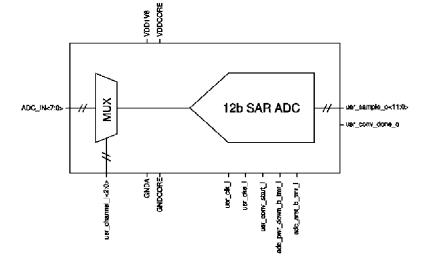

## Ultra 300

ADC & DAC

#### 13—bit DAC, 1-10 MSPS

#### 12—bit ADC, 1-10 MSPS up to 8 inputs

### ULTRA300

QSPI System

- TMR Mode

- Legacy / Standard Mode

- Bit ordering (Endianness)

- Configurable clock phase and polarity

- Debug facilities

- Internal loopback

- Power Management and latchup detection

- SPI VCC (enable / disable)

## Ultra 300

Milestones

Q3 2024 Tape-out Q3 2025 Equivalent Flight Model

Available Engineering Sample Q1 2025 Prototype Q4 2025 Qualified Flight Model

## **Ultra 300** Family

All-rounder FPGA made for Space

ultra 300 RH

ESCC9030

SnPb Organic BGA 484 & 1152

Fully Immune

Space Grade Capacitors

Space: Class 1 & Class 2

General purpose FPGA

ultra 300 JEDEC

**JEDEC**

Leadfree Organic BGA 484 & 1152

Fully Immune

General Purpose Capacitors

Space : Constellations **Avionics** Military & Defense

## Ultra 300

### Product family members availability

| Part Number          | Designation                                                          | Status  |

|----------------------|----------------------------------------------------------------------|---------|

| ULTRA 300ES EVAL KIT |                                                                      |         |

| NX2H300TSA-EK0ES     | NX2H300ES Evaluation Kit without any spacewire connectors            | Q3-2024 |

| NX2H300TSA-EKES      | NX2H300ES Evaluation Kit with 2 Spacewire connectors (Config + User) | Q3-2024 |

|                      | ULTRA 300ES Lead Free ORGANIC PACKAGE FBGA 484 SAC305                |         |

| NX2H300TSA-FFG484ES  | NX2H300ES Lead Free FBGA 484 Engineering Sample                      | Q3-2024 |

| Part Number          | Designation                                                         | Status  |

|----------------------|---------------------------------------------------------------------|---------|

|                      | ULTRA 300 ORGANIC PACKAGE FBGA 484 SnPb                             |         |

| NX2H300TSA-FF484PR   | NX2H300 SnPb FBGA 484 Prototype                                     | Q1-2025 |

| NX2H300TSA-FF484M    | NX2H300 SnPb FBGA 484 - 3 temperatures tested Part (-40 -> +125°c)  | Q2-2025 |

| NX2H300TSA-FF484E    | NX2H300 SnPb FBGA 484 eq.ESCC9030 Class 1                           | Q3-2025 |

|                      | ULTRA 300 ORGANIC PACKAGE FBGA 1152 SnPb                            |         |

| NX2H300TSA-FF1152PR  | NX2H300 SnPb FBGA 1152 Prototype                                    | Q1-2025 |

| NX2H300TSA-FF1152M   | NX2H300 SnPb FBGA 1152 - 3 temperatures tested Part (-40 -> +125°c) | Q2-2025 |

| NX2H300TSA-FF1152E   | NX2H300 SnPb FBGA 1152 eq.ESCC9030 Class 1                          | Q3-2025 |

|                      | ULTRA 300 Lead Free ORGANIC PACKAGE FBGA 484 SACN306                |         |

| NX2H300TSA-FFG484IS  | NX2H300 Lead Free FBGA 484 Industrial Space Part (-40 -> +125°c)    | Q2-2025 |

|                      | ULTRA 300 Lead Free ORGANIC PACKAGE FBGA 1152 SACN306               |         |

| NX2H300TSA-FFG1152IS | NX2H300 Lead Free FBGA 1152 Industrial Space Part (-40 -> +125°c)   | Q2-2025 |

#### **Activities**

# Impulse

New release end of June 2024

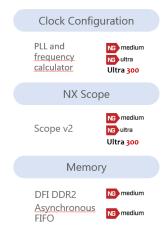

#### **IPs**

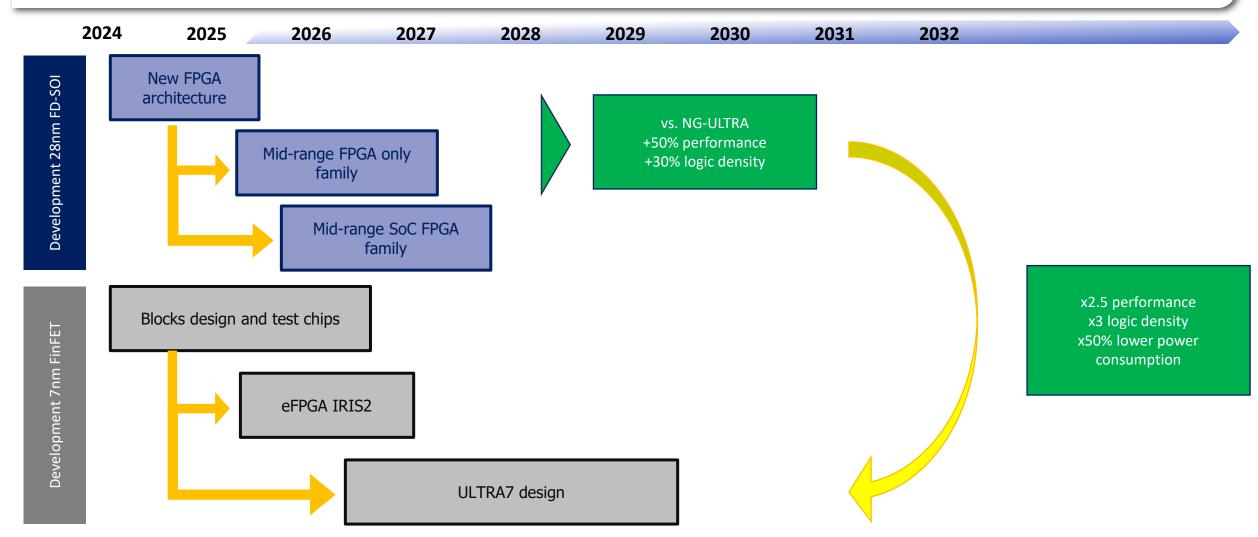

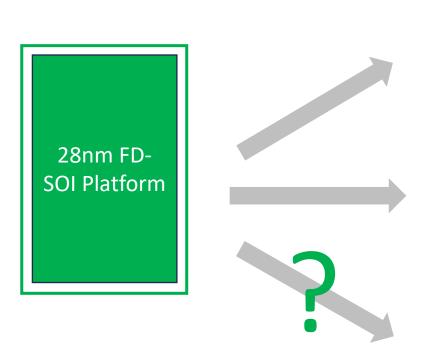

# Company Roadmap

2024

## Introduction

- Overview of NX five years roadmap

- Take benefit of NG-ULTRA development

- Continue investing in 28 FD-SOI and moving to 7nm FinFET

- 110M€ investment in the next 4 years

## Current FPGA Details

Low to high end rad-hard FPGA complexity

## SPACE vs JEDEC

#### Flows and screening comparison

|                                | NG-ULTRA COTS                                | NG-ULTRA ESCC9030                                                                                           |

|--------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Mission profile                | Life Time duration 7 years @85°C Tj 30 krads | Life Time duration 18 years @85C Tj (GEO1) 50 krads<br>Life Time duration 16 years @105C Tj (GEO2) 25 krads |

| Die                            | 28FD-SOI GEO                                 |                                                                                                             |

| Package                        | 45x45 TEFBGA non hermetic                    |                                                                                                             |

| Solder balls                   | Lead free - SACN306                          | SnPb                                                                                                        |

| Capacitors embedded in package | General purpose capacitors                   | Space grade capacitor                                                                                       |

| Visual die sorting             | NO                                           | YES                                                                                                         |

| Precap                         | NO                                           | YES                                                                                                         |

| Marking ID Serialization       | YES                                          | YES                                                                                                         |

| Thermal cycling                | NO                                           | YES                                                                                                         |

| SAM                            | Standard Control Plan                        | ESCC9030 Control Plan                                                                                       |

| XRAY and VI post-assy          | NO                                           | YES                                                                                                         |

| Qualification referential      | JEDEC                                        | ESCC9030                                                                                                    |

| Qualification maintenance      | NO                                           | YES (as defined in ESCC9030)                                                                                |

| Screening for customer parts   | EWS ambient – FT hot T°                      | ESCC9030<br>EWS ambient + FT 3T/BI/3T                                                                       |

| VI before shipment to customer | Automatic Optical VI                         | External VI + CoC                                                                                           |

| Datapack                       | NO                                           | YES                                                                                                         |

| External VI      | External VI    |

|------------------|----------------|

| FT 3 Temp        | FT 1 Temp (hot |

| Burn In          | Bush           |

| FT 3 Temp        | FT 3 mp        |

| Optical VI       | Optical VI     |

| External VI      | Extend VI      |

| Solderability    | Solds ability  |

| Baking           | Baking         |

| G-ULTRA ESCC9030 | NG-ULTRA COTS  |

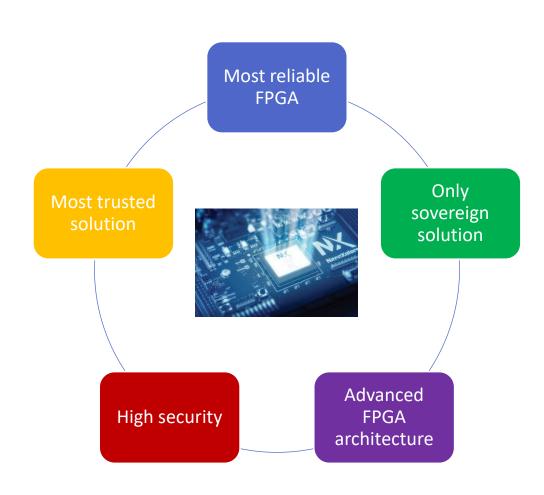

## NX Key Differentiators vs. Competition

Key technologies differentiators for the only sovereign offering

- Compared to current competition, NX offers key differentiators

- 1 Expert in design reliability (radiation, aging etc) -> main reason why end-users are selecting NX offering in Space

- Sovereign offering -> most trusted FPGA vendor for European end-users

- 3 High security features -> more and more required for strategic markets

- Leverage STMicroelectronics supply chain to benefit from previous FPGA development

- Improve our low-power and high-density FPGA architecture

- Better address application at the edge

- Clear differentiator vs. high end FPGA

### 5 Years Objectives

- Offer the best high-reliable SoC FPGA offering in the world to address the relevant markets

- Address low to high ends application complexity

- Have a dominant position in Europe in all identified strategic markets

- Worldwide footprint in the Space market

- Good presence in the US, China, South Korea, Japan

- Leader in India

- 70M€+ revenues with strong profitability

### 4 Years Roadmap Summary

Clear roadmap to address strategic markets with our differentiators

Today 2025 2026 2027

Exceed test chip

New SoC FPGA / FPGA in 28nm FD-SOI

ULTRA7 7nm FinFET

## Roadmap Summary

## 28nm FD-SOI Roadmap Objectives

First samples in 2025

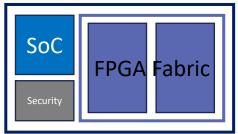

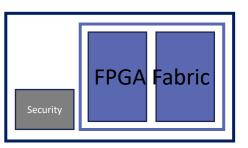

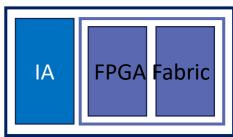

### Next SoC Generation in 28nm FD-SOI

- New FPGA architecture

- Up to 40-50% more performance vs. NG-UI TRA

- Improve logic density

- Very reliable (temperature, aging, radiation immune)

- AI friendly for NN inference -> target smart vision application

- Security at state of the art vs. other commercial FPGA

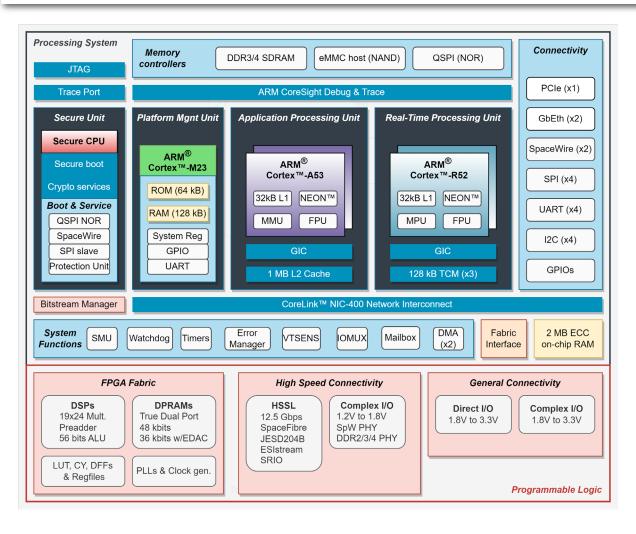

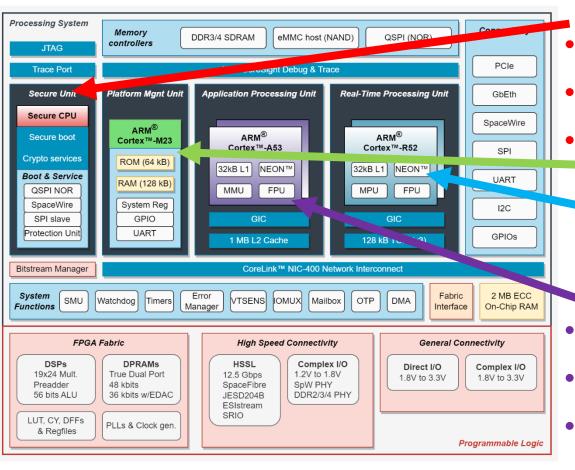

- More advanced SoC based on ARM A53 and R52

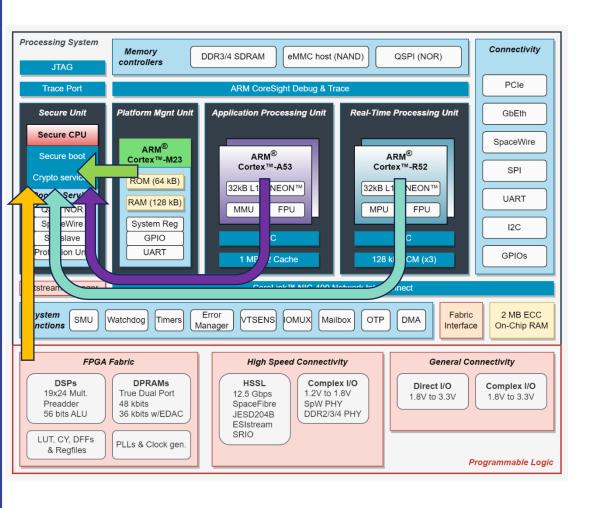

### Architecture

### **Secure Unit**

- **Root of Thrust**

- Cryptographic services

- Life cycle management System Initialization

#### **PMU**

- Low power Processing

### **APU**

- Rich OS applications

- Virtual Memory

- Cache Coherency

### **RPU**

- Deterministic Realtime applications

- Safety Features (Lock) Step)

### Cryptographic Services

- Cryptography

- AES 128, 192, 256b

- RSA 1024, 2048, 3072b

- Key generation / derivation

- HASH: SHA 256/384/512

- MAC

- Signature (ECDSA / DSA)

- Random generation

- DRNG (Hardware 32b rng)

- DRBG (SHA256 based rng)

- User applications

- Key injection / provisions

- Update binaries

## 28nm FD-SOI Roadmap

Product family

|                 | NX 50                   | NX 100   | NX 200                  | NX 300                  | NX SoC 100 | NX SoC 300              |

|-----------------|-------------------------|----------|-------------------------|-------------------------|------------|-------------------------|

| LUTs (4)        | 50k                     | 100k     | 200K                    | 300K                    | 100k       | 300K                    |

| DSP             | 100                     | 200      | 300                     | 400                     | 200        | 400                     |

| RAM             | 3 Mbits                 | 6 Mbits  | 9 Mbits                 | 12 Mbits                | 6 Mbits    | 12 Mbits                |

| HSSL @ 12,5GBs  | 4                       | 8        | 16                      | 24                      | 8          | 24                      |

| PCle Gen2       | 1 PCI                   | 1 PCI    | 1 PCI                   | 1 PCI                   | 1 PCI      | 1 PCI                   |

| Packages        |                         |          |                         |                         |            |                         |

| BGA 256 (1 mm)  | $\overline{\checkmark}$ | <u> </u> |                         |                         | <b>V</b>   |                         |

| BGA 484 (1 mm)  | $\overline{\checkmark}$ |          | <b>V</b>                | $\overline{\checkmark}$ | <b>V</b>   | $\overline{\checkmark}$ |

| BGA 784 (1 mm)  |                         |          | $\overline{\checkmark}$ | $\overline{\checkmark}$ | <b>V</b>   | <b></b>                 |

| BGA 1152 (1 mm) |                         |          |                         | $\overline{\checkmark}$ |            | $\square$               |

# N7 Objectives

- ✓ Min X4 perf vs. NG-ULTRA

- ✓ 1M LUTs

- ✓ PCIe GEN4/5

- ✓ DDR 4/5

- ✓ HSSL 56G / 112G

### Our trusted Customers

## Thank you for your time

### Jean-Louis Frigoul

Head of Sales and Marketing

sales@nanoxplore.com

www.nanoxplore.com

#### **Documentation:**

https://nanoxplore-wiki.atlassian.net