June 11, 2024

Recent Advances in European Space FPGAs: Technologies and Applications

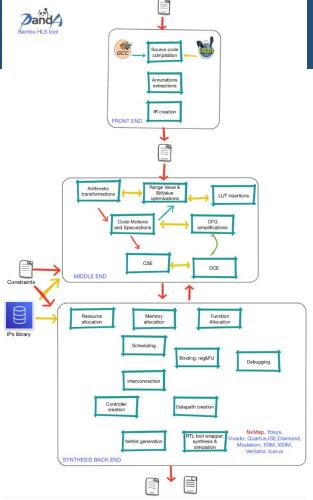

# High-Level Synthesis with Bambu: the HERMES Project Experience

**Fabrizio Ferrandi**

Politecnico di Milano, Italy,

# **Outline**

- Introduction

- Bambu HLS

- Bambu extensions

- Conclusion

# **HERMES** project

- H2020-funded project started in March 2021

- It aims at validating and evaluating a state-of-the-art rad-hard FPGA according to the standards of the European Space Components Coordination (ESCC), and at integrating design and manufacturing technologies needed to deliver high-reliability applications running on radiation-hardened integrated circuits

- Consortium is composed by

- NanoXplore, France,

- Politecnico di Milano, Italy,

- Fent Innovative Software Solutions FentISS, Spain,

- Thales Alenia Space SAS, France,

- STMicroelectronics Grenoble SAS, France,

- Airbus Defence And Space SAS, France

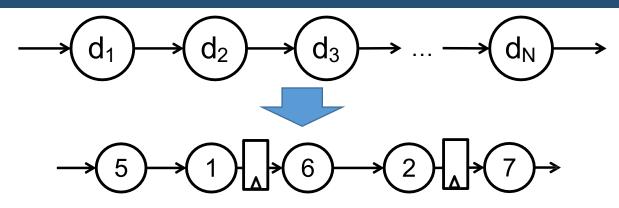

## **Bambu HLS**

- HLS tools simplify the implementation of accelerators on FPGA

- HLS starts from high-level languages (C/C++)

- Optimizes the intermediate representations

- Allocates resources

- Schedules operations

- Binds them to the resources

- And generates RTL descriptions for synthesis tools

The increased performance offered by FPGAs is made available also to software developers that do not have hardware design expertise

# Bambu: an example of modern HLS tools

- Open-source HLS tool developed at Politecnico di Milano (Italy)

- Front-end Input: interfacing with GCC/CLANG-LLVM for parsing C code

- Complete support for ANSI C (except for recursion)

- Support for pointers, user-defined data types, built-in C functions, etc...

- Source code optimizations

- may alias analysis, dead-code elimination, hoisting, loop optimizations, etc...

- Target-aware synthesis

- Characterization of the technology library based on target device

- Verification

- Integrated testbench generation and simulation

- automated interaction with Verilator, Xilinx Xsim, Mentor Modelsim

- Back-end: Automated interaction with commercial synthesis tools

- FPGA: Xilinx ISE, Xilinx Vivado, Altera Quartus, Lattice Diamond, NanoXplore

- ASIC: OpenRoad (Nangate 45, ASAP7)

# **Bambu: front-end**

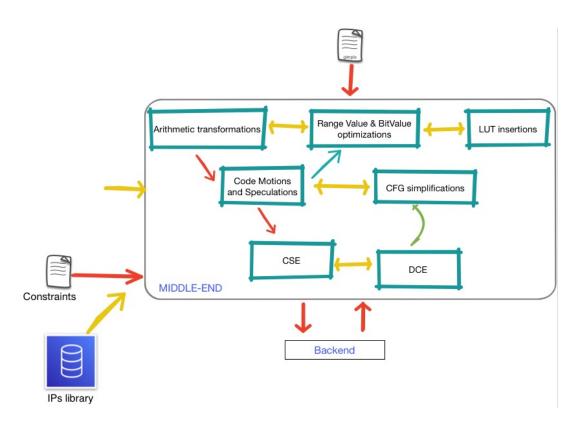

# Bambu: middle-end

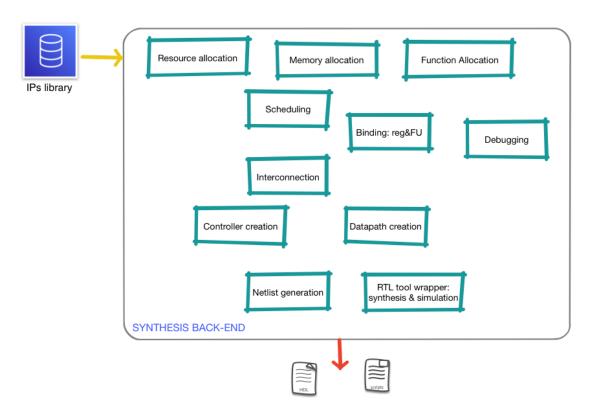

## Bambu: back-end

# Bambu – NX integration

- Seamless integration between Bambu and Impulse from NX

- automatic generation of backend synthesis scripts

- Bambu IP resource library characterized with respect to rad-hard NX FPGAs

- Resource occupation and latency under different design constraints

- Automatically performed with PandA Eucalyptus tool

# **Bambu – NX integration**

- Performance estimation essential for

- Aggressive scheduling

- Pipelining

- Code transformations

- Bambu IP library customized with respect to

- DSPs

- NG-ULTRA fabric True Dual Port RAMs

# Bambu – NX integration

Added support for NanoXplore radiation-hardened FPGAs with device-specific RTL component library characterization for:

```

• NG-MEDIUM (nx1h35S)

<cell>

NG-LARGE (nx1h140tsp)

<name>fp plus expr FU 0 32 32 100</name>

<attribute name="area" value type="float64">649</attribute>

<attribute name="REGISTERS" value type="float64">194</attribute>

<attribute name="SLICE LUTS" value type="float64">457</attribute>

NG-ULTRA (nx2h540tsc)

<template name="fp plus expr FU" parameter="0 32 32 100"/>

on timestamp>

<cell>

<name>fp plus expr FU 0 32 32 100</name>

<attribute name="area" value type="float64">649</attribute>

<attribute name="REGISTERS" value type="float64">194</attribute>

<attribute name="SLICE LUTS" value type="float64">457</attribute>

<cell>

ization timestamp>

<name>fp plus expr FU 0 32 32 100</name>

<attribute name="area" value type="float64">638</attribute>

<attribute name="REGISTERS" value type="float64">150</attribute>

<attribute name="SLICE LUTS" value type="float64">464</attribute>

<template name="fp plus expr FU" parameter="0 32 32 100"/>

<characterization timestamp>2022-05-19T10:41:00</characterization_timestamp>

<operation operation name="plus expr" commutative="1"</pre>

supported types="REAL:32" pipe parameters="100" cycles="2"

initiation time="1" stage period="19.08899999999999"/>

</cell>

```

#### **Use Cases**

- HERMES project is validating the Bambu HLS tool through typical space use cases

- image and vision processing algorithms,

- software-defined algorithms,

- artificial intelligence applications

#### Interface pragmas

- Very similar to the ones used by VitisHLS

- No Protocol (standard parameter behavior)

- FIFO, AXIS

- Handshake

- Array

- Axi4-Master

- In many cases it is possible to use the same VitisHLS syntax. Not all the options are supported.

- Added support to AXI4 master and AXIS interfaces

- Easier integration with ARM processor on the NG-ULTRA board

- Easy way to integrate existing IPs

- Automatic generation of AXI testbench supported

- Memory latency can be configured

- Unaligned accesses are supported

- AXI4 burst transactions supported

- Support for caches on AXI interfaces

- Customizable cache and line size

- Support for different write policies

- Support for associative caches

- Support for different replacement policies

- Support for larger AXI xDATA signal size

- Support for pipelined write transactions

- Automatic cache flush at the end of the computation

- Includes simulation-only hit/miss counters

- C++ FIFO interface support:

- ac\_channel<T>

- hls::stream<T>

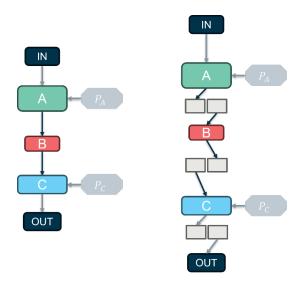

#### Dataflow support

```

class SimpleSystem {

AddBlock<5> A;

MulBlock B;

SubSystem C;

ac channel<int> x, y;

public:

void top(ac channel<int>& in1, ac channel<int>& in2,

ac channel<int>& in3,

ac channel<int>& out) {

#pragma HLS dataflow

A.compute(in1, x);

B.compute(x, in2, y);

C.compute(y, in3, out);

};

void dataflow_top(ac_channel<int>& in1, ac_channel<int>& in2,

ac_channel<int>& in3,

ac channel<int>& out) {

static SimpleSystem sys;

sys.top(in1, in2, in3, out);

```

#### Dataflow current status

- ac\_channel & hls\_stream supported

- fifo depth could be controlled by pragmas

- Struct passed as template parameter supported

- Synthesis efficiency could be improved

- Data field member support could be improved

- ac\_int and ac\_fixed supported

- Synthesis efficiency comes when PandA-Bambu is used with Clang16

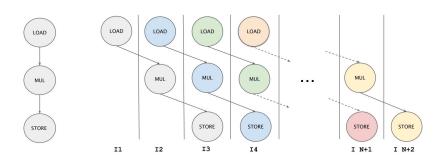

- Extended function pipelining support

- User-defined initiation interval (II)

- Optimized pipelining algorithm

- Loop pipelining overlaps execution of different iterations

- ► Requires information about operation dependencies and available resources

- Latency reduction, less area overhead than loop unrolling

- Goal: initiation interval (II) = 1

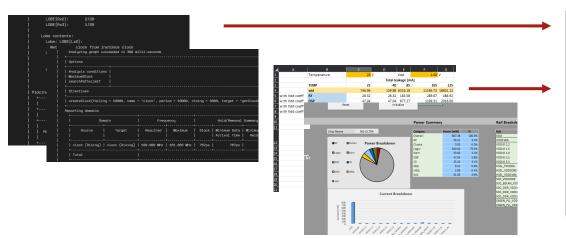

# Polimi benchmark: Polybench kernels

- Suite of basic linear algebra operations commonly used to test polyhedral optimizations.

- Synthetized on a NanoXplore NG Ultra FPGA with target clock period of 20ns (50 MHz);

- Testing the loop pipelining and loop unrolling capability of Bambu HLS with 200 different experiments.

- 82% of the experiments reached the target frequency.

# Bambu verification approach

- 1. Standard verification flow is now supported even by Bambu

- 2. Bambu additional verification approach

- Application instrumented to compare software and HW execution using the original application

- DPI-C interface used to connect the SW and the HW worlds

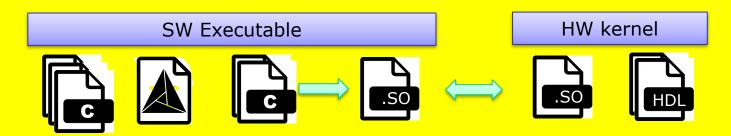

# Integrating ML-design flow in Bambu

- Research ongoing on DSLs to synthesize accelerators for machine learning-based inference.

- We did some experiments with SODA-OPT framework

- Aiming at optimizing one of the TAS use-cases.

- SODA-OPT jointly developed by PNNL, Northwestern University and Politecnico di Milano

Translate to MLIR II MLIR Kerne MLIR Host Analysis & Operations to Runtime Low-Level Low-Level FPGA or Host Executable

**High-Level Framework**

Serena Curzel, Nicolas Bohm Agostini, Vito Giovanni Castellana, Marco Minutoli, Ankur Limaye, Joseph B. Manzano, Jeff Zhang, David Brooks, Gu-Yeon Wei, Fabrizio Ferrandi, Antonino Tumeo: End-to-End Synthesis of Dynamically Controlled Machine Learning Accelerators. IEEE Trans. Computers 71(12): 3074-3087 (2022)

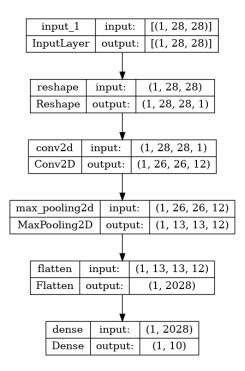

# **MNIST** example

|           | NG-Ultra embedded |

|-----------|-------------------|

| LUTS      | 4627              |

| Registers | 5714              |

| Frequency | 45.7 MHz          |

| DSP       | 54                |

| MEM       | 34                |

| cycles    | 169,649           |

- 8-bit quantized

- Tensorflow 2.15

- Clang 18

- MLIR based design flow

#### Conclusion

- FPGAs are very versatile and suitable for many markets

- Integrating HLS will improve productivity

- Raise the level of abstraction to develop rad-hard FPGA-based applications

- Raise the Technology Readiness Levels (TRL) of the Bambu HLS tool

# Questions

#### HERMES PROJECT – H2020

Qualification of High-pErformance pRogrammable Microprocessor and dEvelopment of Software ecosystem

https://www.hermes-h2020project.eu/

https://panda.dei.polimi.it

https://github.com/ferrandi/PandA-bambu

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement N° 101004203