### **ADCSS 2014**

### ARCHITECTURAL TRADE-OFFS: AVIONICS ARCHITECTURE NON-FUNCTIONAL ANALYSIS

**Avionics Modelling Language AAML**

2014, October 28th

### **CONTENTS**

- 1. Introduction and objectives.

- 2. Process.

- Use case results.

- 4. Conclusions and future work.

# INTRODUCTION AND OBJECTIVES

### INTRODUCTION

- The ESA AAML (Avionics Architecture Modelling Language) study aims at advancing the avionics engineering practices towards a model-based approach.

- Consortium led by GMV:

- Project Kick-Off Meeting on February 2013.

- Project Acceptance Review on April 2014.

### SCOPE AND BACKGROUND

- Defining an avionic architecture for a given project means making several key architecture choices and sizing several performance parameters.

- The selection is usually based on:

- The architect's expertise and background.

- Avionics-specific analyses (to perform trade-offs).

#### Traditional process:

- Each type of analysis is based on a dedicated model.

- Some training is required to be used effectively.

#### AAML model-based approach:

- Usage of a single architectural model.

- The same input is used to perform different avionics analyses.

- The analyses cover most of the phases of the life-cycle.

### **PROCESS**

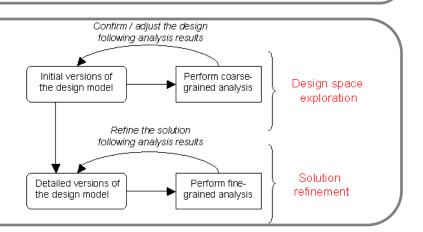

### **MODELLING PROCESS**

**Avionics Functional Definition**

- Used to design the avionics system as a set of high-level functions.

- It answers directly to what the avionics is supposed to do.

Logical **Architecture Definition**

Representation of how the system will work so as to fulfil the requirements and expectations of the users.

**Physical Architecture Definition**

It represents how the system will be concretely developed and built using real components.

### **AVIONICS ANALYSIS**

- Satellite mode definition, RAMS, FDIR and autonomy concept

- Design consistency and correctness checks

- Commandability and Observability

- Bus/Network load & latency analysis

- Space/ground communication

- Avionic resources analysis

- On-board functions and performance

- Power and mass analysis

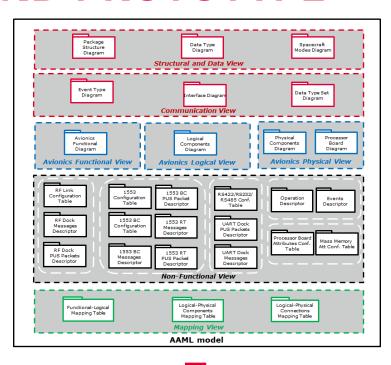

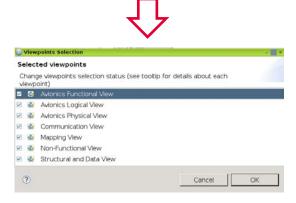

### MODELLING LANGUAGE AND PROTOTYPE

- □ AAML Modelling Language.

- Domain Specific Language.

- Inspired by the Space Component Model.

- □ Prototype:

- Demonstrator for a graphical editor (design views) and analyses tools.

- Technology:

- Eclipse.

- Obeo Designer.

- Capabilities:

- Management of an AAML model through the graphical editor.

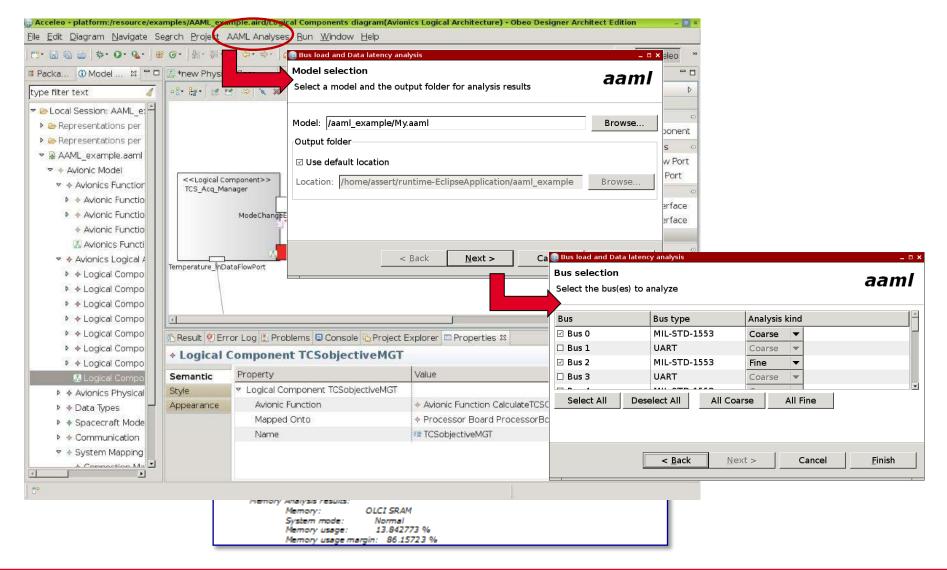

- Configuration of the avionics analyses from a GUI based on Eclipse wizards.

- Execution of the avionics analyses.

- Identification of model inconsistences.

### **TOOLING: AVIONICS ANALYSES**

- Commandability and observability.

- Goal: Size the RF communication system.

- Metrics: Data throughput, link occupation, link occupation margin.

- Bus load and data latency.

- Goal: Size the MIL-STD-1553B bus and RS-422/RS-232/RS-485 serial links.

- Metrics: Data latency, message transmission time, bus load, bus margin, bus utilization.

- MIL-STD-1553B schedulability analysis.

- On-board functions and performance.

- Goal: Analyse the CPU load and memory sizing.

- CPU Metrics: CPU usage, CPU throughput, CPU usage margin.

- Memory Metrics: Non-volatile/volatile memory size, non-volatile/volatile memory margins.

## USE CASE RESULTS

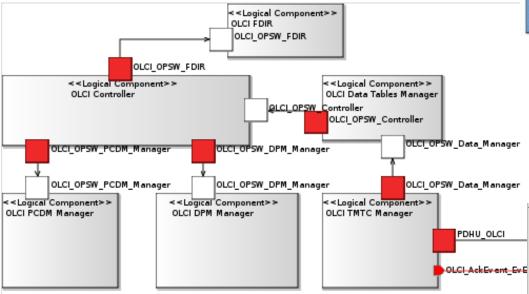

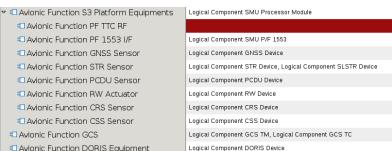

OLCI On-board software

### USE CASE - DESIGN (1/3)

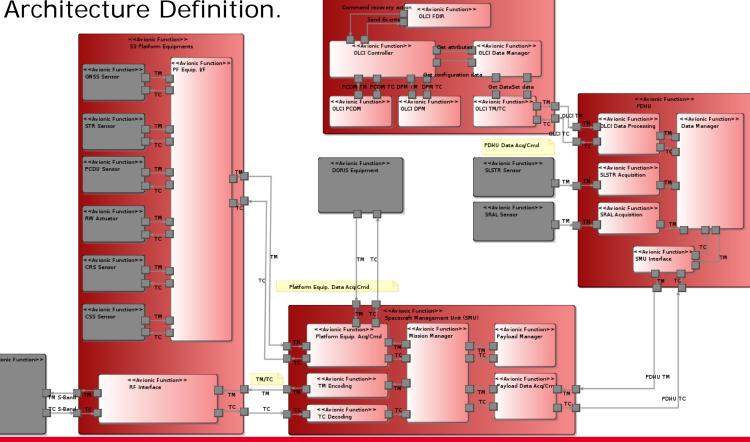

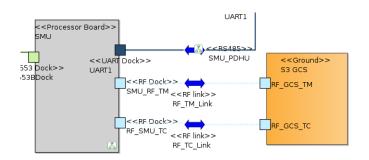

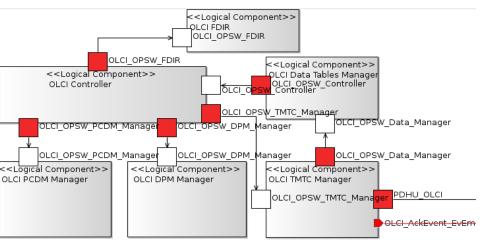

Functional Architecture Definition.

Logical Architecture Definition.

Physical Architecture Definition.

### USE CASE - DESIGN (2/3)

- Functional Architecture Definition.

- Logical Architecture Definition.

- Physical Architecture Definition.

<<irterface>>

PDHU\_OLC(\_Ac)

@ GetOLC(NormalData

@ GetOLC(CalibrationDat

> OLC() LalibrationDat

> OLC() LalibrationDat

> OLC() LalibrationDat

> OLC() LalibrationDat

<<ir>erface>>

PDHU\_SLSTR\_Ao

GetSLSTRDayData( OUT SLSTR\_C

GetSLSTRNightData

SLSTR\_DayData: SLSTR\_Da

SLSTRNightData: SLSTR\_Nig

PDHU UART Aca/Cmd

<interface>>

PDHU\_SRAL\_Acq\_CA

@ GetSRALCNI\_LRM\_IQ;

@ GetSRALCNI\_SAR

@ GetSRALCNI\_SAR

@ GetSRALCNI\_SAR

\$ SRALCNI\_LRM\_IQQ: SRAL\_TM\_CAL1\_LRM\_IC

\$ SRALCNI\_LRM\_IQ: SRAL\_TM\_CAL1\_LRM\_IC

\$ SRALCNI\_LRM\_IQ: SRAL\_TM\_CAL1\_LRM

\$ SRALCNI\_SAR: SRAL\_TM\_CAL1\_SF

\$ SRALCNI\_SAR: SRAL\_TM\_CAL2\_SF

\$ SRAL\_TM\_CA

OLCI OPSW Interfaces

<<ird><<ird><<ird><<ird><<ird>OLCI\_OPSW\_Controlle

Time\_ManageStartup(

OFCLK:4\_Scheduler

<<interface>>

OLCI\_OPSW\_TMTC\_Manage

SMU\_If\_TM\_Bus\_Manage

SMU\_If\_TC\_Bus\_Manage

SMU\_If\_Non\_Pus\_Manage

Commandability\_TC\_Serv

|                                                   | S/C Mode    | Type [S/A]  | Freq./MIAT [Hz] |

|---------------------------------------------------|-------------|-------------|-----------------|

| ♦ Operation: GetDoppler                           |             | SYNCHRONOUS | 1.0             |

| <ul> <li>Operation: GetITRFNavigation</li> </ul>  | Mode Normal | SYNCHRONOUS | 1.0             |

| Operation: GetGeodesicalNavigation                | Mode Normal | SYNCHRONOUS | 1.0             |

| <ul> <li>Operation: GetJ2000Navigation</li> </ul> | Mode Normal | SYNCHRONOUS | 1.0             |

| Operation: GetDatation                            | Mode Normal | SYNCHRONOUS | 1.0             |

| Operation: GetRoutine                             | Mode Normal | SYNCHRONOUS | 1.0             |

| Operation: GetAnomaly                             | Mode Normal | SYNCHRONOUS | 1.0             |

| ♦ Operation: Polling                              | Mode Normal | SYNCHRONOUS | 4.0             |

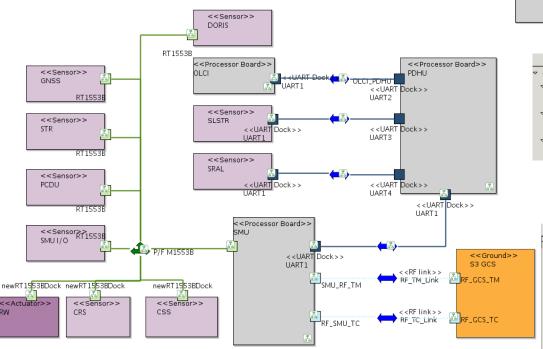

### USE CASE - DESIGN (3/3)

#### FDHU-SRAL RS232/RS422/RS485 Config

- Functional Architecture Definition.

- Logical Architecture Definition.

- Physical Architecture Definition.

|                                       | S/C Mode    | Type [S/A]   | Freq./MIAT [Hz] | Packet Standard |

|---------------------------------------|-------------|--------------|-----------------|-----------------|

| ▼ ♦ UART Dock: UART1                  |             |              |                 |                 |

| ▼ ♦ Operation: GetOLCINormalData      | Mode Normal | SYNCHRONOUS  | 22.7272         |                 |

| Packet Standard                       |             |              |                 | PUS             |

| ▼ ♦ Operation: GetOLCICalibrationData | Mode Normal | SYNCHRONOUS  | 22.7272         |                 |

| Packet Standard                       |             |              |                 | PUS             |

| → Event: AckEvent                     | Mode Normal | ASYNCHRONOUS | 22.727274       |                 |

| Packet Standard                       |             |              |                 | PUS             |

|                                       |             |              |                 |                 |

- ♦ Instructions Per Line Of Code (only required for FINE analysis): 5

- → Volatile Memory OLCI SRAM

→ Data Size: 8 MByte

- ▼ ♦ Non Volatile Memory OLCI PROM

|   |                                       | oci vice iype | Dab Del vice lype | Data Field [Dyce] | Overrieda (Byce) | 14 1 0011000 |

|---|---------------------------------------|---------------|-------------------|-------------------|------------------|--------------|

|   | ♥ + UART Dock: UART1                  |               |                   |                   |                  |              |

| 1 | ⋄ ♦ Operation: GetOLCINormalData      |               |                   |                   |                  |              |

| ı | ♥ ♦ PUS Descriptor                    | 1             | 1                 | 33582.0           | 20.0             |              |

| ı | Number Packets                        |               |                   |                   |                  | 5            |

| ı | ⋄ ♦ Operation: GetOLCICalibrationData |               |                   |                   |                  |              |

| ı | ♥ ♦ PUS Descriptor                    | 1             | 1                 | 35490.0           | 20.0             |              |

| ı | Number Packets                        |               |                   |                   |                  | 10           |

| ı | ⋄ ♦ Event: AckEvent                   |               |                   |                   |                  |              |

| Į | ♥ + PUS Descriptor                    | 1             | 1                 | 2.0               | 20.0             |              |

|   | A November Desirate                   |               |                   |                   |                  | 4            |

Service Type | Sub-Service Type | Data Field [Byte1] Overhead [Byte1] Nº Packets

### **USE CASE – ANALYSES**

### **C&O AND BUS LOAD RESULTS**

- Commandability and observability.

- TM link at very low level of occupation (1.3-2.6%).

- TC links:

- o Assumption of <u>visibility window</u> of 10 min.

- TC upload of SRAL binary: 7974 bps, 55.1% of occupation.

- o TC upload of CSW binary: 20796 bps, 143.7% of occupation.

- □ Bus load: 1553B.

- Scheduling: Major frame of 1000 ms and a minor frame of 125 ms.

- Fine-grained analysis computes a bus load of 14%.

- Bus load: UART.

- Fine-grained analysis detects that SRAL-PDHU data exchange exceeds bus capability (due to calibration messages).

- Bus 'SRAL\_PDHU'

Mode 'Normal':

Bus load: 118.250046 %

Bus system load: 119.00389 %

Data throughput: 59125020 bps

- After introduction of calibration mode the bus load is reduced to 55.4% (normal) and 62.8% (calibration).

ADCSS 2014 - AAML - E.Alaña 28/10/2014 Page 16 © GMV

### ON-BOARD FUNCTIONS AND PERFORMANCE RESULTS

- On-board functions and performance.

- Firstly, only one EEPROM is used.

- The fined-grained analysis detects:

- Computation of CPU load of OLCI OPSW: 51.6%.

- o SRAM occupation of **35.7%** (below 50%).

- High EEPROM1 occupation: 124.4%.

- Reallocation of DPM, PCDM, FDIR, PDHU PL and SMU logical components over EEPROM2:

- EEPROM1 occupation: 67.3%.

- EEPROM2 occupation: 56.9%.

# CONCLUSIONS AND FUTURE WORK

### **CONCLUSIONS AND FUTURE WORK**

- AAML study has provided:

- Identification and evaluation of the avionics analyses.

- AAML modelling language:

- The AAML entities are precise and practical enough for capturing the avionics architecture and to be used as input for specialized avionics analysis.

- It supports the possibility of both coarse- and fine-grained specification by means of the non-functional properties defined.

#### • AAML toolset:

ADCSS 2014 - AAML - E.Alaña

- It allows the design and analysis of the avionics system through the different development phases.

- Future work activities in the modelling language and the toolset have been identified. Some examples:

| Future Work                                                              | Priority |

|--------------------------------------------------------------------------|----------|

| Extend the meta-model and toolset to support additional avionic analyses | MEDIUM   |

| Improve the analysis reports output format                               | MEDIUM   |

| Develop and independent model consistency validator                      | HIGH     |

| Include hierarchy levels                                                 | MEDIUM   |

### Thank you!

Elena Alaña Salazar ealana@gmv.com

Space Systems Business Unit Avionics & On-Board SW Division

Presented by

Marco Panunzio – Thales Alenia Space marco.panunzio@thalesaleniaspace.com