# **FPGA Meets Systems Engineering**

**Integrating Approaches for Space Applications**

Stephan van Beek

European Technical Specialist SoC/FPGA Design Flows

#### Challenges – complexity

2025

### 1 FPGA engineer,1 board with 4 FPGAs

- Applications: logic interfaces, very simple algorithms

- Xilinx XC4000 resources

(DSPs 0, Logic Cells, RAM)

- Schematic entry →

hybrid schematic entry + VHDL

#### Multiple FPGA engineers, 1 board with 1 FPGA

- Applications:

more complex algorithms

- Xilinx Virtex-5 resources

(DSPs, Logic Cells, BRAM, Embedded Processor)

- VHDL → MBD (FPGA)

## Team of engineers (algorithm, architect, FPGA, software) for 1 board with 1 SoC

- Applications: very complex algorithms (artificial intelligence, wireless, signal processing, vision, motor/power, etc.)

- AMD Versal resources (Logic Cells, DSP engines, Al engines, BRAM, URAM, ARM)

- Will this be the next evolution? →MBD (SoC/FPGA) + MBSE??

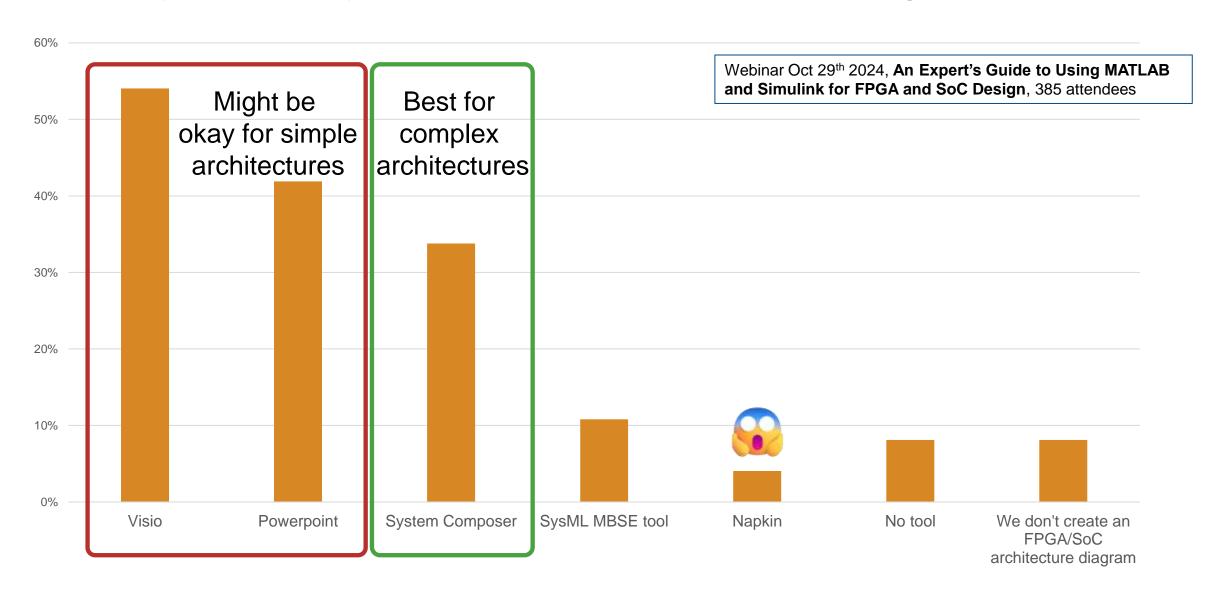

#### How do you create your FPGA architectural block diagrams?

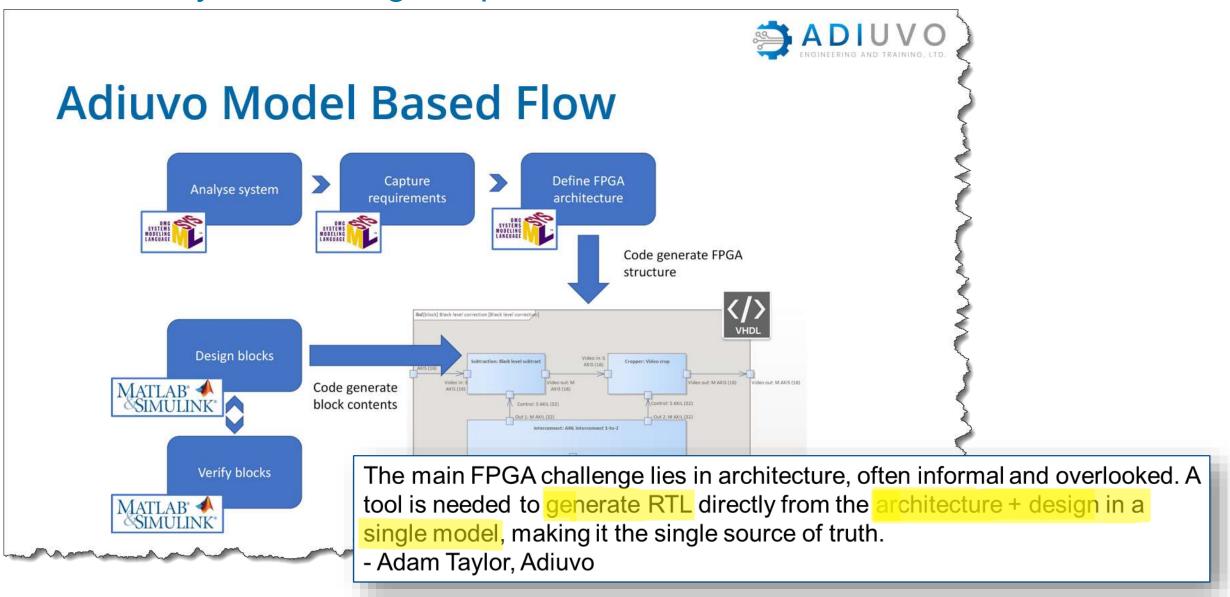

#### Adam Taylor is on a good path here ......

### Challenges – complexity → needs

- Top-down design processes

- Functional decomposition

- No simulation needed early, but ..... later you will need simulation

- Go Beyond Textual Requirements

- Use expressiveness of requirement models and trade studies

- Use views to put stakeholder discussions in context

- Validate compliance to requirements through simulation

- Deployment

- Generate RTL code from architecture + design models

Model-Based Systems Engineering + Model-Based Design

Top-down

Bottom-up

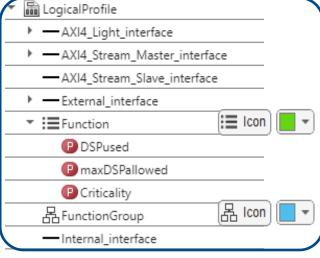

**Custom Profiles**

Integrate MBD with MBSE

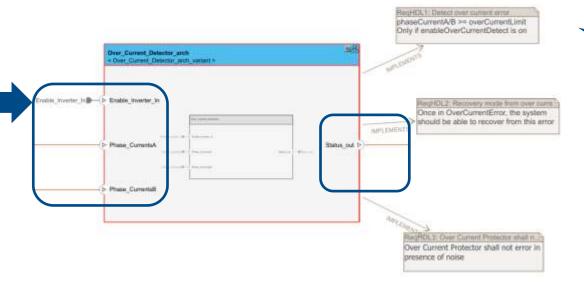

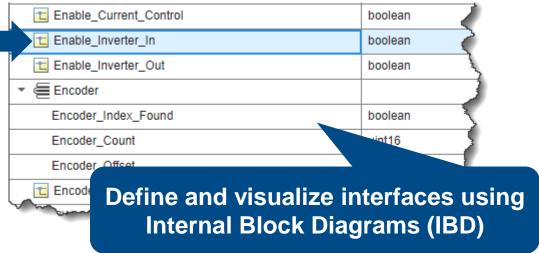

#### Requirements: Textual, Traceability, Interfaces, Interactions

Establish traceability between architecture & design and textual requirements

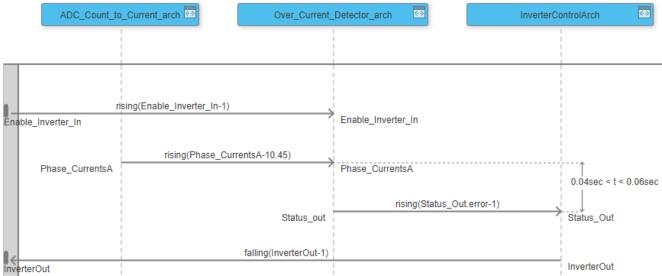

Define interface behaviors using Sequence Diagrams (SD)

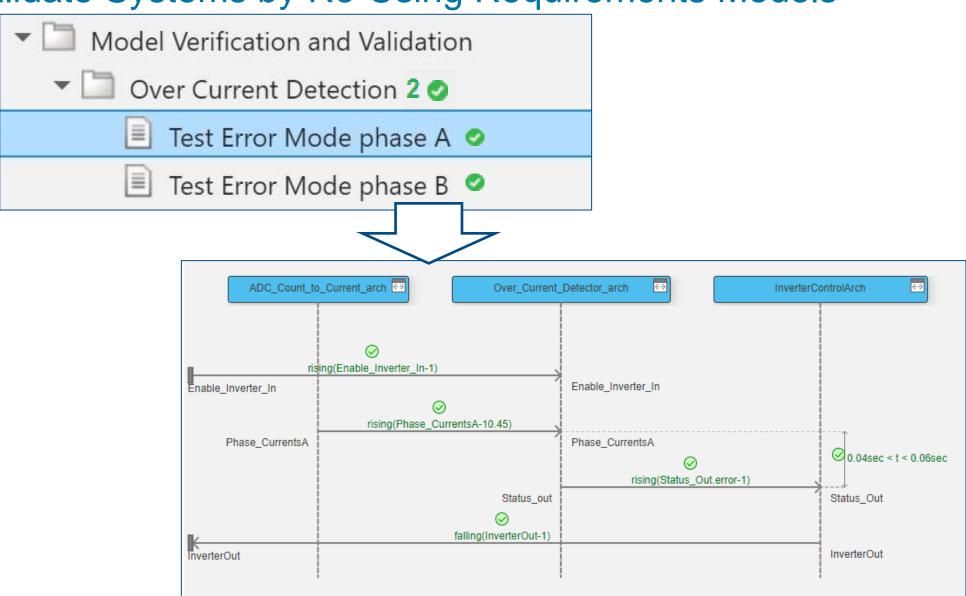

#### Validate Systems by Re-Using Requirements Models

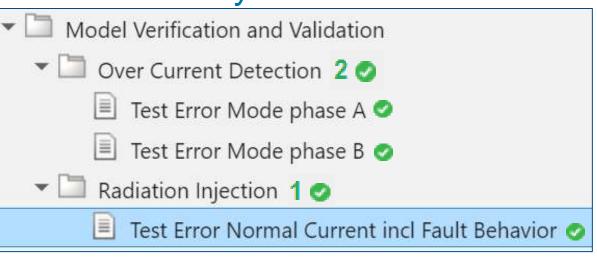

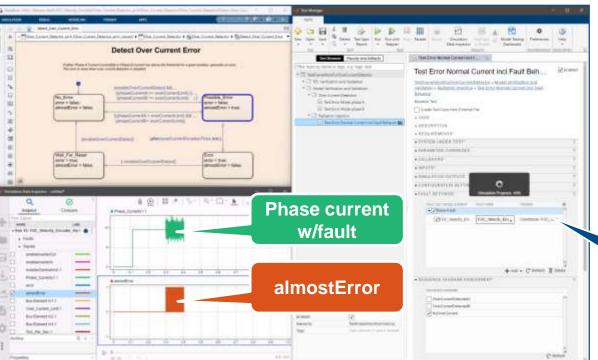

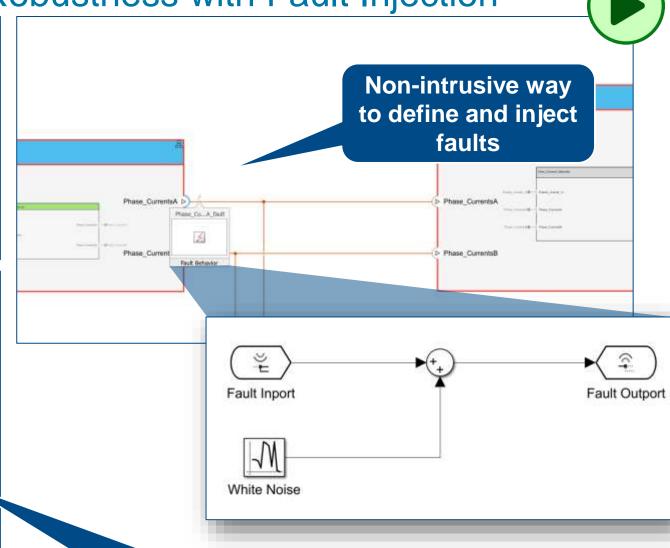

Validate System Behavior and Robustness with Fault Injection

Analyze impact of faults using simulation

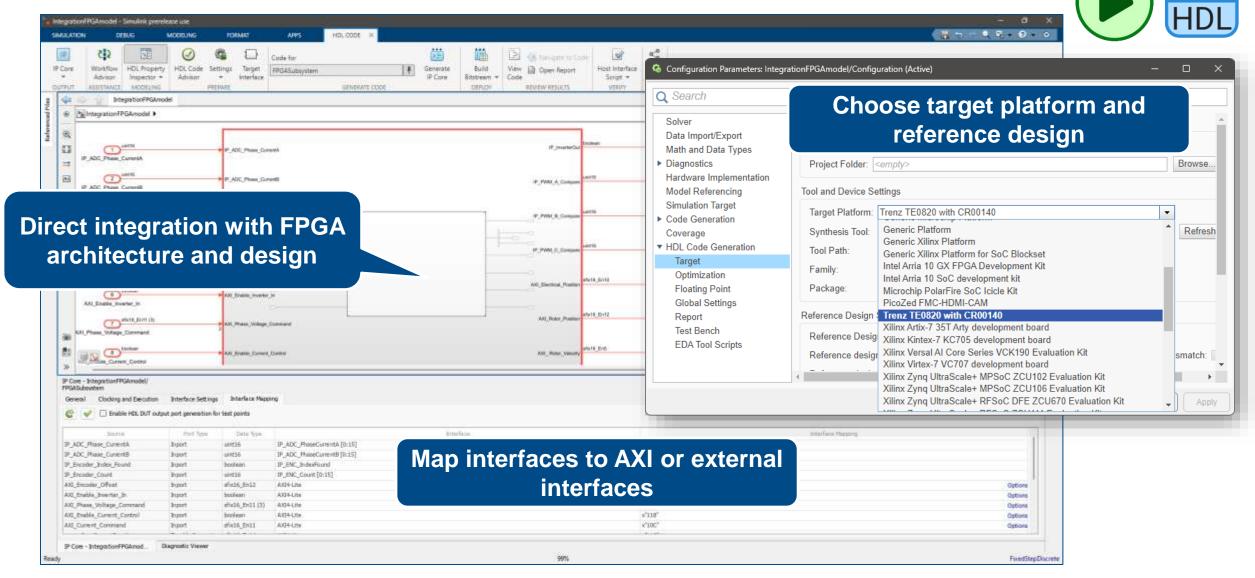

#### Generate HDL code from System Architecture incl Detailed Models

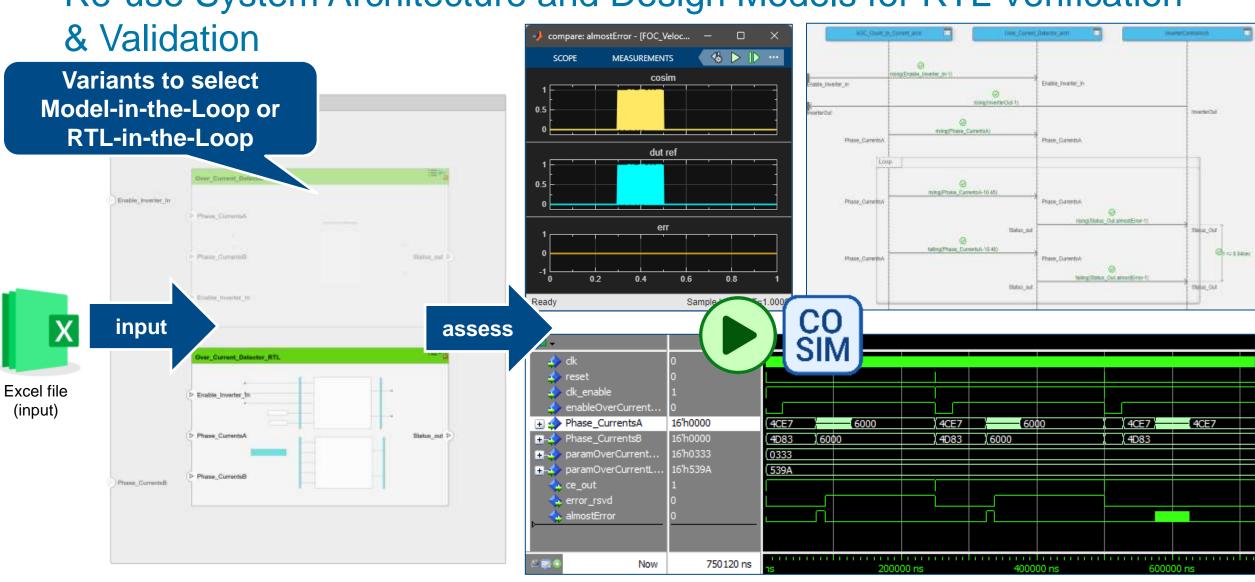

Re-use System Architecture and Design Models for RTL Verification

### Integration with other IPs or Software Components

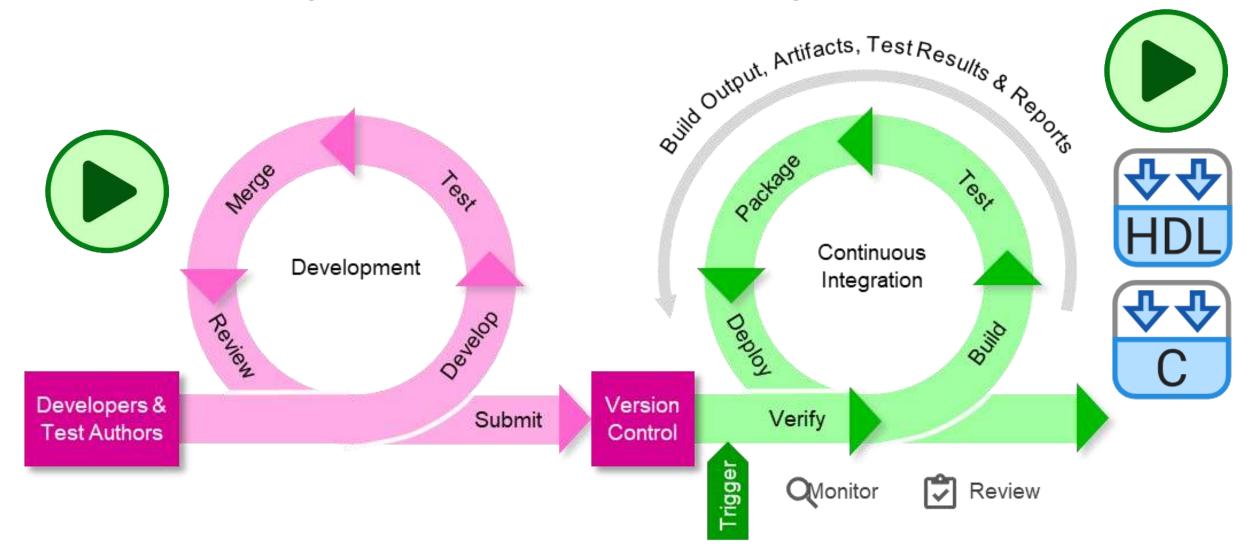

#### Continuous Integration for Model-Based Design

#### Concluding remark

Architecture

Design

Simulation

The main FPGA challenge lies in architecture, often informal and overlooked. A tool is needed to generate RTL directly from the architecture + design in a single model, making it the single source of truth.

- Adam Taylor, Adiuvo

Simulated