# AMD

# AMD XQR Versal<sup>™</sup> Adaptive SoCs Enable Next-Generation Signal Processing and AI in Space

Ken O'Neill Space Systems Architect koneill@amd.com Paul Lynch Customer Quality Engineer paul.lynch@amd.com

SEFUW March 2025

#### Agenda

- XQR Kintex<sup>™</sup> UltraScale<sup>™</sup> and Virtex<sup>™</sup>5-QVFPGA update

- XQR Versal<sup>™</sup> Adaptive SoC introduction and overview

- Architectural features

- Product portfolio

- Qualification and screening

- Power and thermal considerations

- Radiation

- Partners and ecosystem

- Reference designs

- Q&A

# **AMD** in Aerospace & Defense Applications

30 Years Heritage

#### Space

- Space-grade Portfolio

- SEU Mitigation

- Payload Processing

- Y, V, and B flow, QML

- On-orbit Reconfiguration

#### **Security Solutions**

- Anti-Tamper (AT)

- Information Assurance (IA)

- HW / SW Assurance

#### Intelligence, Surveillance & Reconnaissance (ISR)

- Signal Processing

- Multi-channel SAR

- Connectivity

**Avionics**

DO-254 and DO-178

Certifiable Solutions

Advanced Tool Flows

SEU Mitigation

STAP Processing

Covering Ground, Air, and **Space Applications**

**Extending with Machine Learning**

#### **Communications**

- Signal Processing

- Low Power Solutions

- Waveform IP & Analysis

- LTE UE with P2P

# **Exciting Recent Activity!**

**Strong Adoption & Heritage**

Artemis / Orion NASA November 2022 Virtex-5 (SIRF) FPGAs On-Board Computing JUICE European Space Agency June 2023 Virtex-4 Series FPGAs Science Instrument Chemical Composition of Jupiter Icy Moons Heinrich Hertz DLR German Space Agency July 2023 Virtex-5 (SIRF) FPGAs Reconfigurable On-Board Processing

Chandrayaan 3 ISRO Indian Space Agency July 2023 Virtex-5 (SIRF) and Virtex-4 Series FPGAs Science Instruments PWSA Tranche 0 SDA Feb 2024 Kintex<sup>™</sup> Ultrascale<sup>™</sup> FPGAs Imaging Low Earth Orbit Constellations Commercial and USG Launches in 2023 and 2024 Versal<sup>™</sup> Adaptive SoCs Communications

# XQR Kintex<sup>™</sup> Ultrascale<sup>™</sup> FPGA and XQR Virtex-5QV FPGA Update

## XQR Kintex<sup>™</sup> UltraScale<sup>™</sup> and Virtex-5QV Product Table

| Resources                           |                              | XQR4V        | ,                  |         | XQR5V                     | XQRKU060                  |

|-------------------------------------|------------------------------|--------------|--------------------|---------|---------------------------|---------------------------|

| Logic Cells                         | 55,296                       | 56,880       | 142,128            | 200,448 | 131,072                   | 725,550                   |

| CLB Flip-Flops                      | 49,152                       | 50,560       | 126,336            | 178,176 | 81,920                    | 663,360                   |

| Distributed RAM (Kbits)             | 384                          | 395          | 987                | 1,392   | 1,580                     | 9,180                     |

| Total Block RAM (Kbits)             | 5,760                        | 4,176        | 9,936              | 6,048   | 10,728                    | 38Mb                      |

| Max Distributed RAM (Kb)            |                              |              |                    |         |                           | 9,180                     |

| Block RAM/FIFO with ECC (36Kb each) |                              |              |                    |         |                           | 1,080                     |

| Digital Clock Manager (DCM)         | 8                            | 12           | 20                 | 12      | 12                        |                           |

| Phase Lock Loop (PLL)               |                              |              |                    |         | 6                         | 12 CMT (1MMCM, 2 PLLs)    |

| DSP Slices                          | 512                          | 128          | 192                | 96      | 320                       | 2,760                     |

| System Monitor                      |                              |              |                    |         |                           | 1                         |

| PCIe Gen1/2/3                       |                              |              |                    |         |                           | 3                         |

| Processors                          |                              |              | Hz PPC405<br>Cores |         |                           | MicroBlaze (IP)           |

| 10/100/1000 EMACs                   |                              | 4            | 4                  |         | 6                         |                           |

| Multi-Gigabit Transceivers (MGT)    |                              |              |                    |         | 18 @4.25Gbps              | 32 @12.5 Gbps             |

| TID (krad)                          | 300                          | 300          | 300                | 300     | 1,000                     | 120                       |

| SEL Immunity (LETs) MeV-cm2/mg      | >125                         | >125         | >125               | >125    | >125                      | 80                        |

|                                     |                              |              |                    |         | Radiation Hardened By     |                           |

|                                     |                              | iation Toler | ant (RT)           |         | Design (RHBD)             | Radiation Tolerant (RT)   |

|                                     | V-Flow (QML-V<br>Equivalent) |              |                    |         | B-Flow (QML-Q Equivalent) | B-Flow (QML-Q Equivalent) |

|                                     |                              |              |                    |         | V-Flow (QML-V Equivalent) | Y-Flow (QML-Y Equivalent) |

| Package Size (mm)                   | 35 x 35 mm                   |              | 40 x 40 mm         |         | 45 x 45 mm                | 40 x 40 mm                |

| Pin Counts                          | 1140                         | 1144         | 1509               |         | 1752                      | 1509                      |

| Max. IO Count                       | 640                          | 576          | 768                | 960     | 840                       | 620                       |

|                                     |                              | Last Time    | Buy                |         | SHIPPING                  | SHIPPING                  |

## XQR Kintex<sup>™</sup> UltraScale<sup>™</sup> FPGA Qualification - Completed!

- The XQRKU060 qualification was completed on schedule

- 3 qualification lots tested and meet requirements per MIL-PRF-38535

- Qualification report available

- Group A (TM5005)

- Group B (MIL-STD-883)

- Group C (TM1005 2000 Hours) + Group C (TM1005 Aug. 2021 Surpassed 10K hours for New Product Introduction)

- HTS (TM 1008); HAST (JESD22-A110); Temp Cycle (TM1010 Cond C)

- Group D (Sub Groups 1,3,4,5)

- Group E (TM 1019, Sub Group2)

- QML-Y Certification Plans for XQRKU060

- AMD pursuing certification with DLA, NASA/JPL and Aerospace Corporation

- Additional Reliability Monitors

- Board Level Reliability completed

- 1000 Temp cycles (-55°C to 100°C, 10°C/min, 15min dwell time) PASSED

XQRKU060 Xilinx Class B, Class Y **PASSED** Qualification, Shipments since Sept 2020 XQR Versal<sup>™</sup> Adaptive SoCs for Space Applications

## **Space Industry Market Challenges & Requirements**

- Downlink Bandwidth is limited

- Fast time to market

- Platform Concept for reuse on multiple missions

- Low Latency and High Bandwidth

- Seamless and reliable connectivity for broadband communications

Machine Learning in orbit

- Need for capability to process on board a satellite vs ground station

- Reduce Development Time to launch (2-3 years vs. 5-6 years)

- Process hundreds of Gbps data streams in real time

- Flexible System Architecture

- Change algorithms "on the fly"

- Reliable components for long mission life, extreme environments

## Example Applications for AMD Versal<sup>™</sup> Adaptive SoCs

Communications Constellations

- Broadband

Internet

- Direct-to-Device

- Inter-satellite Crosslinks

Remote Sensing Payloads

- Hyperspectral Cameras

- Synthetic Aperture Radar

- Scientific Instruments

Navigation and Guidance

- GPS / GNSS

- Entry/Descent/Landing

- Autonomous Navigation

- Avionics

Signal Processing, HW/SW Reconfigurable, Robust Package, Space Grade Tested, On Orbit Flexibility

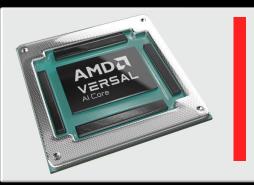

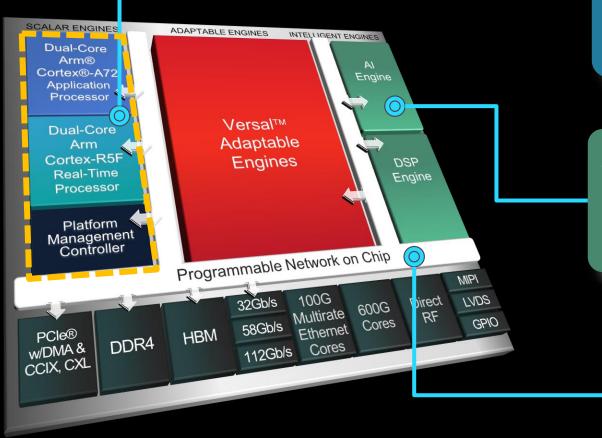

#### XQR Versal<sup>™</sup> Adaptive SoC

| VERSAL |  |

|--------|--|

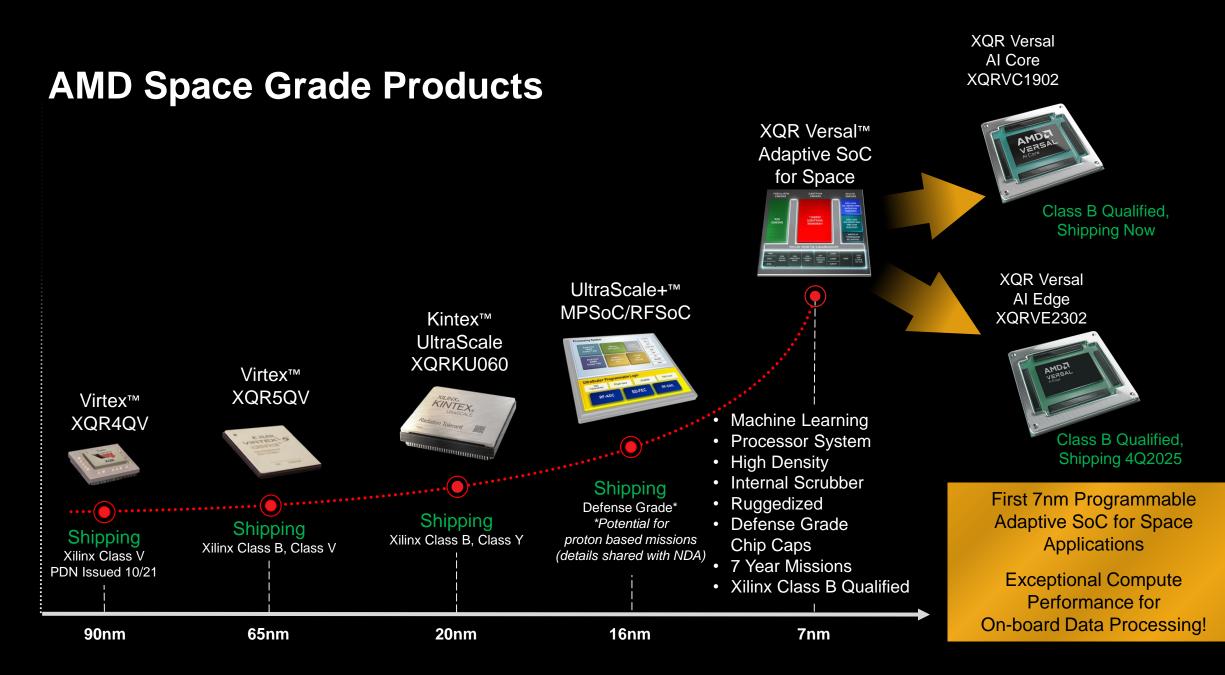

#### First 7nm Adaptive SoC for Space Applications

- AI Core and AI Edge family members with Scalar, Intelligent and Adaptable Engines (ARM<sup>®</sup> CPUs, AI Engines & Prog. Logic)

- Innovative silicon design for SEU mitigation (> 50 patents)

- True on-orbit reconfiguration with unlimited programming cycles

#### Ruggedized Organic BGA

- AI Core 45mm x 45mm, AI Edge 23mm x 23mm

- Lidless with stiffener ring for added thermal mitigation capabilities

- Footprint compatible with commercial packages

#### Production Space Test Flow

- Qualified and screened to MIL-PRF-38535 Class B, modified for organic packages

- Up to 7-year mission duration today with Class B

- Evaluating package enhancements for 15-year missions and class Y qualification

## **Novel Features for Space in Versal<sup>™</sup> Adaptive SoCs**

#### **Processor System**

- Dual A72 application processor

- Dual R5F real-time processor with lock-step mode

- Two triple-redundant hardwired MicroBlaze<sup>™</sup> processors host XilSEM configuration-memory SEU mitigation

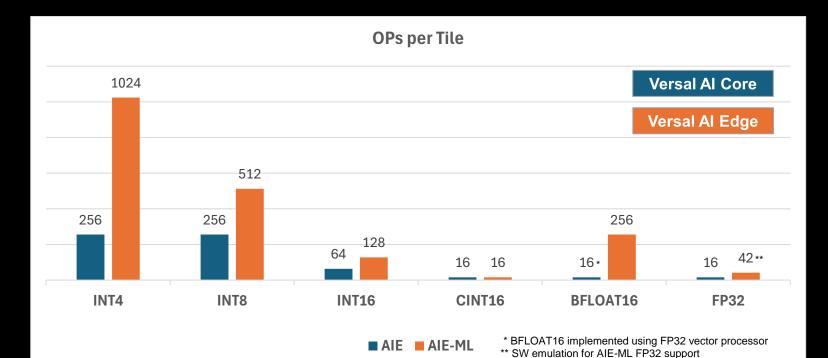

#### Al Engines

- SIMD vector processing

- Efficient complex matrix multiplication for RF processing

- Broad data-type support for AI inferencing

#### **Network on Chip**

- High bandwidth interconnect

- Reduces routing congestion

- Improves utilization

XQR Versal<sup>™</sup> Adaptive SoC Product Portfolio

#### **XQR Versal<sup>™</sup> Adaptive SoC for Space Product Table**

|                                      |                                      | XQRVC1902-1MSBVSRA2197 (AI Core)                                                                  | XQRVE2302-1MSBSSRA784 (AI Edge)       |  |

|--------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------|--|

|                                      | AI Engine Tiles                      | 400 (AIE)                                                                                         | 34 (AIE-ML)                           |  |

| Intelligent Engines                  | Al Engine Data Memory (Mb)           | 100                                                                                               | 17                                    |  |

| intenigent Engines                   | AI-ML Shared Memory (Mb)             | -                                                                                                 | 68                                    |  |

|                                      | DSP Engines                          | 1,968                                                                                             | 464                                   |  |

|                                      | System Logic Cells (K)               | 1,968                                                                                             | 329                                   |  |

| Adaptable Engines                    | 6-Input LUTs                         | 899,840                                                                                           | 150,272                               |  |

| Adaptable Eligilies                  | NoC Master/NoC Slave Ports           | 28                                                                                                | 5                                     |  |

|                                      | Distributed RAM (Mb)                 | 27                                                                                                | 4.6                                   |  |

|                                      | Total Block RAM (Mb)                 | 34                                                                                                | 5.4                                   |  |

|                                      | UltraRAM (Mb)                        | 130                                                                                               | 43.6                                  |  |

|                                      | Accelerator RAM (Mb)                 | -                                                                                                 | 32                                    |  |

| Memory                               | Total PL Memory (Mb)                 | 191                                                                                               | 86                                    |  |

|                                      | DDR Memory Controllers               | 4                                                                                                 | 1                                     |  |

|                                      | DDR Bus Width                        | 256                                                                                               | 64                                    |  |

|                                      | Application Processing Unit          | Dual-core Arm <sup>®</sup> Cortex <sup>®</sup> -A72, 48KB/32KB L1 Cache w/ECC 1 MB L2 Cache w/ECC |                                       |  |

| Scalar Engines                       | Real-time Processing Unit            | Dual-core Arm Cortex-R5F, 32KB/32KB L1 Cache, and 256KB TCM w/ECC                                 |                                       |  |

|                                      | Memory                               | 256KB On-Chip Memory w/ECC                                                                        |                                       |  |

|                                      | Connectivity                         | Ethernet (x2); UART (x2); CAN-FD                                                                  | (x2) USB 2.0 (x1); SPI (x2); I2C (x2) |  |

| Serial Transceivers                  | GTx Transceivers                     | 44 GTY (26.5625 Gb/s)                                                                             | 8 GTYP (26.5625 Gb/s)                 |  |

|                                      | CCIX & PCIe <sup>®</sup> w/DMA (CPM) | 1 x Gen4x8, CCIX                                                                                  | -                                     |  |

| Integrated Protocol IP               | PCI Express                          | 4 x Gen4x8                                                                                        | 1 x Gen4x8                            |  |

|                                      | Multirate Ethernet MAC               | 4                                                                                                 | 1                                     |  |

|                                      | Platform Management Controller       | Boot, Security, Safety, Monitoring, High-Speed Debug, SEU Mitigation (XilSEM)                     |                                       |  |

| Package                              | Ruggedized Organic BGA               | VSRA2197, 45mm x 45mm, 0.92mm pitch                                                               | SSRA784, 23mm x 23mm, 0.8mm pitch     |  |

| I/O                                  |                                      | 648 XPIO, 44 HDIO, 78 MIO, 44 GTY                                                                 | 216 XPIO, 22 HDIO, 78 MIO, 8 GTYP     |  |

| Radiation Single Event Effects (SEE) | Proton and Heavy-Ion SEE Testing     |                                                                                                   |                                       |  |

XQRVC1902 Class B qualification completed, product shipping now XQRVE2302 Class B qualification completed, product shipping 4Q2025

#### XQRVE2302 Versal<sup>™</sup> AI Edge Adaptive SoC

- Versal AI Edge adaptive SoC XQRVE2302 now qualified to B flow

- Significantly lower power consumption than XQRVC1902

- Significantly less board space than XQRVC1902

- Second generation AI engines ("AIE-ML") have increased throughput, optimized for AI inferencing

- Qualification completed, product shipping 4Q2025

XQR Versal<sup>™</sup> Adaptive SoC Packaging, Qualification and Screening

#### **Product Grade Comparison: UltraScale Architecture & Newer**

| Product-Grade    | Designation                                                                                                                                                                                            | Temp-Grade                                                                                  | Temp Range (Tj)                                                                                               | Major Differences & Notes                                                                                                                                                                                                                       | Key Work Elements                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Commercial-Grade | XC                                                                                                                                                                                                     | Extended-Temp                                                                               | E: 0 to +100C                                                                                                 | ROHS (internally and BGA)                                                                                                                                                                                                                       | • Pass process and device qual                                                                                                                                                                            |

| Commercial-Grade | λŪ                                                                                                                                                                                                     | Industrial-Temp                                                                             | I: -40 to +100C                                                                                               | <ul> <li>"XQ-Lite" avail. w/ Sn/Pb BGA (only<br/>avail. in I-temp UltraScale+ &amp; Versal)</li> </ul>                                                                                                                                          | <ul> <li>Base process and device qual</li> </ul>                                                                                                                                                          |

| Automotive-Grade |                                                                                                                                                                                                        | Industrial-Temp                                                                             | I: -40 to +100C                                                                                               | <ul><li>ROHS</li><li>AEC-Q100 Qualification</li></ul>                                                                                                                                                                                           | Si Qualification Testing                                                                                                                                                                                  |

|                  | ХА                                                                                                                                                                                                     | Q: -40 to +125C                                                                             | <ul> <li>Full Mask Set, BOM + Site Control</li> <li>PPAP Documentation</li> <li>Up to Q temp range</li> </ul> | <ul> <li>Si High Temperature Characterization</li> <li>High Temp Test Programs</li> </ul>                                                                                                                                                       |                                                                                                                                                                                                           |

|                  |                                                                                                                                                                                                        | Industrial-Temp                                                                             | I: -40 to +100C                                                                                               | <ul> <li>Ruggedized Packages</li> <li>Full Mitigation of Tin Whiskering</li> <li>Sn/Pb BGA</li> <li>MIL-STD-883 Subset (Group D)</li> </ul>                                                                                                     | <ul> <li>Si Characterization</li> <li>Package Design</li> <li>Package Qualification</li> </ul>                                                                                                            |

| Defense-Grade    | XQ<br>Military-Temp<br>M: -55 to +125C<br>· MIL-STD-883 Subset (Group D)<br>· Fully Tested at Temperature Extremes<br>· Mask set Control<br>· Anti-tamper Features<br>· Extended Lifetime availability | <ul> <li>Test Programs</li> <li>Q &amp; M Speed Files</li> <li>IA / AT Evaluated</li> </ul> |                                                                                                               |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                           |

| Space-Grade      | XQR                                                                                                                                                                                                    | Military-Temp                                                                               | M: -55 to +125C                                                                                               | <ul> <li>Includes all XQ features plus:</li> <li>Radiation Test Reports</li> <li>Ceramic Packaging (UltraScale)</li> <li>Burn-in, Temp &amp; Humidity qualification</li> <li>Groups A-E Qualification</li> <li>B or Y Flow Screening</li> </ul> | <ul> <li>Includes all XQ features plus:</li> <li>Radiation Testing</li> <li>Additional Si Screening</li> <li>Additional Group Testing</li> <li>Additional Test Programs</li> <li>M Speed Files</li> </ul> |

#### AMD XQR Construction Comparison (Ceramic vs. Organic)

| Feature             | Attribute                         | XQRKU060-CNA1509          | XQRVC1902-VSRA2197             |  |

|---------------------|-----------------------------------|---------------------------|--------------------------------|--|

| Qualification Level | Class                             | B and Y                   | В                              |  |

|                     | Package Type                      | Ceramic Column Grid Array | Organic Ball Grid Array        |  |

|                     | Body Size                         | 40x40 mm sq.              | 45x45mm                        |  |

| Package             | Height                            | 8.53 mm                   | 3.8mm                          |  |

| ruckage             | Pitch                             | 1.0 mm                    | 0.92mm                         |  |

|                     | Array                             | 39x39                     | 47x47                          |  |

|                     | Corner Depopulation               | :                         | 3                              |  |

|                     | Supplier                          | SF                        |                                |  |

| C4 Bump             | C4 Material                       | Eutectic, 63Sn37Pb        | Copper pillar with SnAg solder |  |

|                     | Pitch                             | 180 um                    | 130um                          |  |

|                     | Material                          | Ceramic (Alumina)         | Organic                        |  |

|                     | Thickness                         | 4.35 mm                   | 1.45mm                         |  |

|                     | Substrate Metal Layers            | 37 layers                 | 16 layers                      |  |

| Substrate           | I/O, Vcc, Vss Trace Metallization | Tungsten (W)              | Copper                         |  |

|                     | Via Metallization                 | Molybdenum (Mo)           | Copper                         |  |

|                     | C4 Pads                           | E-Less Ni/Au              | Sn/Cu SOP                      |  |

|                     | Substrate LGA Pads                | E-Less Ni/Au              | SAC305 SOP                     |  |

|                     | Supplier                          | Kyocera                   | SPIL                           |  |

|                     | Chip Capacitors                   | Mil screened              | Commercial                     |  |

| Assembly            | Heatspreader Design               | 4 corner                  | Stiffener                      |  |

| Assembly            | Heatspreader Material             | Ni plated AlSiC           | Stainless Steel                |  |

|                     | Underfill                         | Underfill B               |                                |  |

|                     | Thermal Interface Material (TIM)  | TIM A                     |                                |  |

| Column/BGA Ball     | Supplier                          | 6 Sigma                   | SPIL                           |  |

|                     | Material                          | 80Pb/20Sn                 | 63Sn/37Pb                      |  |

| COULTIN/DGA Dall    | Height                            | 2.20 mm                   | 0.5mm                          |  |

|                     | Diameter                          | 0.51 mm                   | 0.64mm                         |  |

- Organic substrate advantages

- Allows high speed performance

- Higher density routing reduces substrate layers – reliability benefits

- Lighter, thinner than ceramic substrates

- Easier handling than column grid arrays

- Aligned with future requirements

#### AMD Versal<sup>™</sup> XQR (Class B) Package Attributes

• Devices are similar except for the size

|                    | Item                       | Versal for Space 2.0 / Class B |              |  |

|--------------------|----------------------------|--------------------------------|--------------|--|

|                    | Device                     | XQRVC1902-                     | XQRVE2302-   |  |

|                    |                            | 1MSBVSRA2197                   | 1MSBSSRA784  |  |

|                    | Body Size                  | 45 x 45mm                      | 23 x 23mm    |  |

| line               | Die Size                   | 25.8 x 17.8mm                  | 12.8 x 9.3mm |  |

| Outline            | Overall Package Height     | 3.8mm                          | 3.62mm       |  |

| Ĵ                  | BGA Ball Pitch             | 0.92mm                         | 0.8mm        |  |

| ate                | Туре                       | Org                            | anic         |  |

| Substrate          | Thickness                  | 1.45mm                         | 1.37mm       |  |

| Sul                | Layers                     | 16                             | 14           |  |

|                    | Туре                       | Stiffener                      |              |  |

| Lid /<br>Stiffener | Material                   | Stainless Steel                |              |  |

| Lid ,<br>tiffen    | Thickness                  | 1.8mm                          |              |  |

| Ś                  | Adhesive                   | Silicone Adhesive              |              |  |

| de                 | Туре                       | Comm                           | ercial       |  |

| Chip Cap           | Termination (top)          | Leadfree w/ ep                 | poxy coating |  |

| Chi                | Termination (bottom)       | SnPb                           | N/A          |  |

| bD                 | Wafer FAB                  | TSMC/T                         | Faiwan       |  |

| Manufacturing      | Mask Set                   | Loc                            | ked          |  |

| actı               | Assembly Location          | SPIL/Taiwan                    |              |  |

| anuf               | Die/Substrate Connection   | Copper pillar w/SnAg solder    |              |  |

| Š                  | BGA Ball Material          | Eutectic                       |              |  |

| Other              | Moisture Sensitivity Level | MS                             | L - 4        |  |

| oth                | Screening Level            | Class B                        |              |  |

#### XQR Versal<sup>™</sup> Adaptive SoC Qualification & Screening

- AMD Class B qualification completed

- Derived from MIL-PRF-38535

- Groups A D

- Burn-in

- High-temp storage and operating life

- Temp cycling

- All devices are screened to AMD Class B for organic packages

- Derived from MIL-PRF-38535

- AMD exceeds test temperature requirements we do tri-temp electrical testing

- For complete qualification details & results, please contact AMD Customer Quality team

## Versal<sup>™</sup> Adaptive SoC Class B Qualification Summary

• AMD has successfully completed our Class B qualification for the Versal XQRVC1902 device

| Stress Test             | MIL-STD-883<br>JEDEC reference | Conditions                                                        | Duration /<br>Sample Size                                             | Results |

|-------------------------|--------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|---------|

| Prod. Burn-in           | TM 1015                        | Dynamic, Tj = 125°C Vccmax                                        | 160 hrs.                                                              | Passed  |

| Group A                 | TM 5005                        | Functional, AC and DC Parameters<br>Test at -55°C, 25°C and 125°C | Test at -55°C, 25°C and 125°C                                         | Passed  |

| Group B                 | Various JEDEC                  | Assembly Monitors                                                 | $\checkmark$                                                          | Passed  |

| Group C <sup>2</sup>    | TM 1005                        | Tj = 125°C, Vccmax                                                | 2 lots, 90 units total - 1000 hours<br>1 lot, 45 units – 10,000 hours | Passed  |

| HTS <sup>1</sup>        | TM 1008                        | Ta = 150°C                                                        | 1000 hours<br>3 lots, 75 units total                                  | Passed  |

| THB <sup>1</sup>        | JESD22-A101                    | 85°C / 85% RH, Vccmax                                             | 1000 hours<br>3 lots, 75 units total                                  | Passed  |

| Temp Cycle <sup>1</sup> | TM 1010                        | B: -55°C / 125°C                                                  | 1000 cycles<br>3 lots, 75 units total                                 | Passed  |

| Group D <sup>1</sup>    | TM 5005                        | Sub-Groups 1,3,4,5                                                | 3 lots, 15 units / subgroup                                           | Passed  |

(1) Units submitted to MSL-4 preconditioning prior to stressing

## AMD Qualification for Versal<sup>™</sup> XQRVE2302-SSRA784 (Class B)

• AMD has successfully completed our Class B qualification for the Versal XQRVE2302 device

| Stress Test             | MIL-STD-883<br>JEDEC reference               | Conditions                                                        | Test Vehicle /<br>Sample Size                                               | Results |

|-------------------------|----------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|

| Prod. Burn-in           | TM 1015 Dynamic, Tj = 125°C Vccmax. 160 hrs. |                                                                   | All units                                                                   | Passed  |

| Group A                 | TM 5005                                      | Functional, AC and DC Parameters<br>Test at -55°C, 25°C and 125°C | XQRVC1902-VSRA2197: 3 lots<br>XQRVE2302-SSRA784: 1 lot                      | Passed  |

| Group B                 | Various JEDEC                                | Assembly Monitors                                                 | XQRVC1902-VSRA2197: 3 lots<br>XQRVE2302-SSRA784: 1 lot                      | Passed  |

| Group C                 | TM 1005                                      | Tj = 125°C, Vccmax, 1000 hrs.                                     | XQRVC1902-VSRA2197: 3 lots, 135 units<br>XQRVE2302-SSRA784: 1 lot, 45 units | Passed  |

| HTS <sup>1</sup>        | TM 1008                                      | Ta = 150°C, 1000 hrs.                                             | XQRVC1902-VSRA2197: 3 lots, 75 units                                        | Passed  |

| THB <sup>1</sup>        | JESD22-A101                                  | 85°C / 85% RH, Vccmax, 1000 hrs.                                  | XQRVC1902-VSRA2197: 3 lots, 75 units                                        | Passed  |

| Temp Cycle <sup>1</sup> | TM 1010                                      | B: -55°C / 125°C, 1000 cycles                                     | XQRVC1902-VSRA2197: 3 lots, 75 units<br>XQRVE2302-SSRA784: 1 lot, 30 units  | Passed  |

| Group D <sup>1</sup>    | TM 5005                                      | Sub-Groups 1,3,4,5                                                | XQRVC1902-VSRA2197: 3 lots, 15 units<br>XQRVE2302-SSRA784: 1 lot, 15 units  | Passed  |

(1) Units submitted to MSL-4 preconditioning prior to stressing

In support of the technology qualification, the XQRVC1902 device has passed 10,000 hours of Group C stressing

## XQR Versal<sup>™</sup> Adaptive SoC Class B Screening Flow

- Screening flow modified to accommodate non-hermetic, organic substrate, flip chip, BGA packaging

- Derived from MIL-PRF-38535

- AMD exceeds the test requirements in pre burn-in electrical test

- Spec. is 25°C

- AMD tests at -55°C, 25°C & 125°C

- AMD adds bumping and serialization

- For mission duration up to 7 years

| Flow                                              | QML<br>"Class B"  | AMD Organic<br>"Class B" |

|---------------------------------------------------|-------------------|--------------------------|

| Wafer Sort                                        | V                 | V                        |

| Bumping                                           | N/A               | V                        |

| Assembly (per MIL-STD-883)                        | V                 | Commercial               |

| Bond Pull (Extended Pull Test)                    | N/A               | N/A                      |

| Die Shear (1unit/lot)                             | V                 | V                        |

| Die Visual Inspection                             | Cond B            | Commercial               |

| Serialization                                     | V                 | V                        |

| Temperature Cycling (cycles)                      | 10                | 10                       |

| Constant Acceleration                             | N/A for flip chip | N/A for flip chip        |

| PIND                                              | N/A               | N/A                      |

| Seal (Fine/Gross Leak Test)                       | N/A               | N/A                      |

| X-Ray and/or CSAM                                 | V                 | $\checkmark$             |

| Pre Burn-in Electrical Test                       | @25C              | @25C, 125C, -55C         |

| Dynamic Burn-in @125C                             | 160 hrs           | 160 hrs                  |

| Post Burn-in Test @25C with Read & Record         | N/A               | N/A                      |

| Static Burn-in (144 hours @125C)                  | N/A               | N/A                      |

| Group A Post Burn-in Test @25C with Read & Record | V                 | V                        |

| Group A Final Test @-55C with Read & Record       | V                 | $\checkmark$             |

| Group A Final Test @125C with Read & Record       | V                 | V                        |

| Column Attach                                     | V                 | N/A (BGA Pkg)            |

| 100% QA Electrical @25C                           | V                 | N/A                      |

| Visual Inspection                                 | V                 | $\checkmark$             |

| Group B Lot Specific                              | V                 | V                        |

| Group C Sample to 44k device hours                | Periodic          | Periodic                 |

| Group D                                           | Periodic          | Periodic                 |

| Group E Total Ionizing Dose                       | N/A               | N/A                      |

| DPA Sample/Ion Milling                            | N/A               | N/A                      |

Note: (1) BGA balls will be attached during assembly

## **Power and Thermal Considerations**

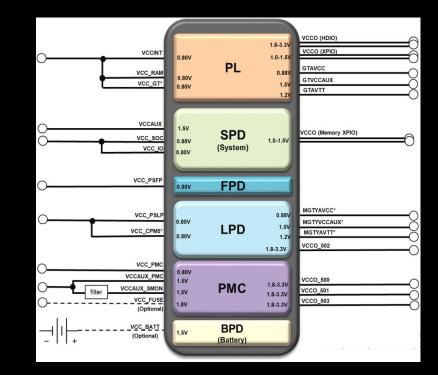

## **XQR Versal<sup>™</sup> Adaptive SoC Power**

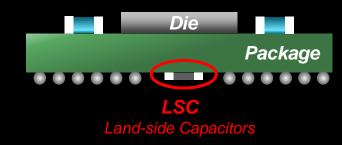

- Power Distribution Network (PDN)

- Land-side capacitors (LSC): reduced distance to die; reduced package induction

- Mix of substrate top-side, LSC and on-die caps helps mitigate noise across wide frequency range

- Xilinx Power Design Manager (PDM) available now

- Stand-alone Java-based power estimator

- Enhanced stability, user interface, IP wizards, XDC constraints

- Power Delivery

- Partnerships for optimized, reliable, radiation tolerant power delivery

- Monitoring, protections and flexible features to reduce BOM count and improve performance

- Power and Thermal Dissipation go hand-in-hand

- Greater power density on Versal demands proper thermal mitigation

- Must do complete thermal simulation

- Siemens <u>Simcenter Flowtherm</u>

- Ansys <u>lcePak</u>

- XQR Versal thermal models will be available on Space Lounge

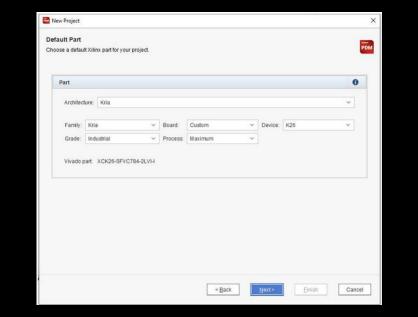

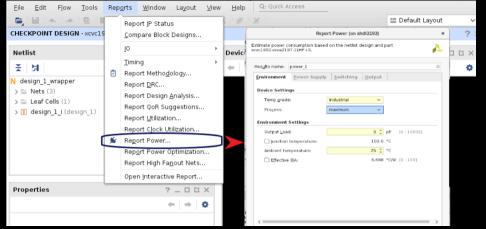

#### **Power Design Manager Supports Two Major Design Flows**

- AMD Power Design Manager (PDM) available now

- Stand-alone Java-based power estimator

- Enhanced stability, user interface, IP wizards, XDC constraints

- Manual Estimation Flow

- Completely manual entries for power estimation

- Start with device selection, followed by thermal specifications and configuring the PMC (platform management controller)

- Import Flow

- You can import the XPE file generated from Vivado<sup>®</sup> power into PDM while creating a new project

- You can also use existing estimations from XPE and import into PDM for Versal<sup>™</sup> and Kria<sup>™</sup> devices

#### **Addressing Thermal Design Challenges**

- AMD highly recommends thermal simulation via Computational Fluid Dynamic software

- AMD has improved thermal simulation models

- Predict the thermal performance of the device

- Quickly iterate through different heat sinks, board placement, airflow directions and countless other scenarios

- Swiftly and confidently arrive at optimal thermal solution

- Thermal design decisions must take place prior to board layout

- Choosing a material with high thermal conductive properties will ensure:

- Complete coverage (>95%)

- High reliability

- AMD is improving thermal performance by:

- Refining and improving current processes

- Introducing and embracing new packaging designs

- Low power screened XQRVC1902

- ▶ 20% static power reduction in Icc

- Ready for quote now using SCD append "5355" to ordering code

XQR Versal<sup>™</sup> Adaptive SoC Radiation Effects

## Versal<sup>™</sup> Adaptive SoC Radiation Effects Summary

|                | Protons (2 – 105 MeV)<br>Low Earth Orbit, 500 km, 20° inclination |                                                                                        |                                                                      | Heavy-ions (1 - 80 MeV·cm²/mg)<br>Geosynchronous Earth Orbit |                                                      |                                                                                                             | TID                  |

|----------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|

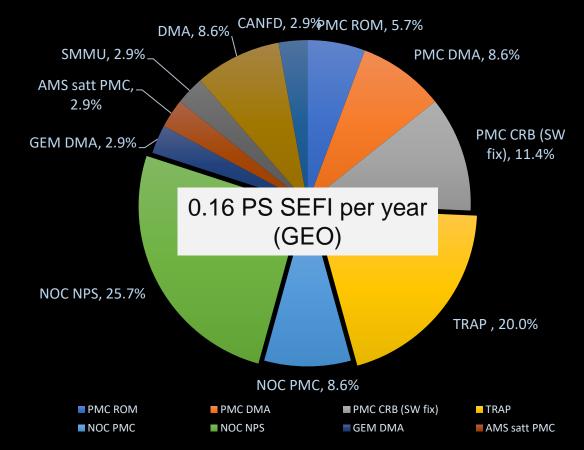

|                | CRAM SEU<br>(upset/bit/day)                                       | SEL                                                                                    | SEFI<br>(events/device/ <mark>year</mark> )                          | CRAM SEU<br>(upset/bit/day)                                  | SEL                                                  | SEFI<br>(events/device/ <mark>year</mark> )                                                                 | (gamma)              |

| Observed Rates | 3.5x10 <sup>-9</sup>                                              | <b>ZERO</b><br>events<br>observed                                                      | PS: <b>1.3</b><br>XilSEM: <b>ZERO</b><br>AIE: <b>1.5</b><br>GT: 2025 | 6.5x10 <sup>-12</sup>                                        | <b>ZERO</b><br>events<br>observed                    | PS: <b>0.16</b> and<br>XilSEM: <b>4.9x10<sup>-3</sup></b><br>AIE: 2025<br>GT Quad: <b>1x10<sup>-3</sup></b> | PASS 120<br>KRad(Si) |

| Comments       |                                                                   | Proton energy: 64-400MeV<br>Environment: 1x10 <sup>12</sup> p/cm <sup>2</sup> at 125°C |                                                                      |                                                              | ergy: 1-80 MeV·cr<br>t: 1x10 <sup>7</sup> per ion/ci |                                                                                                             | <18 Krad/min         |

Estimates based on CREME96 AP8-Max; 500km and GEO models

- DUTs: Versal 7nm VC1902, 20 parts from 5 wafer lots to account for lot-to-lot variation

- ZERO SEL events in maximum V<sub>CC</sub> and junction temperature conditions at LET up to 80 MeV·cm<sup>2</sup>/mg

- ZERO uncorrectable Configuration RAM (CRAM) events in LEO and GEO

- Configuration RAM protected by EDAC and interleaving

- Robust XilSEM internal scrubber SEFI rate may eliminate need for on-board scrubber in space flight

- Reference AMD / Xilinx user guides UG643 and PG352 for XilSEM scrubbing operation and cycle time

- AMD has published Versal SEE results at SEE/MAPLD 2022, NSREC 2022, 2023 and 2024, RADECS 2022 and 2023

- Check <u>AMD / Xilinx Space Lounge</u> for new reports, links to conference papers and updated content

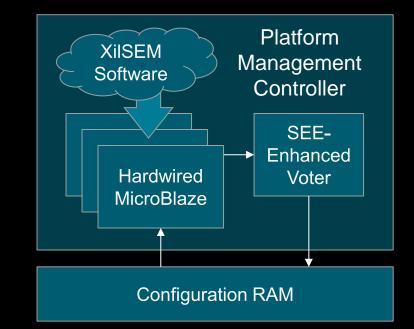

## **CRAM Soft Error Mitigation in XQR Versal<sup>™</sup> Adaptive SoC**

- XQR Versal uses a novel approach to mitigate SEUs in configuration RAM (CRAM)

- Previous generations of Xilinx FPGAs use SEM (Soft Error Manager) IP residing in the programmable logic fabric

- XiISEM uses the hardwired TMR MicroBlaze<sup>™</sup> processors in the Platform Management Controller (PMC) as a fault-tolerant platform to mitigate upsets in the configuration RAM

- Approx 30 times greater protection than previous techniques

|                                                           | Kintex <sup>™</sup> UltraScale <sup>™</sup><br>XQRKU060 | Versal<br>XQRVC1902            | Comments                                 |

|-----------------------------------------------------------|---------------------------------------------------------|--------------------------------|------------------------------------------|

| Configuration Memory (Mb)                                 | 193 Mb                                                  | 363 Mb                         | VC1902 has ~ 80% more<br>CRAM than KU060 |

| SEFI Rate per Device*<br>(with mitigation, GEO solar min) | 1 in 6 years<br>Using SEM                               | 1 in 200 years<br>Using XiISEM | 30X Improvement                          |

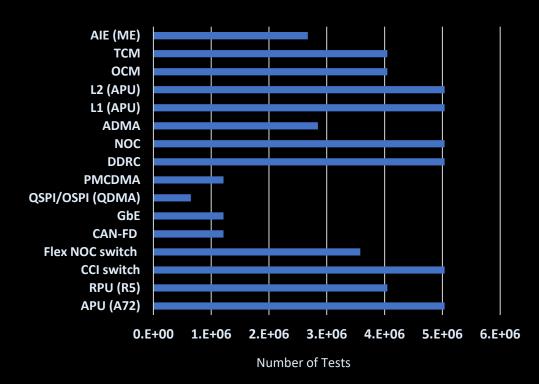

#### **PS test coverage and SEFI distribution**

- SVT code used during beam test was modified to generate the required information for coverage analysis

- > 10 million tests were generated under the beam

- R5/RPU, A72/APU and PMC (except security block) have been exercised > 4 million times

- Main SEFI signature: processor core hang (20%) or NOC NPS (26%)

- Block not listed means that Zero SEFI was observed

#### **AI/ML** Radiation Induced Datapath Error Signatures

#### Example: Misclassification (Accuracy Degradation)

Actual Image<sup>(1)</sup>

**Predicted Image**

Image: ILSVRC2012\_val\_00000383 Model: resnet-18 (SAT)

Golden Model Prediction (Top-1): komondor (sheep dog) (87.71%)

Actual Prediction (Top-1): window shade (61.65%)

Note: (1) Images are for illustration; actual images were cropped to 224x224 and mean-centered prior to model training and classification; (2) Probability/certainty can increase as well as decrease. For analysis purposes, absolute value error magnitude was considered.

#### Example: Probability Error

(Certainty Degradation)<sup>(2)</sup>

#### Correct Classification, Different Probability

Image: ILSVRC2012\_val\_00024059 Model: resnet-18 (SAT)

Golden Model Prediction (Top-1): water ouzel, dipper (bird) (95.76%)

Actual Prediction: water ouzel, dipper (74.71%)

Probability Error = -21.06%

Single events induced faults can impact prediction accuracy and certainty; In addition to SEFI, SEE analysis should account for Datapath signatures

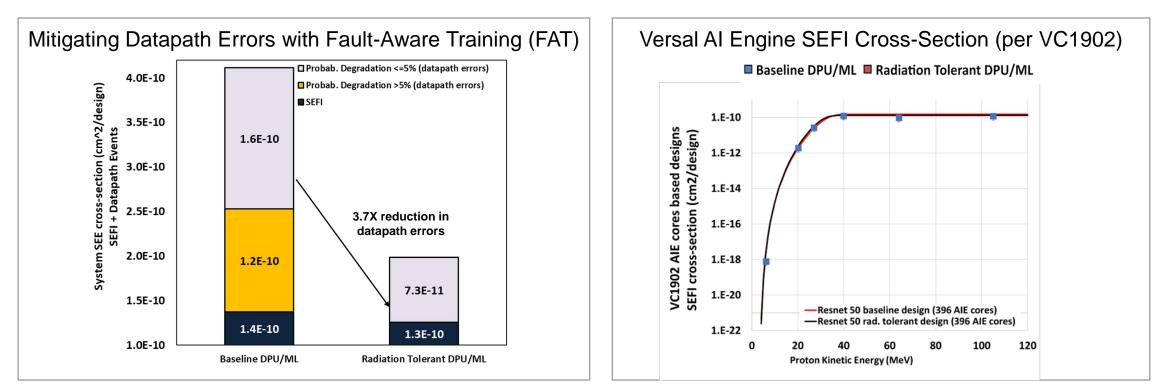

# Versal<sup>™</sup> Adaptive SoC AI/ML Proton Test Results

Radiation tolerant neural network response (vs. non-mitigated/baseline implementation), ResNet-50 network

- ~ 4X reduction in datapath SEU induced errors w/ rad. tolerant FAT platform (vs. baseline)

- > 5% probability degradation events are fully mitigated in the rad-tolerant design

- SEFI occurrence is <10% of the overall rad-tolerant platform single event cross-section</li>

- 1.5 event per ~ 400 cores per year (estimates using CREME96 AP8-Max; 500km, 52° inclination)

- Weibull parameters published in <u>Radiation Tolerant Versal AI Core Data Sheet (DS946)</u>

- P. Maillard et al., "Radiation-Tolerant Deep Learning Processor Unit (DPU)-Based Platform Using Xilinx 7-nm Versal Adaptive SoC AIE", IEEE NSREC 2024 AMD (AECG) Rad. Effects & RAS Team

# AMD Versal<sup>™</sup> Adaptive SoC Support Ecosystem

## Versal<sup>™</sup> Adaptive SoC Support Ecosystem

- Configuration Memory

- 3D-Plus

- Avalanche

- DDC

- Infineon

- Mercury Systems

- Development Platforms

- Alpha Data ADK-VA601 (XCVC1902)

- Alpha Data ADM-VB630 (XCVE2302, in development)

- iWave iW-RainboW-G57M<sup>®</sup> (XCVE2302)

- Trenz Electronic TE0950-01-EGBE11A (XCVE2302)

- Power Distribution

- Frontgrade (CAES)

- Infineon

- Renesas

- Texas Instruments

- Vicor

# AMD Versal<sup>™</sup> Reference Designs

#### Versal<sup>™</sup> Adaptive SoCs in Space – Conference Papers

IEEE Space Computing Conference, July 2023 XQRVC1902 Radar Space Time Adaptive Processing using AMD Versal<sup>™</sup> Adaptive SoCs

IEEE Space Computing Conference, July 2024 XQRVC1902 On-Orbit Anomaly Detection in Spacecraft Telemetry using RNNs in AMD Versal<sup>™</sup> Adaptive SoCs

IEEE Space Computing Conference, July 2024 XQRVE2302

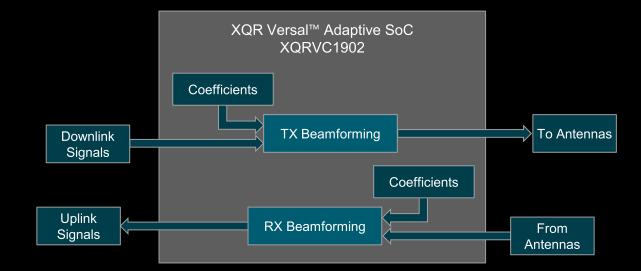

## **Example 1: RF Beamforming**

RF Beamforming in AMD XQR Versal<sup>™</sup> Adaptive SoCs using AI Engines

IEEE Space Computing Conference, July 2023 Image Credit: David Jessop, Licensed under Creative Commons Screenshot from <u>https://upload.wikimedia.org/wikipedia/commons/1/1e/Phasearray.gif</u>

- With 100 MHz bandwidth, 64 antennas, and 32 layers, downlink beamforming requires  $100,000,000 \times 64 \times 32 = 204,800,000,000$  CMACs per second, 204.8 GCMAC/s

- Implementation in AI Engines gives device utilization and time-to-implement advantage over DSP

- One AI Engine can compute 6,400,000,000 CMACs per second (at 80% runtime ratio) with 1 GHz clock

- 32 AI Engines achieve 204.8 GCMAC/s in each direction 64 AI Engines total, out of 400 available

- Modifications to design can be made in hours, not weeks

- For further information, consult AMD application note and reference design <u>XAPP1352</u>

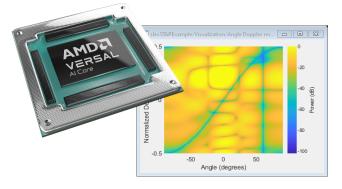

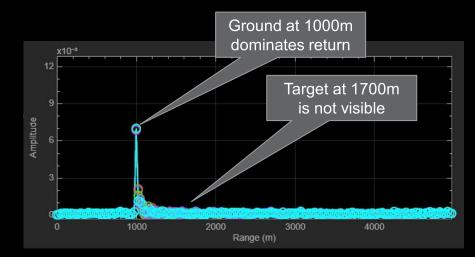

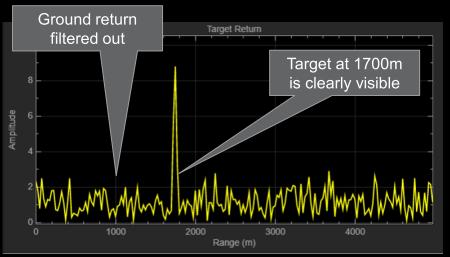

## **Example 2: STAP Radar Processing**

Radar Space Time Adaptive Processing using AMD Versal<sup>™</sup> Adaptive SoCs

ESA EDHPC, Oct 2023, and updated at IEEE Space Computing Conference, July 2024 Image Credit: Mathworks Inc.

| Resource                  | Amount Available in XQRVC1902 | Amount Used in<br>STAP Design | Percentage of<br>Resources |

|---------------------------|-------------------------------|-------------------------------|----------------------------|

| LUTs (6 Input)            | 899,840                       | 230,385                       | 26%                        |

| SRAM                      | 191 Mbit                      | 50.4 Mbit                     | 26%                        |

| DSP Engines               | 1,968                         | 1,136                         | 58%                        |

| AI Engines,<br>Clock Rate | 400                           | 78,<br>1.25 GHz               | 20%                        |

Reference design project files available direct from AMD

Both images credit: MathWorks Inc

https://www.mathworks.com/help/radar/ug/clutter-and-jammer-mitigationwith-stap.html?s\_tid=srchtitle\_site\_search\_2\_STAP

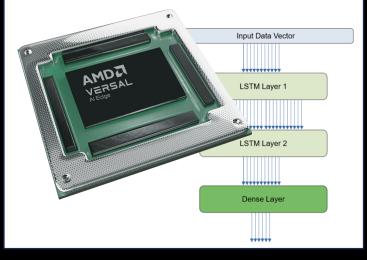

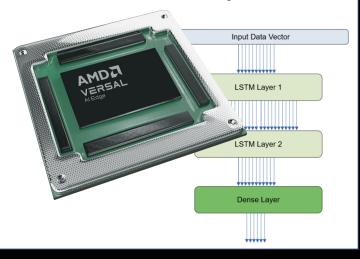

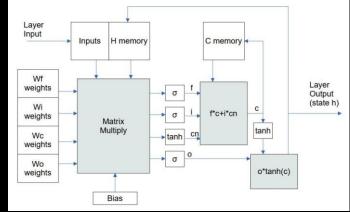

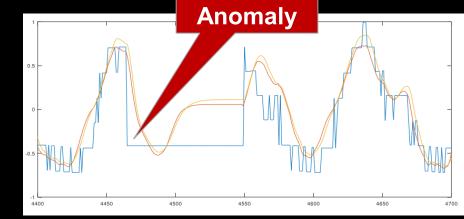

#### **Example 3: Real-time Telemetry Anomaly Detection**

On-Orbit Anomaly Detection in Spacecraft Telemetry using RNNs in AMD Versal<sup>™</sup> Adaptive SoCs

- Design uses AMD Versal AI Edge VE2302

- Real-time on-orbit anomaly detection for up to 80 channels of spacecraft telemetry

- Reference design project files available from AMD and <u>Alpha Data Parallel Systems</u>

| Resource      | Amount Available in XQRVE2302 | Amount Used in<br>Anomaly Detector | Percentage of<br>Resources |

|---------------|-------------------------------|------------------------------------|----------------------------|

| AIE-ML Tiles  | 34                            | 24                                 | 70%                        |

| AIE-ML Memory | 17 Mbit                       | 440 Kbit                           | 2.5%                       |

| Shared Memory | 68 Mbit                       | 54.7 Mbit                          | 80%                        |

# **Questions and Answers**

Ken O'Neill Space Systems Architect koneill@amd.com Paul Lynch Customer Quality Engineer paul.lynch@amd.com

Timelines, roadmaps, and/or product release dates shown in these slides are plans only and subject to change.

The information contained herein is for informational purposes only and is subject to changeout notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

©2025 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Xilinx, the Xilinx logo, Kintex, Versal, Virtex and UltraScale and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. ARM and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. Java is a registered trademark of Oracle and/or its affiliates. PCIe® is a registered trademark of PCI-SIG Corporation.