### AGENDA

- Context

- Requirements

- Developments

- Tests

- Results

# CONTEXT

1.2.2.2

### CONTEXT

European program

- EU Horizon 2020 program for research and innovation

- Developed by 3D PLUS in the frame of a research and innovation program

- Guaranteed supply chain fully manufactured in Europe

- Users' Cross validated by a consortium of Radiation Effects and European Space

Electronics experts

# CONTEXT

### 1 Consortium, 6 partners

# beyond gravity

# REQUIREMENTS

----

8 8 8 8

### **MNEMOSYNE**

#### The Memory Goddess

Mnemosyne, daughter of Ouranos and Gaia. She is the goddess of memory in Greek mythology. She embodies knowledge and the transmission of wisdom.

Mother of the nine Muses, through them, she becomes the source of inspiration for the arts and sciences. Without her, all knowledge would be doomed to oblivion.

### **MNEMOSYNE REQUIREMENTS**

More details

- Non volatile memory ASIC with SPI and EEPROM interfaces

- High Density

- Radiation Immune

- Applications:

- FPGA configuration bitstream storage

- Boot code storage for microcontrollers and micro processors

- Strengthen the reliability (temperature, data retention, life time) to reach space requirements.

- Identify and analyse the process & circuit radiation sensitivity and verify the memory cells SEU/SEL immunity on the STT-MRAM FDSOI process

- Mitigate the risks of TID which degrade the performance and lead to functional failure at component level

- Mitigate the risk of SET/SEFI leading to component level data loss or functional error

- Design the control logic and interface around the MRAM to adapt to space design requirements

# DEVELOPMENTS

BBB Bal

A14148

Technologies

- SEL immune chip

- Existing Rad Hard Digital library

- Mature, reliability proven and commercially available in Europe process

- 40% die scaling, and 70% power saving vs

28 nm

- STT-MRAM process provides a SEU immune

Memory cell

- Rad Hard design techniques on analog and power blocks, control logic and interfaces

- Stacking of multiple chips to achieve higher densities (up 8 dies for 1Gbits)

Analog design

# ເກາຍດ

- Hard macro PMU

- 1.8V to 0.8V LDO

- 0.8V RC oscillator

- Power up/down sequence control

- Trimming of IVREF & RC osc

Three phases

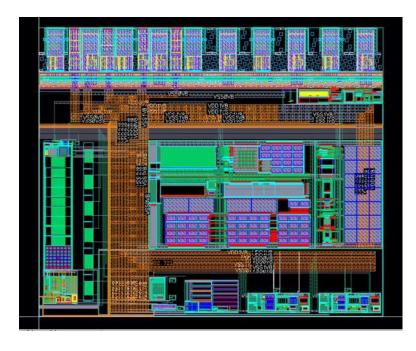

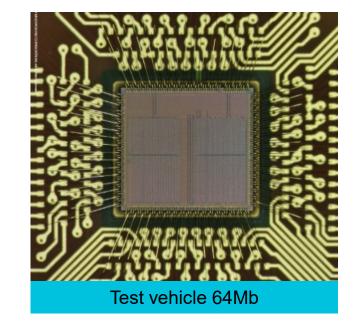

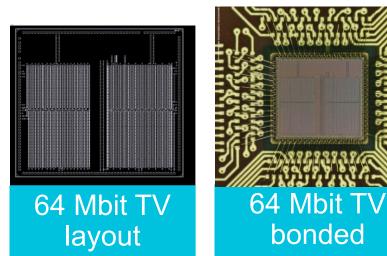

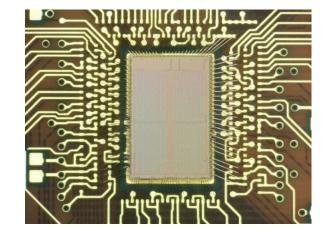

### **TV AND PROTYPE DESIGN**

#### Test Vehicle

- 186 pads

- All functionality can be bypassed

- Each module can be characterized individually

bonded

SPI 1.8v & 3.3v

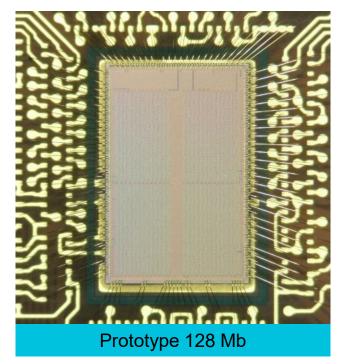

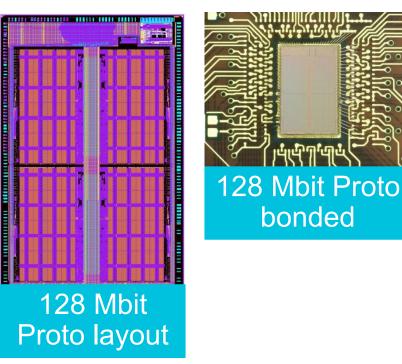

#### Prototype

- 225 pads

- PMU can be bypassed

- SPI 1.8v & 3.3v interfaces

- EEPROM 3.3v interface added

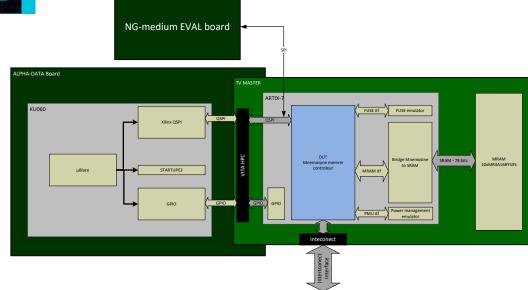

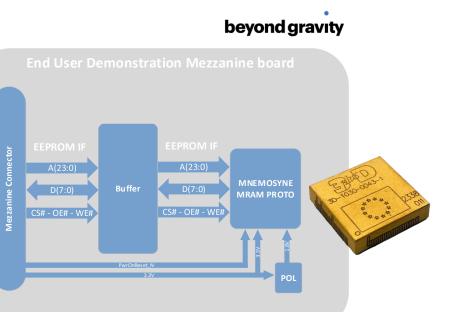

#### Braedboards

- Test boot of NG-MEDIUM

- Test boot of XQRKU060 FPGA

- Use XQRKU060 FPGA as hardware validation platform

# **TESTS**

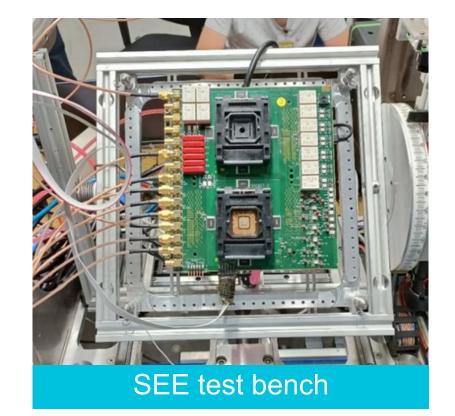

### TESTS Test Vehicle

- TID > 100 krad(Si)

- SEL/SEU LETh > 60 MeV.cm²/mg

- 1000h Life test passed with 30 measurements

- Overall Functional and Performance validated

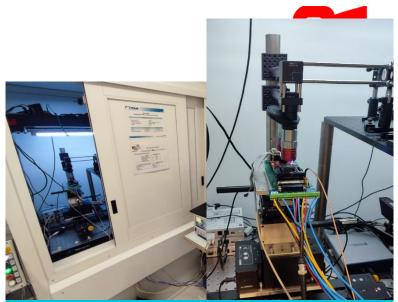

- Laser tests to pinpoint the location of the SEE sensitivity source

- Functional issue found during campaign, corrected for prototype run

- Radiation and reliability performances achieved

MNEMOSYNE TV at TRAD laser facility

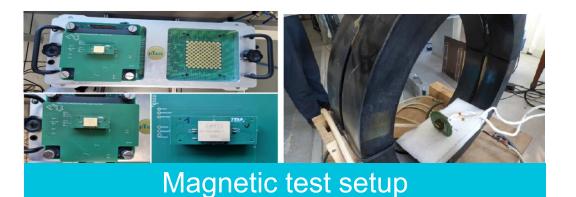

### **TESTS** TID and Magnetic tests

#### TID performed by TRAD using 60Co source at 310 rad/h (low dose rate)

o TID level > 100 krad(Si) has been validated

#### Magnetic Test

- Static Magnetic Field > 1000 Gauss

- Power Frequency Magnetic Field > 1000A/m

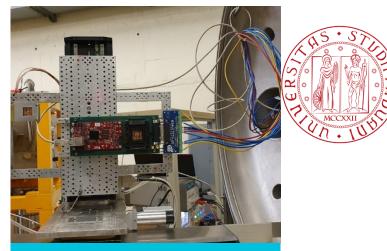

# Beam test to characterize the ASIC SEE response at LNL, Italy and UCL, Belgium SEL LETth > 60 MeV.cm²/mg SEU LETth > 60 MeV.cm²/mg

Latest SEE campaign (June 2024) at RADED, Finland

SEL LETth > 85 MeV.cm²/mg

SEFI LETth > 85 MeV.cm²/mg

SEU LETth > 85 MeV.cm²/mg

SET LETth > 85 MeV.cm²/mg

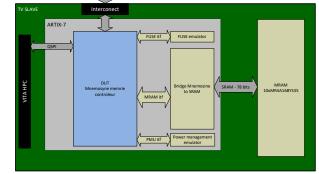

TESTS Functional tests

#### o NG MEDIUM : Successful operation

- NG ULTRA 300 : in progress, first analysis shown positive feasibility

- NG ULTRA : Flash boot time: miss match boot time performances.

The functional tests performed by Beyond Gravity show that the MNEMOSYNE memory ASIC works as expected with a processor using the EEPROM interface

I Public

# RESULTS

4.2.2.1

### **MNEMOSYNE ASIC**

### Radiation & Reliability Results

SEL sensitivity:

Immune to SEL up to at least LETth > 85 MeV.cm<sup>2</sup>/mg

SEFI sensitivity:

Immune to SEFI up to at least LETth > 85 MeV.cm<sup>2</sup>/mg

SEU sensitivity:

○ Immune to cell SEU up to at least LETth ≥ 85 MeV.cm<sup>2</sup>/mg

SET sensitivity:

- $\circ$  **EEPROM interface: immune to SET** up to at least

- LET ≥ 85 MeV.cm<sup>2</sup>.mg<sup>-1</sup>

- $\circ$  1.8V SPI interface: immune to SET up to at least

$LET \ge 85 \text{ MeV.cm2.mg-1}$

3.3V SPI interface: sensitive to SET in read mode only (no write errors observed)

- TID sensitivity:

- No performance degradation > 100 krad(Si)

#### Magnetic sensitivity:

No functional degradation > 1000 Gauss\*

Life test:

$_{\odot}$  No functional degradation after 1000 hrs at +125  $^{\circ}\text{C}$

### **MNEMOSYNE ASIC**

- **Functional Results**

- SPI 1.8v interface

Quad SPI up to 100MHz fast read

Octal SPI up to 50MHz fast read

512 Mbits or 1 Gbits density

- SPI 3.3v interface

Quad SPI up to 100MHz fast read

512 Mbits or 1 Gbits density

Boot LEON2 micro controleur

Boot Xilinx FPGA

Boot Nanoxplore FPGA

Issue to boot Nanoxplore SOC

EEPROM 3.3v Interface

0 128 Mbits density

### CONCLUSION

### This memory ASIC is a beautiful tribute to Mnemosyne goddess.

# www.3d-plus.com

408 rue Hélène Boucher 78530 Buc - **FRANCE** +33 130 832 650

1247 Reamwood Avenue Sunnyvale, CA 94089 - **USA** +1 408-734-8200

#### OUR MISSION IS THAT YOU ACHIEVE YOURS