# Methodology with a formal approach for selective radiation mitigation in space-grade FPGAs

Siemens EDA, IC Verification Solutions

#### Agenda

Trends and industry challenges

SEU Analysis Overview

SEU Methodology Overview

## Industry challenges

Current headwinds impacting success

## Challenge 1: The productivity gap

The widening gap between increasing project complexity and availability (and effectiveness) of talent

**Ever-present productivity gap is growing, with resource deficits predicted** Growth in DV teams, where possible, only slowed the growing gap

Unrestricted | © Siemens 2025 | Siemens Digital Industries Software

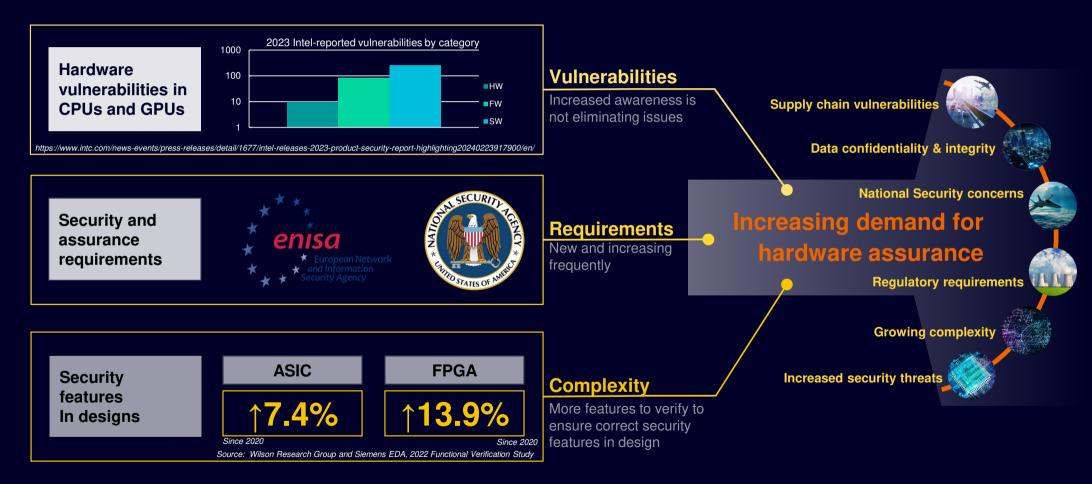

### Challenge 2: Hardware assurance

System operational requirements and global environment drive increased assurance scrutiny

#### Failure-intolerant applications are increasing in high-vulnerability environment Current verification methods can not deliver proof of compliance

## Addressing these challenges with Static & Formal technologies

Static and Formal are critical to success amidst today's industry challenges Complementary to simulation, deliver assurance and productivity

Questa OneSpin Static & Formal address industry's largest challenges Complete solution to accelerate productivity & a deterministic path to success

| <b>Questa Design Solutions</b><br>Automatic Formal for<br>designers <u>and</u> Verification<br>engineers                                                   | Questa OneSpin Solutions<br>Powerful formal verification for<br>critical design functions                                                                                | Questa Equivalent Design<br>Ensure clean designs remain<br>clean throughout<br>implementation |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| <ul> <li>Increase RTL quality - without<br/>a testbench</li> <li>Design Checking</li> <li>Metastability prevention</li> <li>Connectivity Proofs</li> </ul> | <ul> <li>Find bugs simulation cannot</li> <li>Critical functionalities</li> <li>Processor Verification</li> <li>Security Validation</li> <li>Coverage closure</li> </ul> | RTL vs RTL<br>RTL vs Gate<br>Verification of ECO changes                                      |

## SEU challenges and engine analysis overview

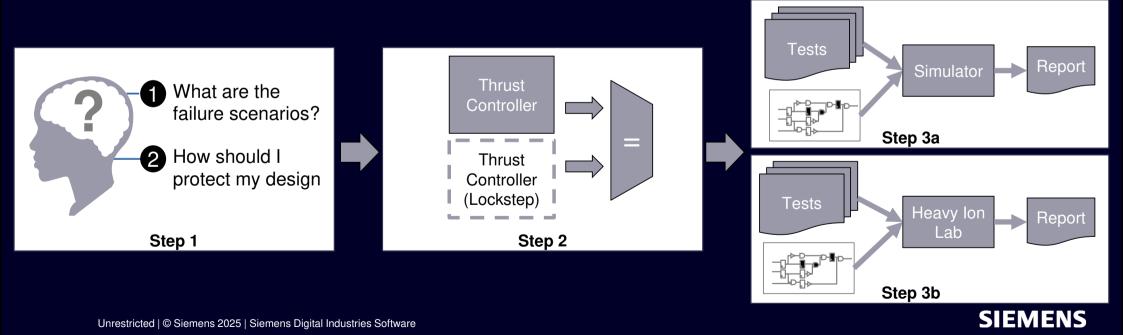

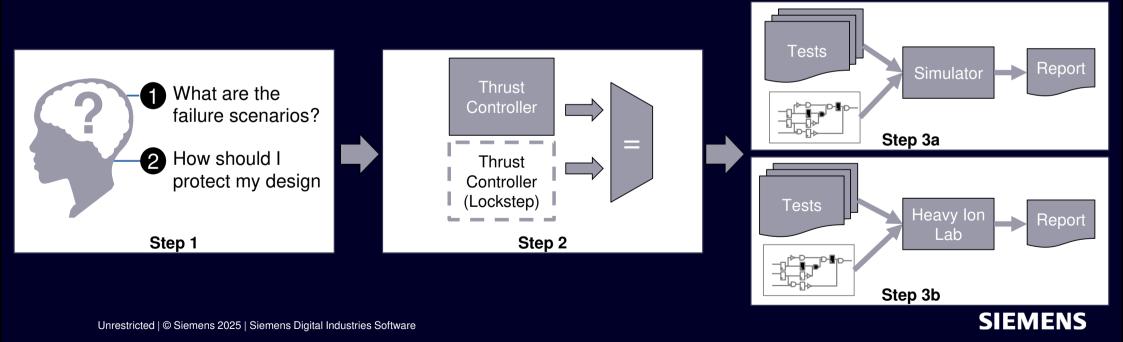

#### **Common approach to Logical SEU mitigation**

Step 1: Failure points are identified through expert driven analysis

- Step 2: Insertion of protection is performed by design engineers

- Step 3: Verification is commonly performed by (either or both):

- Simulation leveraging functional regressions and force commands to inject faults

- Functional testing under heavy ion exposure

#### Challenges with common approach

- **1. Implementation**: Identifying optimal mitigation strategy

- **2. Verification**: Delivering quantitative assurance of mitigation effectiveness

- **3. Debug**: Visibility and analytics to quickly root cause and fix failures

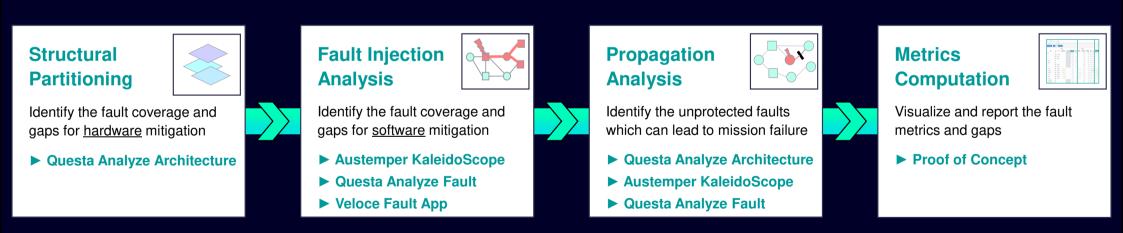

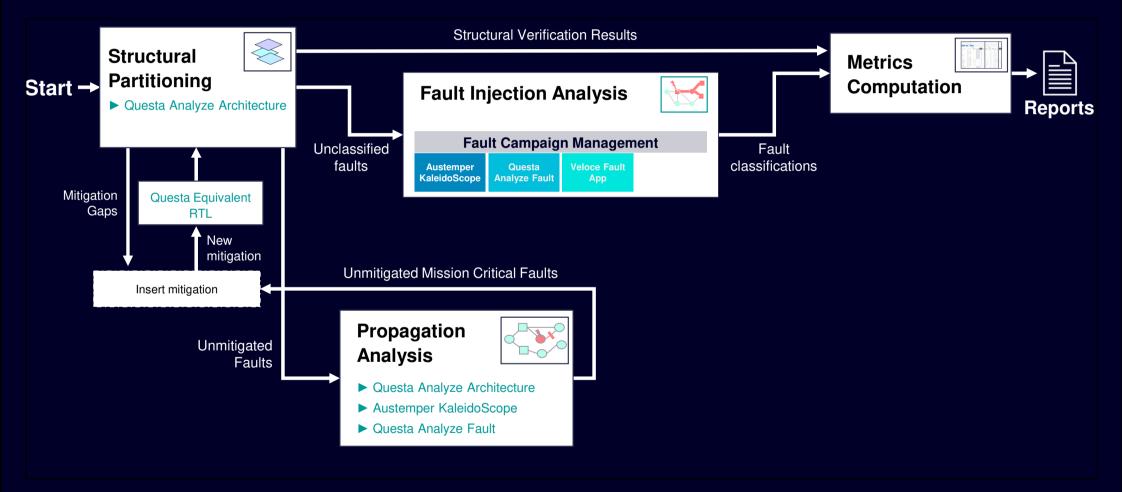

#### Logical SEU radiation mitigation platform

- **1.** Identifies issues in existing logical radiation mitigation

- 2. Classifies unmitigated logic based on it's potential to affect mission critical functions

- 3. Provides a quantitative assessment of the logical mitigation and generates reports

## Logical SEU Mitigation Methodology Overview

#### Logical SEU radiation mitigation methodology

Unrestricted | © Siemens 2025 | Siemens Digital Industries Software

### Conclusion

SIEMENS

#### Conclusion

Productivity gap is growing. Complexity is increasing

- Teams need to adopt more advanced verification techniques

- Static & Formal can help both in finding bugs earlier, and in finding bugs other solutions cannot

#### This proposed methodology

- Provides a quantitative assessment of the effectiveness of SEU mitigation strategies

- Highlights existing gaps and unprotected logic

- Leverages Siemens' static and formal verification technologies, to achieve absolute assurance and increased productivity in addressing these critical hardware reliability challenges.

#### Disclaimer

© Siemens 2025

Subject to changes and errors. The information given in this document only contains general descriptions and/or performance features which may not always specifically reflect those described, or which may undergo modification in the course of further development of the products. The requested performance features are binding only when they are expressly agreed upon in the concluded contract.

All product designations may be trademarks or other rights of Siemens AG, its affiliated companies or other companies whose use by third parties for their own purposes could violate the rights of the respective owner.

## Contact

Published by Siemens

Mark Handover Application Engineer

E-mail mark.handover@siemens.com