# FRONTGRADE Gaisler

GR765:

A Radiation-Hardened, Fault-Tolerant Octa-Core SoC with Integrated eFPGA for Next-Generation Space Avionics

**EDHPC 2025**

# Agenda

| 01 | Introduction           | 04 | Authenticated boot and security features |

|----|------------------------|----|------------------------------------------|

| 02 | Processor system       | 05 | Conclusions                              |

| 03 | Integrated peripherals | 03 | Conclusions                              |

# Introduction

PUBLIC

### **GR765 - Introduction**

GR765 is a new processor component for space developed by Frontgrade Gaisler on STMicroelectronics 28nm technology platform.

Successor to GR740 as the high-end processor product in Frontgrade Gaisler's portfolio.

Development supported by European Space Agency ARTES, TDE, GSTP, and NAVISP EL2 programmes, SNSA and Frontgrade funding.

# **GR765** – Key features

| ARCHITECTURE  | Octa-core SPARC v8 / RISC-V RV64GCH                                                      |

|---------------|------------------------------------------------------------------------------------------|

| QUALIFICATION | ESCC Generic Specification No. 9030                                                      |

| PACKAGE       | PBGA 1752 (45x45 mm, 1mm ball pitch)                                                     |

| TID           | 50 krad(Si) (guaranteed by platform)<br>100 krad(Si) (testing/screening to be performed) |

| SEL IMMUNITY  | 60 MeV*cm <sup>2</sup> /mg @125°C                                                        |

| TECHNOLOGY    | STM 28nm FDSOI                                                                           |

| SUPPLIES      | Core: 1.0 V<br>I/O: 1.2 V 3.3 V                                                          |

| FREQUENCY     | 800 MHz, delivering 2600 DMIPS/core                                                      |

| POWER         | 10 W @ 25°C (TBC)                                                                        |

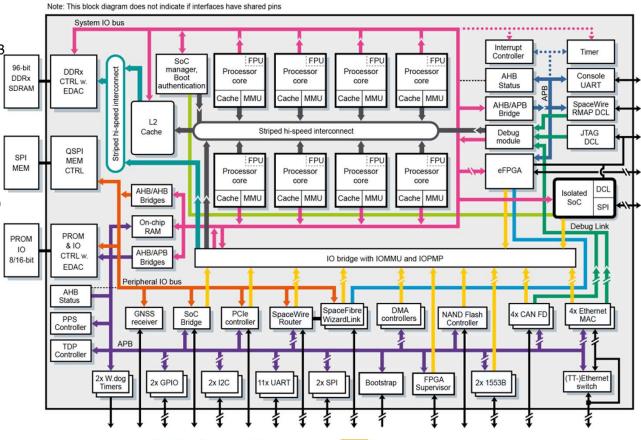

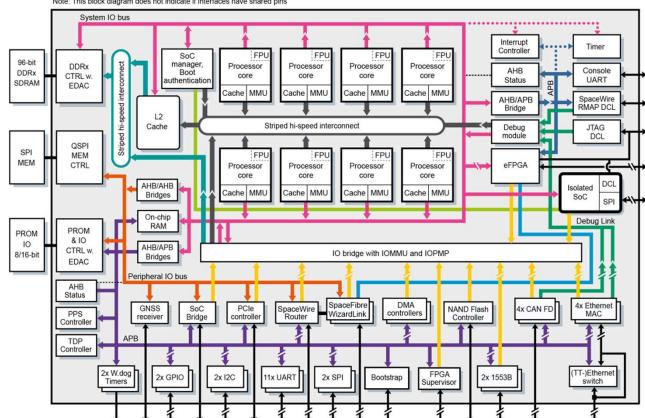

# **GR765 – Block diagram**

- Fault-tolerant octa-core architecture

- LEON5FT SPARC V8 or NOEL-V RV64GCH

- each core with SIMD extensions, FPU, and MMU, 32 KiB per core L1 cache

- connected via multi-port interconnect

- 4 MiB L2 cache, 512-bit cache line, 8-ways

- DDR2/3/4

- 96-bit interface with dual x8 device correction capability

- 80-bit interface with x8 device correction capability

- 72-bit interface with error detection capability (SECDED)

- 8/16-bit PROM/IO interface

- (Q)SPI and NAND memory controller interfaces

- eFPGA 30k LUT

- Built-in GNSS receiver for (GPS and Galileo)

- Hardware authenticated boot (hybrid scheme with ECDSA, ML-DSA)

- Isolated SoC / HSM for HW RoT, Secure Boot, Crypto

- DMA controllers

noel-V

# **GR765** – Raw numbers comparison with **GR740**

| Metric                | GR740                                         | GR765                                          | Change |

|-----------------------|-----------------------------------------------|------------------------------------------------|--------|

| CPU performance       | 4-core, single-issue, 250MHz                  | 8-core, dual-issue, 800 MHz                    | 12X    |

| RAM capacity          | SDRAM PC100, 512 MiB                          | DDR4-1600, 16 GiB                              | 32X    |

| RAM bandwidth         | 64 x 100Mbps = 6.4 Gbps                       | 64 x 1600 Mbps = 100 Gbps                      | 16X    |

| IO bandwidth (in+out) | PCI 32x33M = 1Gbps<br>SpW 8x2x200M = 3.2 Gbps | PCle 8x2x4G = 64 Gbps<br>SpFi 4x6.25 = 25 Gbps | 27X    |

# Processor system

PUBLIC

### **Instruction Set Architectures**

#### Why RISC-V?

- Hardware and software potential for future space applications: A new class of processors requires a modern architecture

- Enabling new technologies by standardization

- Hypervisor support

- Vector extension, ...

- Growing base of 3<sup>rd</sup> party ecosystem:

- Toolsets

- Libraries, engines etc.

- Attractive to talent entering the space domain

- Influx of know-how by talent entering the space domain

#### Why SPARC?

- Existing base of space proven HW and SW designs

- Mature ecosystem for today's space applications, e.g. qualified OS

- Accumulated development knowhow in the industry

- Software backward compatible with existing LEON devices

#### **GR765 provides RISC-V and SPARC**

- Both architectures are needed by the industry

- Faster time-to-market for RISC-V while continuing SPARC – ease transition between the two architectures

- Minimal silicon overhead sharing of resources on chip. User selects CPU (LEON5FT or NOEL-VFT), device cannot operate with both at the same time.

### **GR765 – Processor cores**

# LEONS SPARC

- 32-bit SPARC V8 processor core

- Improved performance over LEON3 & LEON4

- In-order dual-issue pipeline

- Improved fault tolerance (FT) from SEUs

- Improved FPU: denormalized number support

- Leverage existing software: maintain binary compatibility with LEON3 and LEON4

#### New fault tolerant features

- L1 cache SECDED ECC allows error correction on the fly

- Optional internal hardware scrubber for L1 and register file

- RISC-V processor core

- 64-bit (RV64I) implementation in GR765

- Superscalar in order pipeline

- Same fault-tolerance features as LEON5FT

- Leverages RISC-V software and tool support in the commercial domain together with same level of software support provided by Gaisler as for the LEON line of processors

#### **GR765** feature set

- RISC-V RV64GCH

- Can run complex OS (like Linux), also within virtual machine

- OS-A Embedded RISC-V platform specification

### **NOEL-V – RISC-V Processor**

- RISC-V processor core

- Superscalar in order pipeline

- RV64GCH 64-bit processor

- 64 Base integer instructions (I)

- MUL/DIV (M)

- Atomics (A)

- Half/Single/Double Precision Float (Zfhmin, FD)

- Compressed instructions (C)

- Hypervisor (H)

- Bit manipulation (subset of) (B)

- Physical Memory Protection (PMP)

- MMU 39 bit virtual addressing, separate I and D, fully associative, TLB

- Cache control extensions

- Cacheline invalidate, zero, etc (Zicbom, Zicbop, Zicboz)

- Cachability in page tables (Svpbmt)

- RISC-V Advanced Interrupt Architecture (AIA)

#### **Performance:**

- Comparable to ARM Cortex A53

- CoreMark\*/MHz: 5.02\*\*

<sup>\*</sup>gcc (ge0886d8ad) 15.0.1 20250330 (experimental)

<sup>-</sup>O3 -ffast-math -march=rv64imafdc\_zba\_zbb\_zbc\_zbs\_zbkb\_zbkc\_zbkx\_zicond\_zifencei\_zfh\_zicbom -mabi=lp64d -finline-functions --param max-inline-insns-auto=20 --param inline-min-speedup=10 -funswitch-loops -funroll-all-loops -fgcse-after-reload -fpredictive-commoning -fipa-cp-clone -falign-jumps=8 -falign-functions=8 --param=11-cache-line-size=32 --param=11-cache-size=16

<sup>\*\*</sup> Using "#define ee u32 int32 t" in core portme.h, as is common for 64 bit RISC-V.

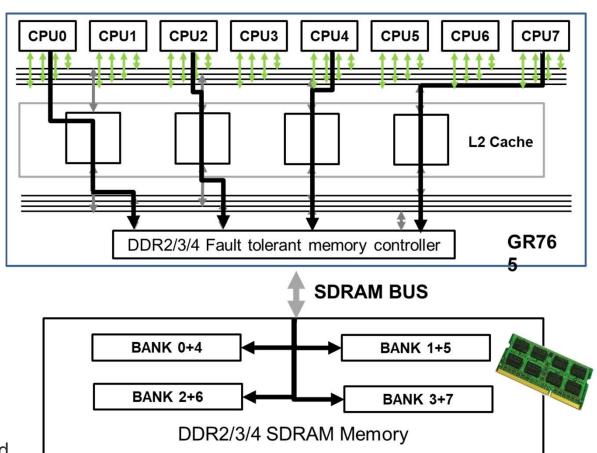

# **GR765** – Improved interconnect

- Banked / Striped on-chip bus interconnect creating four separate L2+bus hierarchies that map to different internal banks of the SDRAM.

- CPUs accessing two different stripes will have zero interference on L2 hit and near-zero on L2 miss.

- Mapping between linear RAM address (as seen from software/DMA) and stripes reconfigurable.

Can be tuned for performance/scaling, timing isolation or hybrid of the two.

- This striping approach is fully cache-coherent and transparent to software.

# Integrated peripherals

### **GR765** – Interfaces

#### Interfaces - SPARC and RISC-V mode

- PCle Gen 3 4-port x2, 2-port x4, with Root Complex

- SpaceFibre 4-port x1 6.25 Gbit/s + WizardLink support

- **12-port** SpaceWire router with +4 internal ports

- 4x 10/100/1000 Mbit Ethernet MACs connected TTEthernet capable switch with 14 external ports. And TSN support.

- 2x MIL-STD-1553B

- 4x CAN-FD

- 2x I2C, 12x UART, 2x SPI controller

- SoC bridge interface

- FPGA supervisor interface

- Timers & Watchdog, GPIO ports

- Debug links:

- Dedicated: JTAG and SpaceWire

- CAN. Ethernet

#### In development No guarantee of product launch

#### noel-V

Note: This block diagram does not indicate if interfaces have shared pins

### **GR765** – embedded FPGA

- GR765 will incorporate a NanoXplore eFPGA

- 32k LUTs + 40x 48kbit BRAMs

- The eFPGA subsystem will be possible to operate without processor intervention.

- Reprogramming of the eFPGA will not affect processor execution.

- The eFPGA subsystem will be programmable from processors.

- AMBA AHB and APB ports will be accessible to processor subsystem.

- Bitstream authentication will be available.

- Supported by standard NanoXplore tool set.

- Supported by GRLIB IP cores.

# Authenticated boot and security features

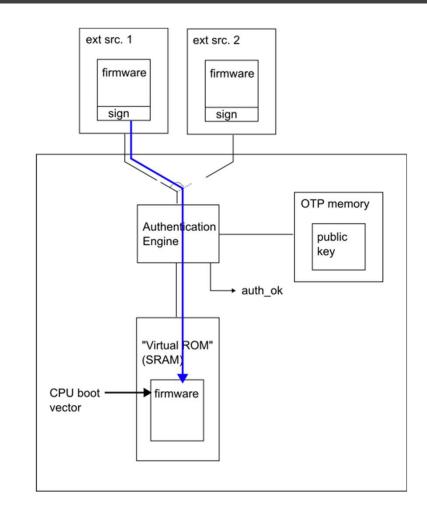

### **GR765 – Authenticated boot scheme**

- Scheme to extract first stage of software into on chip memory and verify cryptographic signature before CPU starts running

- With retry from alternate sources

- Using hybrid classic+PQC public-key signature verification algorithm implemented in hardware with public key stored on-chip in one-time programmable memory (OTP).

- Software-free process, managed by central SoC boot manager state machine and using hardware crypto accelerator cores.

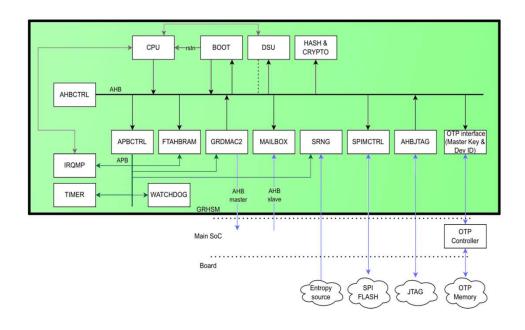

# **GR765 – Isolated Subsystem / Hardware Security Module**

Separate SoC with private external SPI flash storage that interfaces the rest of the system via a mailbox interface. Independent execution after device reset.

- Intended usage is as a hardware security module to perform attestation, key generation and other security/crypto-related tasks.

- Cores for SHA256 acceleration, and entropy/randomness generators for key generation.

- Working with third party provider to develop offthe-shelf software offering for the Isolated Subsystem

- Not mandatory for using the rest of the device, for applications that do not require this type of functionality.

PUBLIC

# Software support

**Next-Generation SoC**

# FRONTGRADE

# Software

- Complete ecosystem

- A combination of Gaisler and 3<sup>rd</sup> party software

# Tool chains, Operating systems and compilers

- Bare-C

- Linux

- RTEMS

- VxWorks

- Zephyr

### Hypervisors

- XtratuM/XNG (FentISS)

- PikeOS (SYSGO)

- Xvisor

#### **Boot loaders**

- MKPROM2

- GRBOOT Flight bootloader

#### Tools

- GRMON3

- TSIM3

# **GR765** and **GR740** software compatibility

- LEON5FT maintains backward compatibility with LEON4FT

- Software running on top of environments such as RTEMS, VxWorks, Linux, ... should not require any changes if moving from GR740 to GR765 (updated OS will be provided by GSL)

- Example: unmodified LEON3 Linux image will boot on LEON5

- Redefinition of some internal processor configuration registers, may affect operating system, bootloaders, etc.

- Set of communication interfaces is kept and expanded but PCI is removed

- · Changes will be addressed in a software porting guide

- Versions of communication controller IP may be updated, may require updated software drivers

- Memory controllers and pin-mux control are updated

- · Requires updates to bootloader

- Significant differences in timing (different processor microarchitecture, memory controller, bus structure, etc)

- Work ongoing to enable same level of software support for NOEL-V as for, and extending beyond, the LEON processors

# Conclusions

PUBLIC

## **GR765 Conclusion**

- The GR765 development builds on the successful GR740 quad-core LEON4FT component, with a major leap in performance and numerous additional enhancements.

- The GR765 is an octa-core processor. Users can enable either eight NOEL-VFT RISC-V

64-bit processor cores or eight LEON5FT cores.

- GR765 supports DDR2/3/4 SDRAM, high-speed serial link controllers and several other extensions.

- The GR765 development puts emphasis on computational performance, power

efficiency, and support for mixed criticality application with a high degree of integration to

allow an overall cost, space and power efficient board-level solution.

- The GR765 is supported by a strong software ecosystem.

noel-V

LEON5

# Thank you for listening!

hwww.gaisler.com/GR765

PUBLIC