# Development Status of the 2nd-generation On-board Processing Unit Using COTS GPU

Takeshi Tachibana, Jin Miyazawa, Kenji Maeno, Shoya Otsu, Minoru Yoshida, Toru Sasaki,

Hiroshi Kishimoto, Shinya Hirakuri, Shota Suzuki, Yosuke Sato, Akira Chiba

Mitsubishi Electric Corporation (MELCO)

# **■** Table of contents

- Introduction

- Our History: 1st to 2nd Generation

- 2nd-Gen System Architecture

- Environmental Tests for GPU

- Bread Board Model (BBM)

- Summary & Future Works

# **■** Introduction

## Many missions so far:

**GEO Satellite**

**LEO Satellite**

Lander

Ground

# **Data Handling**

- · CCSDS TC/AOS

- SpaceWire

- · 1553B...

# **Data Processing**

- SAR imaging

- Optical imaging

- Target detecting

- Template matching ...

# Introduction

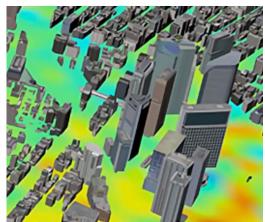

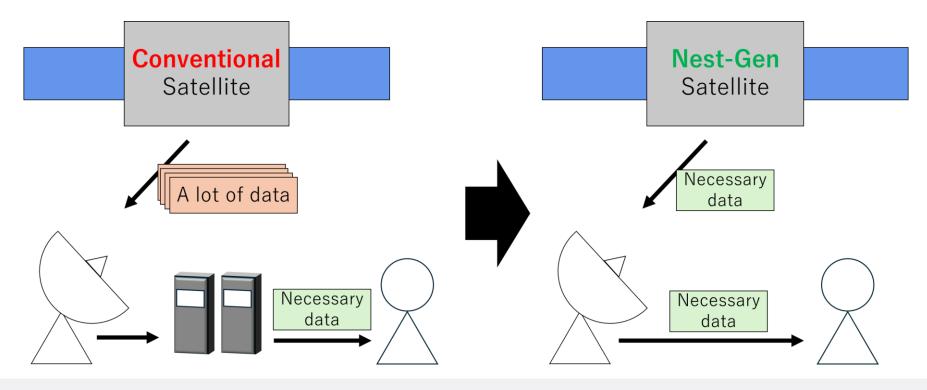

## • Background:

- Increasing the amount of payload data from advanced satellite sensors.

- —Growing user demand for <u>faster data delivery</u>.

- —Evolution of semiconductor technology.

#### Solution:

- -Process & Compress raw data in orbit.

- -Downlink only necessary data.

- —Overcome limited downlink bandwidth.

# Introduction

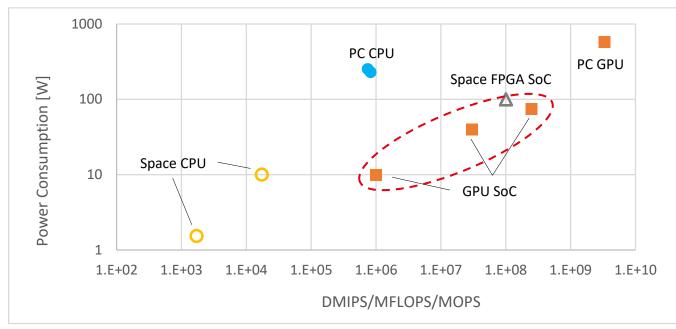

#### Problem:

- —Space-grade CPUs <u>lack sufficient performance</u> for these demanding tasks.

- -PC CPUs and PC GPUs have too large power consumption.

## Our Approach: COTS GPU-SoC

- Achieving both high performance and low power consumption.

- —Easy to reconfigure or update in orbit.

- —Low procurement costs.

<sup>\*</sup> The evaluated processors are as follows. Those for space are underlined (shown in white in the diagram).

CPU: Ryzen 9 7950X, Intel i9-14900KF, <u>HPSC</u>, <u>GR740</u>

GPU: GeForce RTX 5090, Jetson AGXi Orin, Jetson AGX Xavier, Jetson TX2i

FPGA: Versal VC1902

# ■ Our History: 1<sup>st</sup> to 2<sup>nd</sup> Generation

#### • Since 2020:

Developing COTS GPU for On-board Processing.

#### 1st-Gen Achievement: GEMINI

—Will be launched and demonstrated in JFY2025.

# Mission Objectives:

- —SAR processing on GEMINI simulated data.

- —Target detection with Al.

- —On-orbit software updates.

- —Investigation SEEs during the one-year mission period.

- Measuring MTBF in space environment.

**RAISE-\*** (**RA**pid Innovative payload demonstration **S**atellit**E-\***):

a satellite for on-orbit demonstration themes selected in the "Innovative Satellite Technology Demonstration Program".

**GEMINI**: cots **G**PU based **E**dge computing for **MI**ssion systems utilizing model based systems engi**N**eer**I**ng)

# ■ Our History: 1<sup>st</sup> to 2<sup>nd</sup> Generation

## **Developing the 2<sup>nd</sup>-Generation since 2022.**

- 2<sup>nd</sup>-Gen Adopted Device:

- —NVIDIA Jetson AGX Xavier Industrial (JAXi)

- Key Features:

- —<u>Highly integrated</u> module (SoC, DRAM, flash, power, clock, etc.).

- —<u>High-speed interfaces</u> (e.g., PCle for > several Gbps).

- -Enables high performance with low design cost.

https://www.nvidia.com/ja-jp/autonomous-machines/embedded-systems/jetson-agx-xavier/#

#### Standard:

—<u>6U SpaceVPX</u> (VITA78) compliant.

#### Controller Board:

- —<u>FPGA</u> for system control & data handling.

- —<u>DDR4 memory</u> for buffering payload data.

- —<u>Flash memory</u> for storing program data.

- -Implemented using radiation-tolerant parts.

#### GPU Boards:

- —Utilize COTS/low-grade parts for high performance.

- -2 JAXi modules per board.

- -Total of 6 boards (12 JAXis).

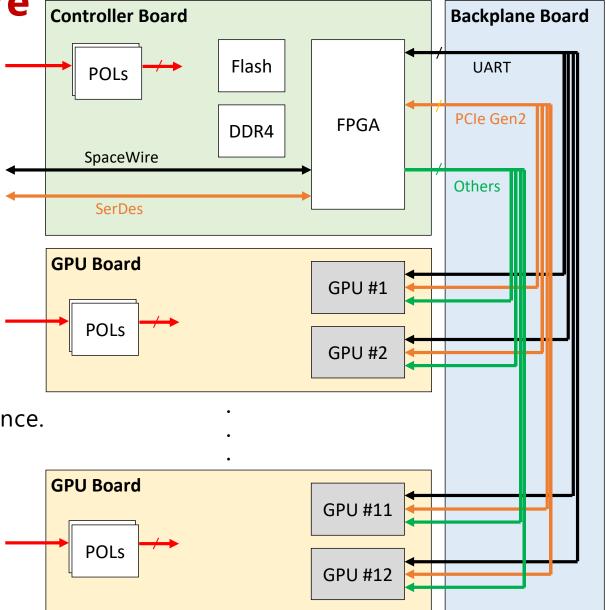

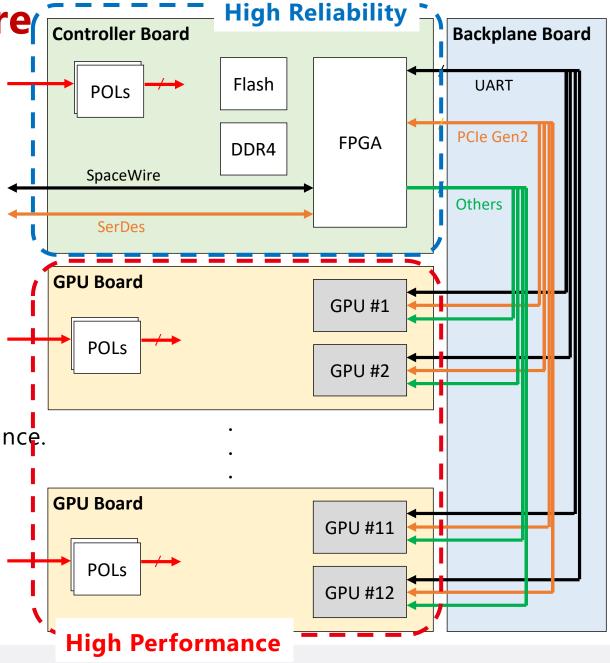

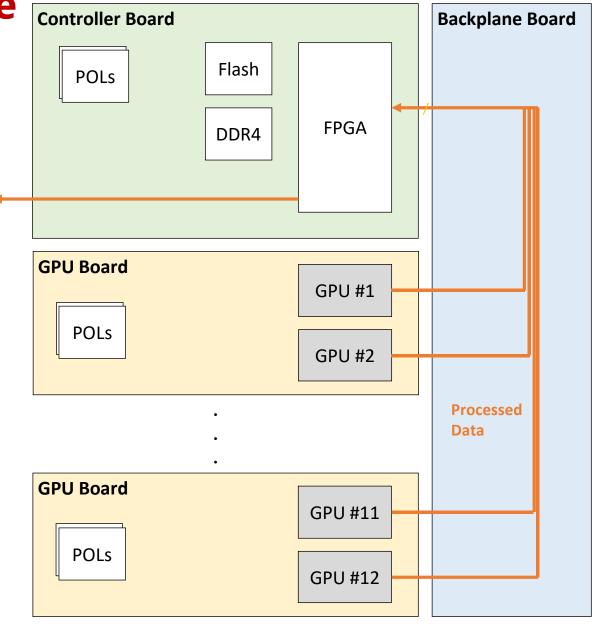

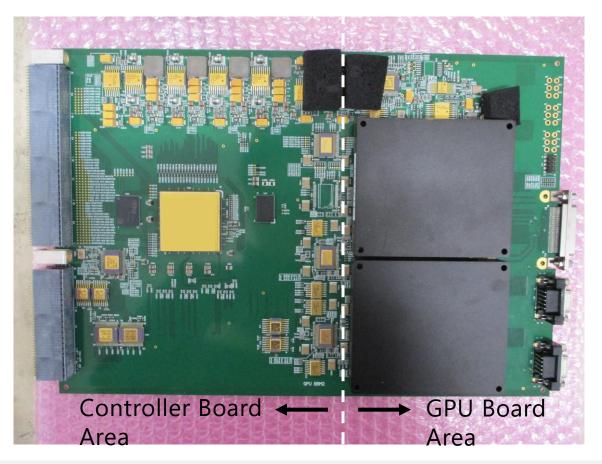

■ 2<sup>nd</sup>-Gen System Architecture Controller Board

#### Standard:

—<u>6U SpaceVPX</u> (VITA78) compliant.

#### Controller Board:

- —<u>FPGA</u> for system control & data handling.

- —<u>DDR4 memory</u> for buffering payload data.

- —<u>Flash memory</u> for storing program data.

- -Implemented using radiation-tolerant parts.

#### GPU Boards:

- —Utilize <u>COTS/low-grade parts</u> for high performance.

- -2 JAXi modules per board.

- -Total of 6 boards (12 JAXis).

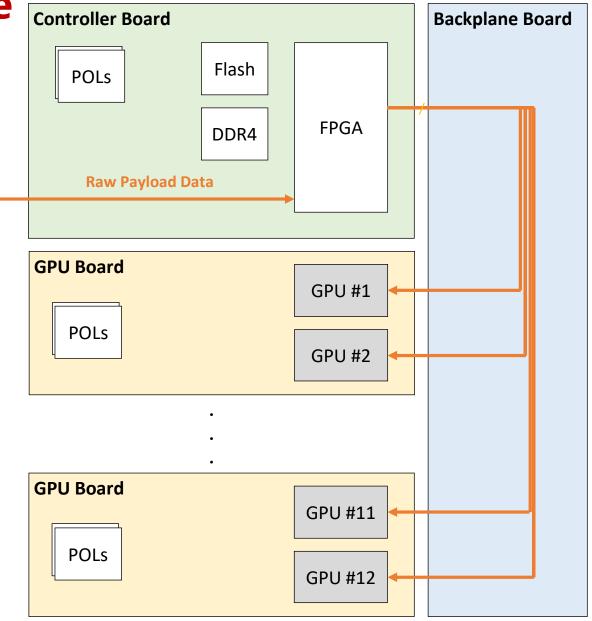

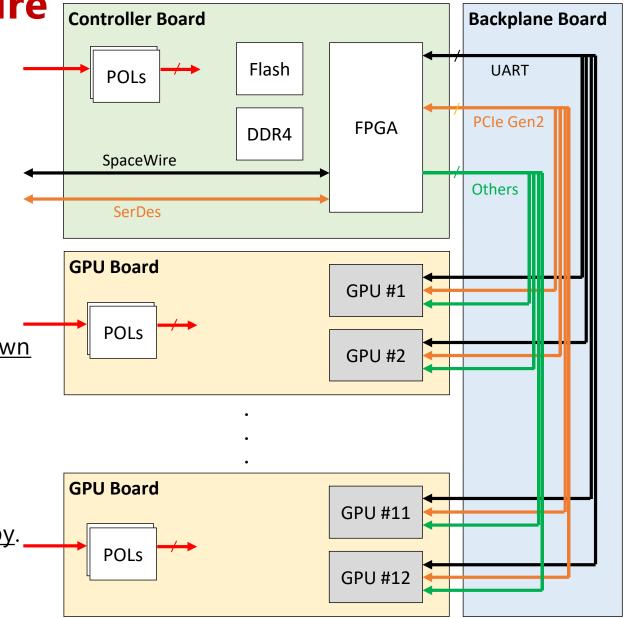

# <Data Processing Flow>

#### 1. Distribute:

FPGA distributes raw data to each GPU via PCIe.

## 2. Process & notify:

GPUs process data in parallel, and GPUs notify FPGA of completion via UART.

#### 3. Request:

FPGA requests the processed data from GPUs.

#### 4. Send:

# < Data Processing Flow >

#### 1. Distribute:

FPGA distributes raw data to each GPU via PCIe.

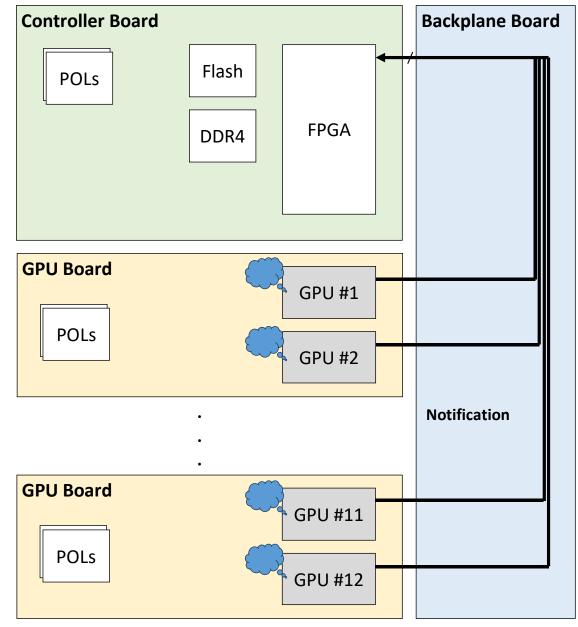

## 2. Process & notify:

GPUs process data in parallel, and GPUs notify FPGA of completion via UART.

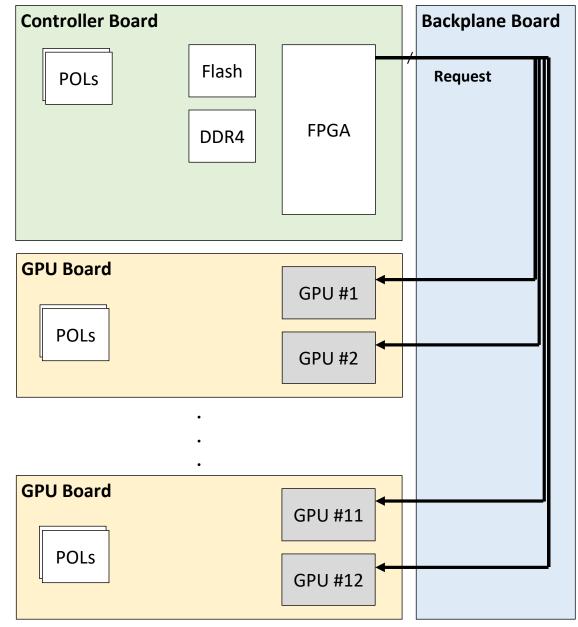

#### 3. Request:

FPGA requests the processed data from GPUs.

#### 4. Send:

# <Data Processing Flow>

#### 1. Distribute:

FPGA distributes raw data to each GPU via PCIe.

## 2. Process & notify:

GPUs process data in parallel, and GPUs notify FPGA of completion via UART.

#### 3. Request:

FPGA requests the processed data from GPUs.

#### 4. Send:

# <Data Processing Flow>

#### 1. Distribute:

FPGA distributes raw data to each GPU via PCIe.

## 2. Process & notify:

GPUs process data in parallel, and GPUs notify FPGA of completion via UART.

#### 3. Request:

FPGA requests the processed data from GPUs.

#### 4. Send:

# < Radiation Hardening (1): SEL>

## Challenge:

—Single Event Lath-up (SEL):A destructive overcurrent failure.

#### Our Solution:

—Isolation:

POL converter's <u>overcurrent detection/shutdown</u> function isolates the faulty module and <u>prevents failure propagation</u>.

#### -Redundancy:

Up to 10 GPUs can be operated in parallel and 1 spare GPU board (2 modules) on standby.

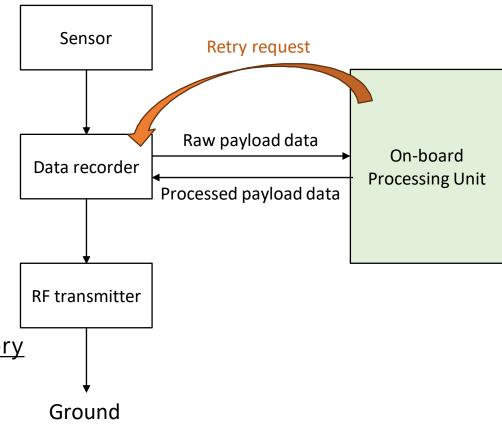

# < Radiation Hardening (2): SEU/SEFI>

## Challenge:

—Single Event Upset (SEU) & Functional Interrupt (SEFI): Transient errors during processing.

#### Our Solution:

## -Retry Mechanism:

- <u>Retry request</u> is sent to an external data recorder.

- · Power cycling (if necessary).

#### - Program Data Integrity:

Program data <u>is stored in radiation-tolerant flash memory</u> on the controller board, and deployed from FPGA to GPUs.

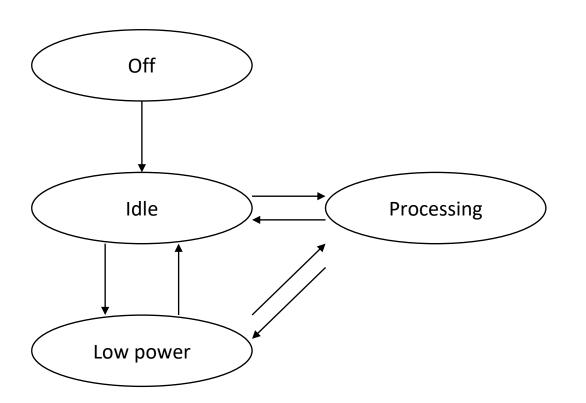

# <Running modes>

This system has four running modes.

| Mode       | Power consumption |

|------------|-------------------|

| Off        | < 0.1 W           |

| Idle       | < 80 W            |

| Processing | < 500 W           |

| Low power  | < 10 W            |

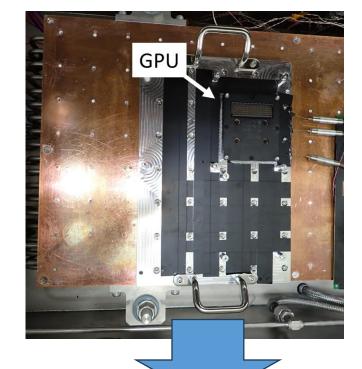

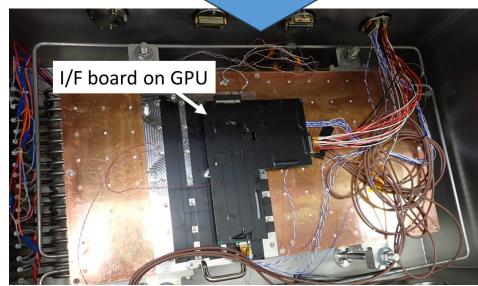

# **■ Environmental Tests for GPU**

#### Tests Performed:

- —Vibration Test.

- —Shock Test.

- —Thermal Vacuum Test.

## Test Program (operated periodically):

- -Al inference.

- —Health checks of memory and UART/PCIe interfaces.

- -Logging temperature and CPU/GPU usages.

#### Results:

- √ No damage and failures in all tests.

- Stable operation during thermal vacuum tests.

- ✓ Internal temperatures <u>remained within specified limits</u>.

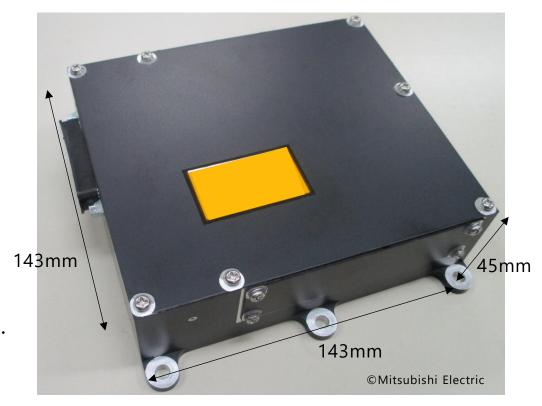

# **■** Bread Board Model (BBM)

Completely developed BBM and conducting the functional performance tests.

| Main Functions             | Verification Results                                                     |

|----------------------------|--------------------------------------------------------------------------|

| GPU Power Control          | Worked normally during<br>both power-on/off<br>sequences.                |

| Telemetry/Command Control  | ✓ Processed normally.                                                    |

| Payload Data<br>Handling   | <ul> <li>Proper data handling and<br/>PCle DMA with two GPUs.</li> </ul> |

| Program Data<br>Deployment | Ongoing.                                                                 |

# Summary

- Developing a 2<sup>nd</sup>-Gen On-board Processing Unit using NVIDIA JAXi COTS GPU.

- Environmental tolerance confirmed:

GPU module passed vibration, shock, and thermal vacuum tests.

Main Functions Verified:

BBM tests showed satisfactory results for power control, T&C, and data handling. Verification of program data deployment function is ongoing.

# **■ Future Works**

- Execute computationally intensive tasks and evaluate processing time/latency.

- Conduct thermal cycle test to assess system lifetime. ←Ongoing.

- Investigate strategies for managing multiple GPU's heat.

Name: Takeshi Tachibana

Number: +81 467 41 6209

E-mail: Tachibana.Takeshi@dw.MitsubishiElectric.co.jp

# **Appendix**

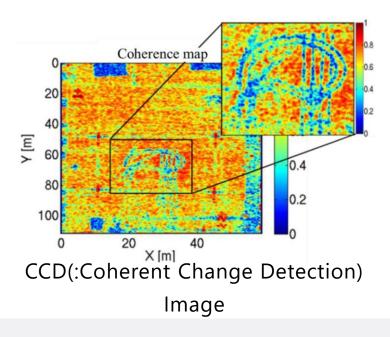

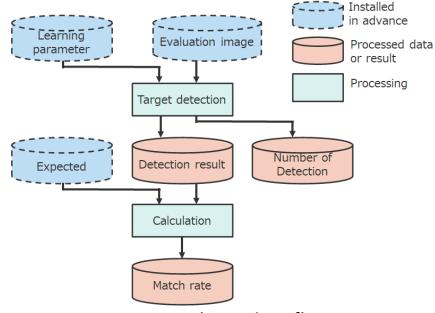

# ■ GEMINI S/W

- SAR Processing

- Target Detection

- Update Learning Parameter

SAR Image

Target detection flow

Expected detection result