**DEFENCE AND SPACE**

#### **DEFENCE AND SPACE**

| Section 1 (not applicable in France, please go to section 3)                                                                                                                                                                               |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| This document contains Technical Information :                                                                                                                                                                                             |  |  |  |  |

| Yes 128 No □                                                                                                                                                                                                                               |  |  |  |  |

| If No to section1: please complete Section 2                                                                                                                                                                                               |  |  |  |  |

| If Yes to section1: please complete Section 3 as applicable                                                                                                                                                                                |  |  |  |  |

| Section 2 (not applicable in France, please go to section 3)                                                                                                                                                                               |  |  |  |  |

| I confirm the document does not contain Technical Information and is « Not-Technical »                                                                                                                                                     |  |  |  |  |

| Name:                                                                                                                                                                                                                                      |  |  |  |  |

| Date:                                                                                                                                                                                                                                      |  |  |  |  |

| Section 3                                                                                                                                                                                                                                  |  |  |  |  |

| 3a. National and EU regulations Export Control Assessment                                                                                                                                                                                  |  |  |  |  |

| This document has been assessed against applicable export control regulations in                                                                                                                                                           |  |  |  |  |

| ■ France Germany Spain UK Cher                                                                                                                                                                                                             |  |  |  |  |

| ☑ and does not contains Controlled Technology¹ and is therefore « Not Listed / Not Controlled »                                                                                                                                            |  |  |  |  |

| and contains Controlled Technology with export control classification                                                                                                                                                                      |  |  |  |  |

| □ <u>Note</u> : Any transfer of this document in part or in whole must be made in accordance with the appropriate export control regulations. Prior to any transfer outside of the responsible legal entity, confirmation of an applicable |  |  |  |  |

| export licence or authorisation must be obtained from the local Export Control Officer (ECO).                                                                                                                                              |  |  |  |  |

| 3b. US (ITAR/EAR) Export Control Assessment                                                                                                                                                                                                |  |  |  |  |

| This document does not contains US origin Technical Data (Technology)                                                                                                                                                                      |  |  |  |  |

| ☐ This document contains « Technology » which is controlled by the U.S government under [USML category number / ECCN] and which has been                                                                                                   |  |  |  |  |

| received by [Legal entity] under the authority of [Licence number / ITAR exemption / EAR licence exception / NLR]                                                                                                                          |  |  |  |  |

| ☐ This document contains technology which is designated as EAR99 (subject to EAR and not listed on the USML/CCL.)                                                                                                                          |  |  |  |  |

| Note: Any re-export or re-transfer of this document in part or in whole must be made in accordance with the appropriate regulation (ITAR or EAR) and applicable authorization. If in any doubt please contact your local ECO.              |  |  |  |  |

| 3c. Technical Rater Information                                                                                                                                                                                                            |  |  |  |  |

| This document has been assessed by the following Technical Rater :                                                                                                                                                                         |  |  |  |  |

| Assessed and classified by: A.MEGE                                                                                                                                                                                                         |  |  |  |  |

| Date classification completed: 2025-10-10                                                                                                                                                                                                  |  |  |  |  |

Technology" is defined as any Information necessary for the design, development, production, use, operation, maintenance or repair of export controlled goods. Examples of such Information are blueprints, plans, diagrams, models, engineering designs, manuals, requirements specifications and instructions etc. If in any doubt please contact your local Export Control Officer (ECO)

## Space Electronics portfolio

Power & Propulsion Units

Platform & Payload Processing Units

**Sensors & Actuators**

www.airbus.com/en/products-services/space/equipment

## Motivations and stakes

### On board processing for earth observation (Optical / Radar / ...IA):

- Computational Power: FPGA Cores + AI Engines + Software Framework

- Memory Throughput (IA)

Different applications -> various usage of the processing core

#### **LEO Telecommunications / 5G:**

- ADC/DAC Interfaces: Many High Speed Serial Links, 25Gbps+

- Computational Power: FPGA + AI Engines + Processor: > 90W dissipated by FPGA

- Routing Interfaces: PCle3x8 (co-processing), 10Gb & 100Gb Ethernet

#### **Science:**

Mass Correlators / Computational Power: FPGA + Internal FPGA Memories

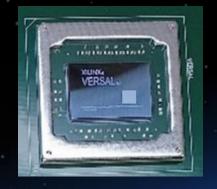

## Hardware equipment with VERSAL

## Real technical challenges:

- Power density heat dissipation

- Processing core supply: high current low voltage

- Data throughputs

- Technologies assembly & manufacturability (components pitches / high pin counts / PCB technologies ...)

### Keeping the constraints of space design

- Conductive cooling

- Radiations

- Reliability

- Etc...

Technical challenges must be addressed for a flight usage of the Versal chip

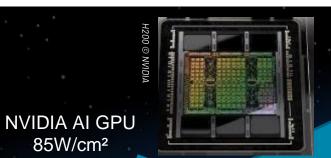

## Power density

**VERSAL**

20W/cm<sup>2</sup>

85W/cm<sup>2</sup>

Nuclear power plant 55W/cm²

Air fans, CC BY-SA 4.0 <a href="https://creativecommons.org/licenses/by-sa/4.0">https://creativecommons.org/licenses/by-sa/4.0</a>, via Wikimedia Commons Emmelie Callewaert, CC BY-SA 4.0 <a href="https://creativecommons.org/licenses/by-sa/4.0">https://creativecommons.org/licenses/by-sa/4.0</a>, via Wikimedia Commons

RTG4 2W/cm<sup>2</sup>

## Current

VERSAL 100A+

20 phases, 40A+ per phase

RTG4 12A

2 Phases, 6A per phase

4 phases, 25A per phase GaN transistor

1406

J405

1305

~100 Mbit/s, 1995

SpaceWire

## Data throughputs (per lane)

RTG4 3 Gbit/s, 2016

VERSAL 25 Gbit/s, 2020

H200 100 Gbit/s,2022

> **PCIE 7.0** 128 Gbit/s, 2025 (planned)

**PCIE 6.0** 64 Gbit/s, 2022

**PCIE 5.0** 32 Gbit/s, 2019

**PCIE 4.0** 16 Gbit/s, 2017

**PCIE 3.0** 8 Gbit/s, 2010

PCIE 2.0 4 Gbit/s, 2007

PCIE 1.0 2 Gbit/s, 2003

MIL-STD-1553

1 Mbit/s, 1975

| Space I | Electronics           |

|---------|-----------------------|

| . A S   | Space Products entity |

| Year          | Project | Key Features                                                                             | Innovations                                                                              | Applications                                                                                                | View |

|---------------|---------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|

| 2019-<br>2021 | ZUP     | Zynq UltraScale+ MPSoC  • Modular extended 6U VPX format 2xFMC+ digital/mixed mezzanines | DDR4 introduction at 1,866Gsps High-speed links 10Gbps  16 Layers stack up (1156pin SoC) | TELEO <sup>(1)</sup> <b>GEO</b> optical atmospheric feeder in-flight demonstrator  (1): successful in-orbit |      |

| Year          | Project | Key Features                                                                                                                                                 | Innovations                                                                                                                                  | Applications                                                                                         | View |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|

| 2019-<br>2021 | ZUP     | Zynq UltraScale+ MPSoC  • Modular extended 6U VPX format 2xFMC+ digital/mixed mezzanines                                                                     | DDR4 introduction at 1,866Gsps High-speed links 10Gbps  16 Layers stack up (1156pin SoC)                                                     | TELEO <sup>(1)</sup> GEO optical atmospheric feeder in-flight demonstrator  (1): successful in-orbit |      |

| 2020-<br>2022 | KUP     | <ul> <li>KU060 Kintex UltraScale</li> <li>SEL and SEU protection</li> <li>Modular extended 6U VPX format</li> <li>2xFMC+ digital/mixed mezzanines</li> </ul> | <ul> <li>HSSLs signal integrity simulations</li> <li>Backdrill introduction DDR4 tested at 2.4Gsps 22 Layers stack up (1517p SoC)</li> </ul> | Sunrise Laser LCT modem technology development  Hi-side Hyperspectral compression demonstrator       |      |

| Year          | Project | Key Features                                                                                                                                                                                         | Innovations                                                                                                                                                                                                                        | Applications                                                                                   | View                                         |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2019-<br>2021 | ZUP     | Zynq UltraScale+ MPSoC  • Modular extended 6U VPX format 2xFMC+ digital/mixed mezzanines                                                                                                             | <ul> <li>DDR4 introduction at 1,866Gsps         High-speed links 10Gbps</li> <li>16 Layers stack up (1156pin SoC)</li> </ul>                                                                                                       | TELEO(1) GEO optical atmospheric feeder in-flight demonstrator  (1): successful in-orbit       |                                              |

| 2020-<br>2022 | KUP     | <ul> <li>KU060 Kintex UltraScale</li> <li>SEL and SEU protection</li> <li>Modular extended 6U VPX format</li> <li>2xFMC+ digital/mixed mezzanines</li> </ul>                                         | <ul> <li>HSSLs signal integrity simulations</li> <li>Backdrill introduction DDR4 tested at 2.4Gsps 22 Layers stack up (1517p SoC)</li> </ul>                                                                                       | Sunrise Laser LCT modem technology development  Hi-side Hyperspectral compression demonstrator |                                              |

| 2023-<br>2026 | VIP     | <ul> <li>VERSAL SoC Ready for conduction cooled</li> <li>SEL and SEU protection 6U VPX format High-speed links: x16 @ 12Gbps+ on backplane 2x12 @ 25Gbps on 2xFMC+ Optical links 4x25Gbps</li> </ul> | <ul> <li>Advanced power and thermal management</li> <li>90W@core and &gt;150W at board</li> <li>24 Layers stack up (2192 p on SoC)</li> <li>Intensive signal integrity simulations</li> <li>Power integrity simulations</li> </ul> | Technology demonstrator <sup>(3)</sup> Use cases and applications developments                 | Avieus S S S S S S S S S S S S S S S S S S S |

| Year          | Project | Key Features                                                                                                                                                               | Innovations                                                                                                                                                                                                                       | Applications                                                                                                | View     |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------|

| 2019-<br>2021 | ZUP     | Zynq UltraScale+ MPSoC  • Modular extended 6U VPX format 2xFMC+ digital/mixed mezzanines                                                                                   | DDR4 introduction at 1,866Gsps High-speed links 10Gbps  16 Layers stack up (1156pin SoC)                                                                                                                                          | TELEO <sup>(1)</sup> <b>GEO</b> optical atmospheric feeder in-flight demonstrator  (1): successful in-orbit |          |

| 2020-<br>2022 | KUP     | KU060 Kintex UltraScale  • SEL and SEU protection  • Modular extended 6U VPX format  2xFMC+ digital/mixed mezzanines                                                       | <ul> <li>HSSLs signal integrity simulations</li> <li>Backdrill introduction</li> <li>DDR4 tested at 2.4Gsps</li> <li>22 Layers stack up (1517p SoC)</li> </ul>                                                                    | Sunrise Laser LCT modem technology development  Hi-side Hyperspectral compression demonstrator              |          |

| 2023-<br>2026 | VIP     | VERSAL SoC Ready for conduction cooled  • SEL and SEU protection 6U VPX format High-speed links: x16 @ 12Gbps+ on backplane 2x12 @ 25Gbps on 2xFMC+ Optical links 4x25Gbps | <ul> <li>Advanced power and thermal management         90W@core and &gt;150W at board</li> <li>24 Layers stack up (2192 p on SoC)</li> <li>Intensive signal integrity simulations</li> <li>Power integrity simulations</li> </ul> | Technology demonstrator <sup>(3)</sup> Use cases and applications developments                              | Augus S. |

| 2024-         | VHIPER  | VERSAL SoC 1xFMC+ connector Conduction cooled Rad-Tolerant                                                                                                                 | Radiation hardened power solution                                                                                                                                                                                                 | Earth Observation Science Telecom / Optical Coms modems                                                     |          |

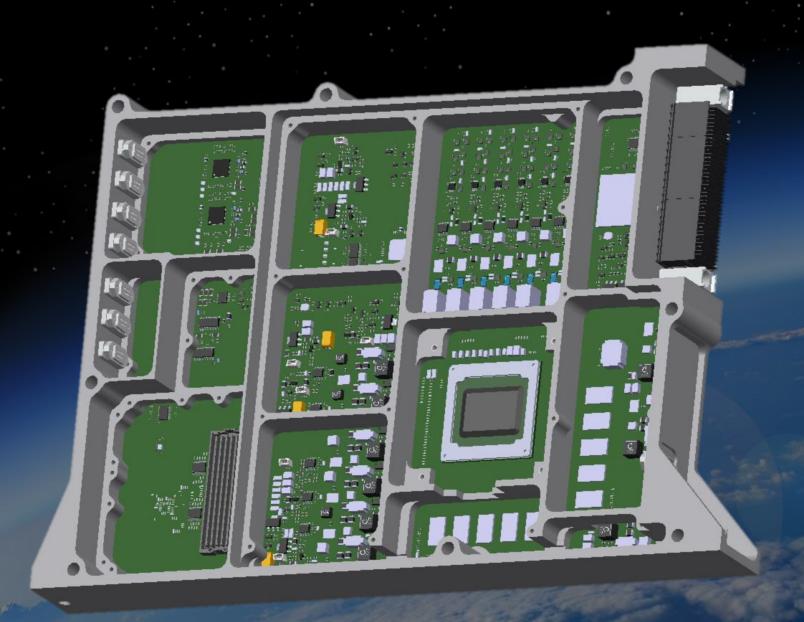

## VIP Board technology demonstrator

#### **Modular Format extended 6U VPX**

> 90W available on the FPGA

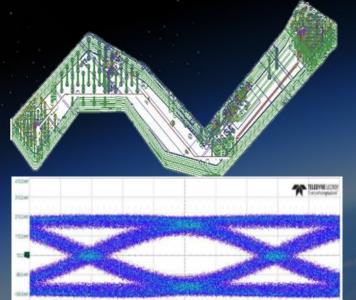

#### **HSSL links**

#### Backplane:

- Connector VPX RT3

- x16 @ 16Gbps+ (target)

FMC+: 2x12 @ 25Gbps (target)

Backdrill, microvias

#### Memory DDR4, 2 banks:

2GBytes DDR4 with ECC, >2.4Gbps x (64bits + 8 bits ECC) 2GBytes DDR4 with ECC, >2.4Gbps x (64bits + 8 bits ECC)

#### **Optical links**

module 4x25 Gbps TX/RX

# VIP Board technology demonstrator

FMC2 slot

Ethernet (GbE)

VPX interface (Power, std IO, High speed)

Commercial Point Of Load

Versal

DDR BK0

DDR BK1

## De-risking activities

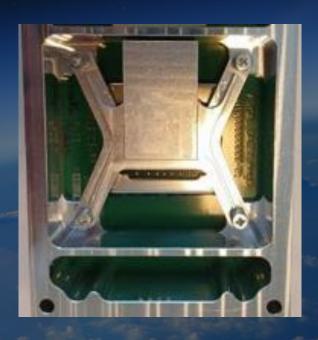

# Versal assembly prototyping (Report & X-rays)

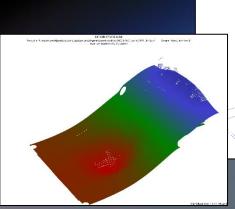

### **Power Integrity**

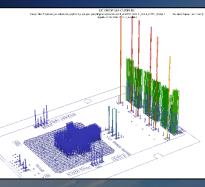

# High-Speed Links 3D PCB Signal Integrity Simulation

# Thermal Dissipation Mechanical Mockup

## De-risking activities

**EM Board New Space Components GaN Technology Transistors**

Output: 800 mV, 100A+

#### Tested at:

Continuous: 100A, 80W DC

• Transients: +25A, 200ns rise/fall time

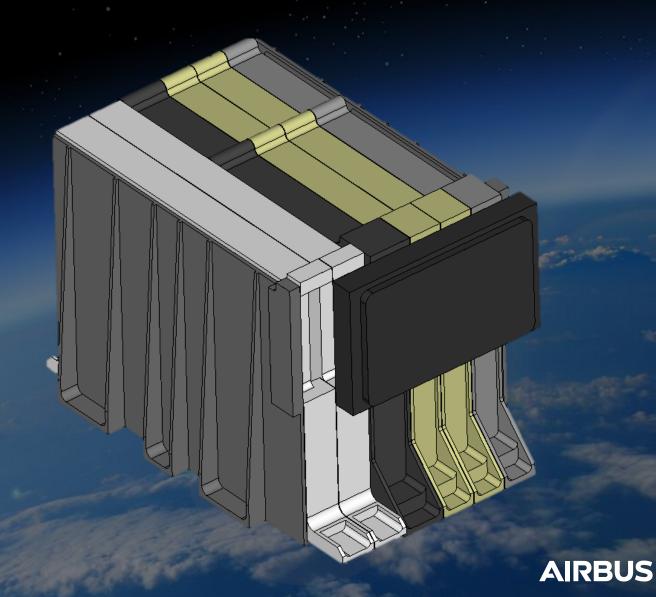

## VHIPER: An operational product EM

### **Derived from**

- VIP demonstration

- De-risking activities

**Preparing 1st Versal-based EM product**

## VHIPER EM preparation

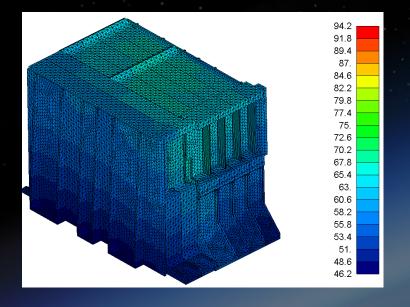

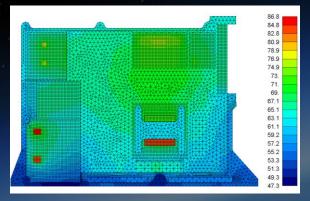

# Detailed thermal bord and equipment architecture

### **Boards layout**

# VHIPER EM preparation

a u 0