# OBC Simulator Architectures and Interfaces to System Test Benches (LeonSVF) GSTP + StrIn + Lab investment activity

progress presentation

Tehnical Officer: M.Caleno (TEC-SWS) Prime: Astrium SAS Toulouse/Airbus Consultant: Ingespace SARL (Toulouse) Subco: Terma AS (Copenhagen)

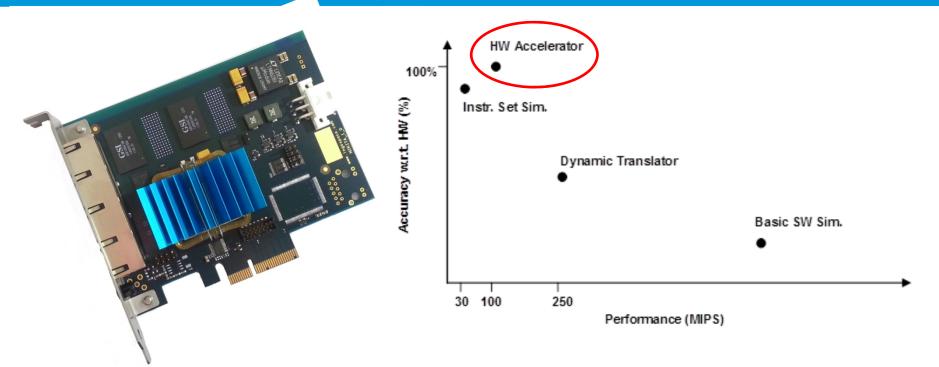

## Skipping to conclusions: Leon Emulation Board (LEB)

Do you need a Leon System on Chip emulator?

- 100% representative

- simulate in real time a S/C with OBC 60MHz+

- works in Eurosim, SimTG

- easy to integrate in your infrastructure

- easy to operate

- ...

### Leon Emulation Board !

## Skipping to conclusions: Leon Emulation Board (LEB)

#### Easy to tailor to another SoC

| LEON2<br>configuration                                                                                                                                                                                                                                                                                                                    | LEON3<br>configuration    | SCOC3-inspired<br>configuration<br>(extension of LEON3<br>config)                                              | Another<br>SoC ???? |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|

| - Leon2FT@100Mhz<br>- GRFPU                                                                                                                                                                                                                                                                                                               | - Leon3@100Mhz<br>- GRFPU | <ul> <li>Leon3@100Mhz</li> <li>GRFPU</li> <li>SpW packets:<br/>Leon ←→ Sim SW</li> <li>2 Amba buses</li> </ul> | Leon2FT? Leon3?<br> |

| <ul> <li>4+4MB Leon PROM/EEPROM</li> <li>16 MB Leon SRAM at 0 wait states</li> <li>64 MB SDRAM</li> <li>4+4 MB for fast simulation of I/O mapped memories</li> <li>SW Simulation on I/O and AMBA bus (APB and AHB)</li> <li>UART characters Leon ←→ Simulation SW</li> <li>Monitor and control of PIO, reset and watchdog pins</li> </ul> |                           |                                                                                                                |                     |

| <ul> <li>Scheduler and Timed Events</li> <li>GDB Server</li> <li>Save and Restore of simulation contexts</li> <li>API TSIM compliant (partly) plus extensions</li> <li>Runs in Eurosim (Dutch Space) and in SimTG (Airbus DS)</li> </ul>                                                                                                  |                           |                                                                                                                |                     |

## Agenda

- 1. Context and goals of the project

- a. from CPU to SoC emulation with HW-in-the-loop

- 2. Work logic and status

- 3. Leon Emulation Board (LEB)

- a. Functions, Leon2FT/Leon3, Performance

- b. Future: multicore? DSU4?

- 4. HW/SW Co-engineering and the SysC/TLM SpW model

- 5. SOIS in system simulation

- 6. Conclusions

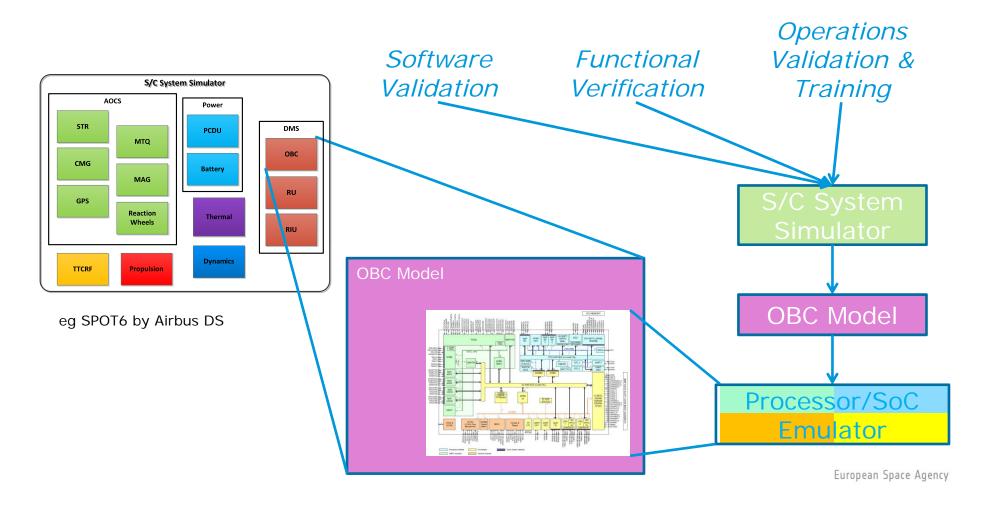

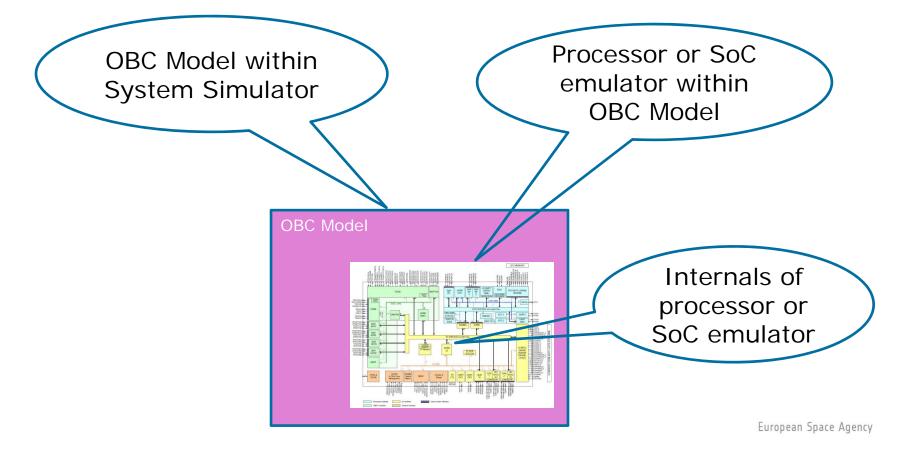

## Context

When actual OBSW flight image and/or CPU instruction set are required

### **Context: the project**

"OBC Simulator Architectures and Interfaces to System Test Benches"

Motive: Moving from processor emulators to System On Chip emulators

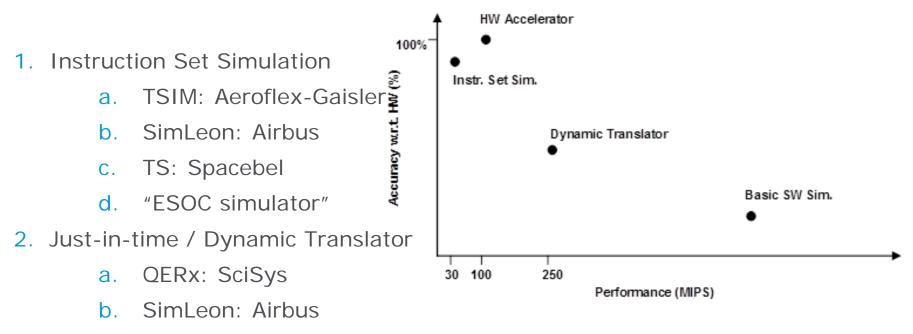

## **Context: processor emulation techniques**

- 3. Hybrid (HW and SW in the loop)

- a. LeonSVF/Leon Emulator Board: ESA, Airbus, Ingespace & Terma

- b. TSIM-HW: Aeroflex-Gaisler

- c. EPICA-next: TAS, Ingespace

- d. MAS281, DSP21020 ... ERC32: SHaM architecture by ESA & Chess

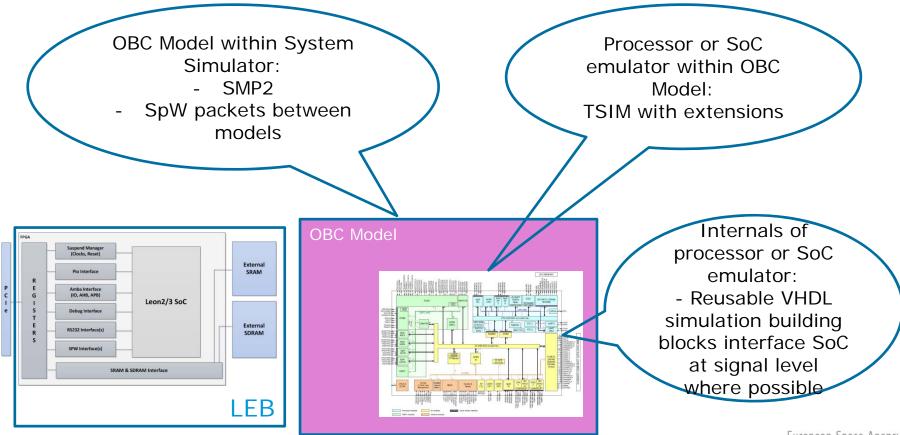

## **Context: Leon Emulation Board (LEB)**

#### **3.** Hybrid (HW and SW in the loop)

- a. LeonSVF/Leon Emulator Board: ESA, Airbus, Ingespace, Terma

- Leon Processor IP Core (HIL): actual VHDL runs in the FPGA

- Other IP Cores (HIL/SIL): in FPGA and in workstation

- I/O peripherals (SIL): simulated in workstation

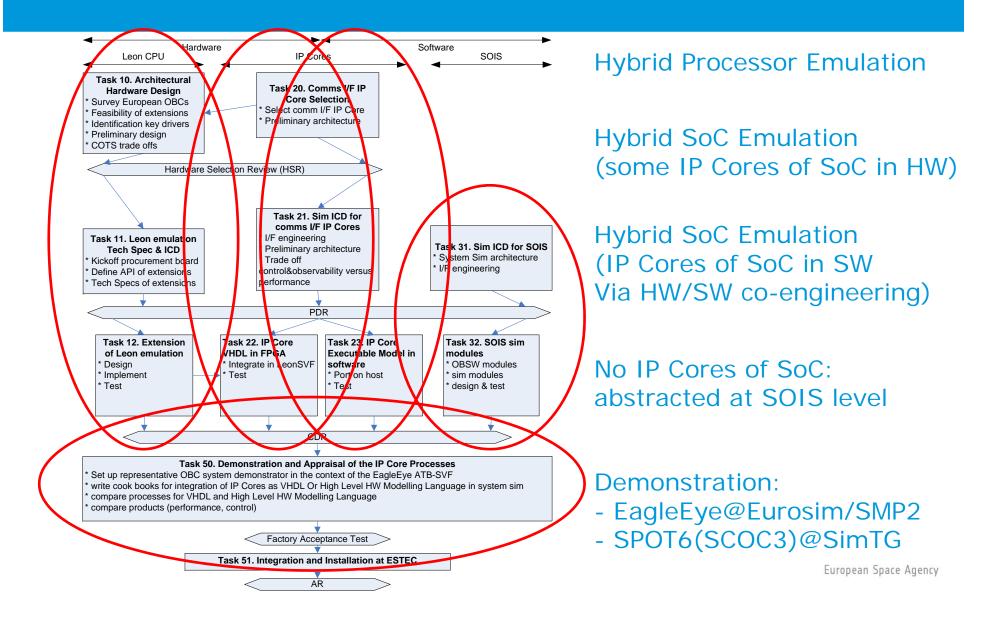

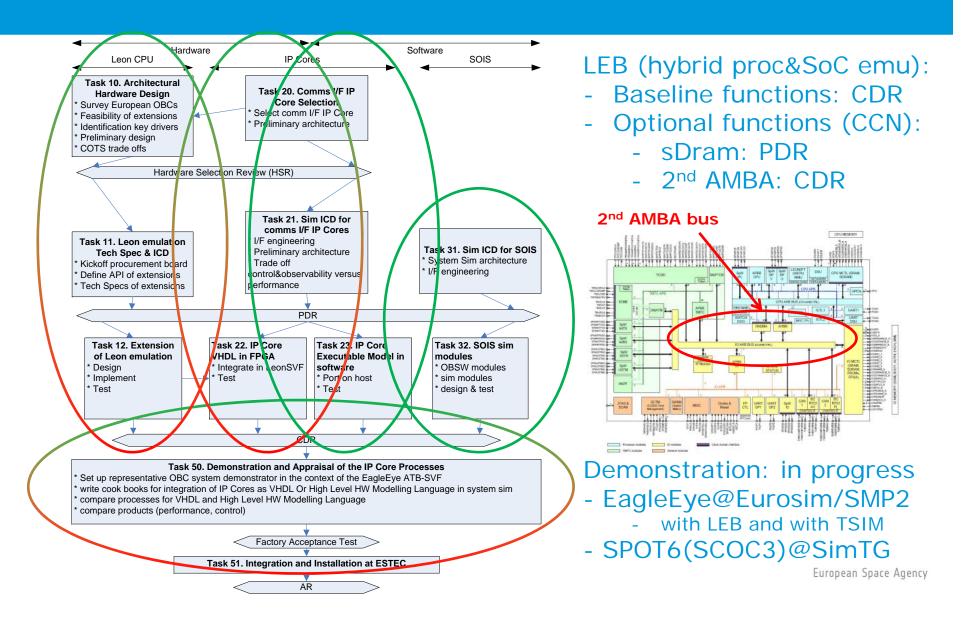

## **Project work logic**

### **Project status**

## **LEB: simulation functions**

| LEON2<br>configuration                                                                                                                                                                                                                                                                                                                                                           | LEON3<br>configuration    | SCOC3-inspired configuration (extension of LEON3 configuration)                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| - Leon2FT@100Mhz<br>- GRFPU                                                                                                                                                                                                                                                                                                                                                      | - Leon3@100Mhz<br>- GRFPU | <ul> <li>Leon3@100Mhz</li> <li>GRFPU</li> <li>SpaceWire packets Leon ←→ Simulation SW</li> <li>2 Amba buses</li> </ul> |

| <ul> <li>4+4MB Leon PROM/EEPROM</li> <li>16 MB Leon SRAM at 0 wait states</li> <li>64 MB SDRAM</li> <li>4+4 MB for fast simulation of I/O mapped memories</li> <li>SW Simulation on I/O and AMBA bus (APB and AHB)</li> <li>UART characters Leon ←→ Simulation SW</li> <li>Monitor and control of PIO, reset and watchdog pins</li> <li>Easy to tailor to another SoC</li> </ul> |                           |                                                                                                                        |

| <ul> <li>Scheduler and Timed Events</li> <li>GDB Server</li> <li>Save and Restore of simulation contexts</li> <li>API TSIM compliant (partly) plus extensions</li> <li>Runs in Eurosim (Dutch Space) and in SimTG (Airbus DS)</li> </ul>                                                                                                                                         |                           |                                                                                                                        |

## **LEB: simulation functions**

| LEON2<br>configuration                                                                                                                                                                                                                                                                                                                                                           | LEON3<br>configuration    | SCOC3-inspired configuration (extension of LEON3 configuration)                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| - Leon2FT@100Mhz<br>- GRFPU                                                                                                                                                                                                                                                                                                                                                      | - Leon3@100Mhz<br>- GRFPU | <ul> <li>Leon3@100Mhz</li> <li>GREPU</li> <li>SpaceWire packets Leon ←→ Simulation SW</li> <li>2 Amba buses</li> </ul> |

| <ul> <li>4+4MB Leon PROM/EEPROM</li> <li>16 MB Leon SRAM at 0 wait states</li> <li>64 MB SDRAM</li> <li>4+4 MB for fast simulation of I/O mapped memories</li> <li>SW Simulation on I/O and AMBA bus (APB and AHB)</li> <li>UART characters Leon ←→ Simulation SW</li> <li>Monitor and control of PIO, reset and watchdog pins</li> <li>Easy to tailor to another SoC</li> </ul> |                           |                                                                                                                        |

| <ul> <li>Scheduler and Timed Events</li> <li>GDB Server</li> <li>Save and Restore of simulation contexts</li> <li>API TSIM compliant (partly) plus extensions</li> <li>Runs in Eurosim (Dutch Space) and in SimTG (Airbus DS)</li> </ul>                                                                                                                                         |                           |                                                                                                                        |

## **LEB: simulation functions**

| LEON2<br>configuration                                                                                                                                                                                                                                                                                                                                                           | LEON3<br>configuration    | SCOC3-inspired configuration (extension of LEON3 configuration)                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| - Leon2FT@100Mhz<br>- GRFPU                                                                                                                                                                                                                                                                                                                                                      | - Leon3@100Mhz<br>- GRFPU | <ul> <li>Leon3@100Mhz</li> <li>GREPU</li> <li>SpaceWire packets Leon ←→ Simulation SW</li> <li>2 Amba buses</li> </ul> |

| <ul> <li>4+4MB Leon PROM/EEPROM</li> <li>16 MB Leon SRAM at 0 wait states</li> <li>64 MB SDRAM</li> <li>4+4 MB for fast simulation of 1/0 mapped memories</li> <li>SW Simulation on 1/0 and AMBA bus (APB and AHB)</li> <li>UART characters Leon ←→ Simulation SW</li> <li>Monitor and control of PIO, reset and watchdog pins</li> <li>Easy to tailor to another SoC</li> </ul> |                           |                                                                                                                        |

| <ul> <li>Scheduler and Timed Events</li> <li>GDB Server</li> <li>Save and Restore of simulation contexts</li> <li>API TSIM compliant (partly) plus extensions</li> <li>Runs in Eurosim (Dutch Space) and in SimTG (Airbus DS)</li> </ul>                                                                                                                                         |                           |                                                                                                                        |

## LEB: fundamental operational principle

- Simulated Real Time counter (SRT)  $\leftarrow \rightarrow$  Leon clock

- Leon clock & SRT are suspended/frozen when:

- OBSW accesses I/O

- OBSW accesses AMBA

- SoC Tx/Rx a SpW packet / UART character / PIO pin toggles...

- Simulation Time Events expires

- LEB calls back simulation SW via the PCI express bus (comm overhead)

- Simulation SW do their work:

- provide data to / retrieves data from SoC (I/O, AMBA, RAM...)

- Raise interrupts...

- Leon clock & SRT are resumed

- ... and so on...

## **LEB:** Performance

| example                                                                         |          |

|---------------------------------------------------------------------------------|----------|

| n. APB AMBA read / sSRT<br>(suspend on PClexpress)                              | 5,000    |

| n. APB AMBA write / sSRT<br>(suspend on PClexpress)                             | 5,000    |

| n. time events/sSRT<br>(suspend on PClexpress)                                  | 1,000    |

| throughput simulations → I/O<br>mapped memory (across PClexpr)<br>[KBytes/sSRT] | 130 KB/s |

| throughput simulations ← I/O<br>mapped memory (across PClexpr)<br>[KBytes/sSRT] | 130 KB/s |

| max OBC Frequency<br>while real time [Mhz]                                      | 68 Mhz   |

sSRT = second of simulated time

## **LEB:** performance

#### Stress Test : Airbus DS SCOC3 Simulation with small OBSW derived from SPOT6

| Suspend Cause               | Average number<br>of occurrences<br>per second SRT |

|-----------------------------|----------------------------------------------------|

| Read into I/O Suspend Area  | 3452                                               |

| Write into I/O Suspend Area | 867                                                |

| Amba Slave APB read         | 65                                                 |

| Amba Slave APB write        | 65                                                 |

| Amba Slave AHB read         | 1                                                  |

| Amba Slave AHB write        | 1                                                  |

| UART Byte sending           | 2                                                  |

| Timed event trigs           | 70                                                 |

| SPW packet emission         | 7521                                               |

| Time Windows                | 128                                                |

More than 12 000 suspend per second

60Mhz OBC Simulation run in real-time

| Read/Write Accesses on I/O Space | Data rate  |

|----------------------------------|------------|

| OBSW read to IO Exclusion Area   | 8.12 MB/s  |

| OBSW write to IO Exclusion Area  | 16.79 MB/s |

| OBSW read to IO Suspend Area     | 13.52 kB/s |

| OBSW write to IO Suspend Area    | 13.44 kB/s |

OBC Simulator Architectures and Interfaces to System Test Benches

## HW/SW Co-engineering

- 1. HW-engineer and SW-engineer cooperate on a single model (e.g.) of a functional block within a System On Chip

- 2. Used pre-existing SpaceWire SystemC/Transaction Level Model

- 3. Issues irrelevant to the goal of the SoW impaired the activity:

- a. Documentation hard-to-read

- b. HW/SW interface missing (the model targets the co/dec) → need to re-try with both goals in mind, HW-engineering, SWengineering

- c. could have reinterfaced  $\rightarrow$  performance certainly poor for SVF

- d. pushed out in favour of other key goals

- 4. Conclusion: need to try again

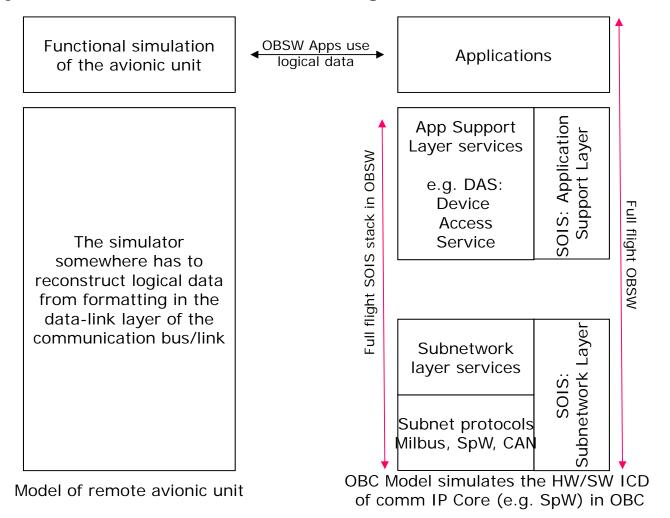

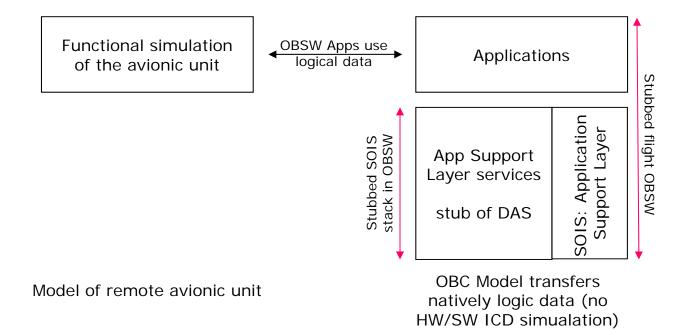

## Interfaces: ignore IP Core, cut&simulate SOIS (1/2)

Can system simulator take advantage of SOIS-based OBSW in OBC?

European Space Agency

## Interfaces: ignore IP Core, cut&simulate SOIS (2/2)

Conclusion: we can swap between full OBSW&Payload and stubbed OBSW&Payload in the EagleEye@Eurosim.

Works in progress...

## Conclusions

- 1. The Leon Emulation Board is

- a. a mature product for processor and SoC HIL emulation

- b. a building block for system simulators (SVF, FV, Ops Sim)

- c. representative (real Leon VHDL)

- d. high-performance: 60 MHz in real time in representative load

- e. TSIM compatible, works in Eurosim & SimTG

### 2. Please contact me if you want to try out an LEB

- 3. LEB-ecosystem: mature and attractive technology for SoC simulation

- a. will be even richer at next FPD

- b. reusable blocks to tailor LEB easily to specific SoC

- c. Multicore? FPGA-in-the-loop (LEB) or ASIC-in-the-loop

- 4. HW/SW co-engineering: to be tried again

- 5. SOIS stack offers convenient cuts in the simulators for high-level early software validation (nothing really new)