# Public Discussion / AOB All

### **Public Discussion**

#### **Proposed Discussion Topics**

- SSDP: priorities / schemes for software developments

- NGDSP: modified requirements and new IP for next attempt

- DSP IP vs. DSP ASIC vs. DSP hard IP in FPGA

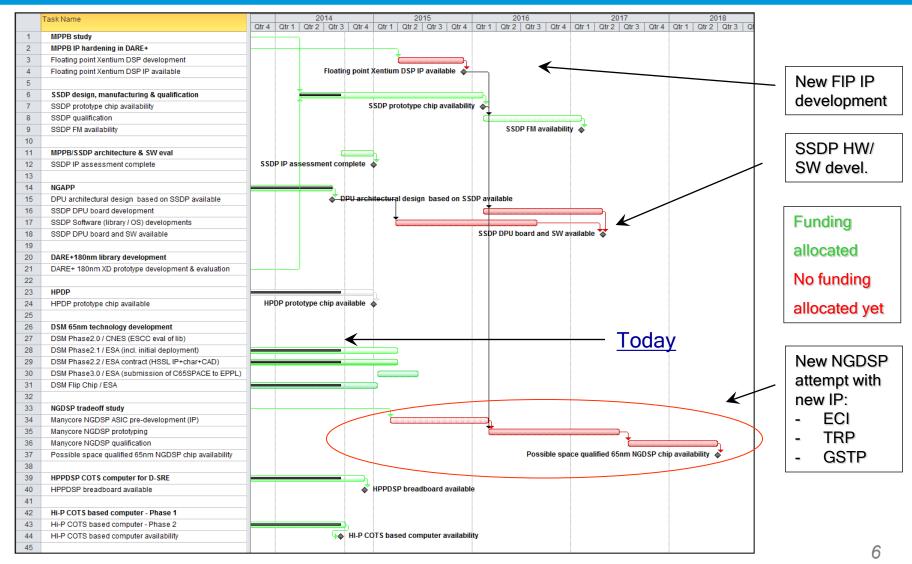

- Feedback on updated ESA roadmap

- AOB

### **Public Discussion - SSDP SW**

#### **Discussion: SSDP Software Priorities & Concepts**

- Problem: available software / DSP libraries for SSDP are much more limited in comparison to what we are used from COTS products

- Proposal: pool resources from ESA-funded and other SSDP related activities, provide DSP kernels developed in such activities to community via

- Implementation: provide DSP kernels under ESA OSS license: Open for ESA member state users, non-infective = can be combined with own software in products.

- First case: NGAPP "AlgoLib", developed by RSA / Univie. Contractors <u>agreed</u> to provide DSP kernels under ESA OSS license => good example to follow.

- **Issues to solve:** quality, optimization/performance, documentation => proposed that ESA does that via dedicated contracts.

- Your opinion ?

### Public Discussion — new NGDSP

#### Discussion: NGDSP – modified requirements and new IP for next attempt

- Problem: COTS IP assessed for NGDSP turned out to be not suitable (ATMEL Diopsis) / not licensable (TI6727)/ not affordable (ADI 21469). Need for high performance floating point DSP continues to exist. Current fix is large / expensive FPGAs and specific ASICs.

- Consequence of delays: ECI4 money (600k) was re-allocated to DDR2 IP development (good and bad at the same time), original goal of >1 GFLOP insufficient, new suitable IP needs to be found.

- New facts: SSDP development ongoing, RECORE IP matured and hardened, floating

point Xentium IP can be developed with acceptable effort and <u>dedicated activity</u>

proposed in TRP for approval at next AC (issue: Geo-return ... AI)

- <u>Proposal / ESA position</u>: develop floating point Xentium version, incorporate DSP IP in ESA IP portfolio for supporting future developments, <u>proceed with manycore floating point DSP development</u>, taking advantage of the <u>LEONx/SSDP/NGDSP family approach for software and IP</u>

- Your opinion ?

### Public Discussion — DSP ASIC, IP, hard IP

#### Discussion: DSP IP vs. DSP ASIC vs. DSP hard IP in FPGA

- At ADCSS 2007 industrial participants voiced desire to have the ESA (NG)DSP IP also available as licensable IP, or IP as part of ESA IP portfolio, available for their own developments

- SSDP: DSP IP (including NoC, bridges, SDE) is licensable from RECORE b.v.

- Proposed FP DSP IP development (AI) with RECORE b.v. is also aiming at incorporation of fixed + floating point DSP IP in ESA IP portfolio (supporting prototyping / TRP work), with defined conditions for support packages and FM development licenses for other projects.

- Your opinion ?

- Future options: DSP as hard IP in future European large FPGA. Would allow

efficient integration of software programmable backend with very fast data

processing frontends (instrumentation, GPS, accelerated specific computations etc.)

- Your opinion ?

### Public Discussion - Updated ESA DSP RM

### ESA DSP Day 2014 — The End

## Thank You!

FYI the presentations will be posted on the DSP day 2014 website:

http://space-env.esa.int/indico/conferenceDisplay.py?confld=60

ESA & TEC-EDP wish you a good evening & safe return.