# R2RAM 640073 H2020 Project

Cristiano Calligaro RedCat Devices - c.calligaro@redcatdevices.it

# Outline

R2RAM Consortium

R2RAM Goals

R2RAM Technology

R2RAM Test Vehicle

R2RAM Testing approach

#### Workshop on Memristive Systems for Space Applications, ESTEC - April 30 2015 3

**R2RAM** Consortium

The IHP is an institute of the Leibniz Association and conducts research and development of silicon-based systems and ultra high-frequency circuits and technologies including new materials. It develops innovative solutions for application areas such as wireless and broadband communication, aerospace, biotechnology and medicine, automotive industry, security technology and industrial automation.

Key Person and Project Coordinator: Christian Wenger

IUNET (Italian Universities Nano-Electronics Team), is a non-profit Organization, aimed to lead and coordinate the effort of the major Italian university teams in the field of silicon-based nanoelectronic device modelling and characterization. Current members of IUNET are the Universities of Bologna, Calabria, Ferrara, Modena e Reggio Emilia, Padova, Pisa, Udine, Roma "La Sapienza" and the Politecnico of Milano. Key Person: Prof. Piero Olivo

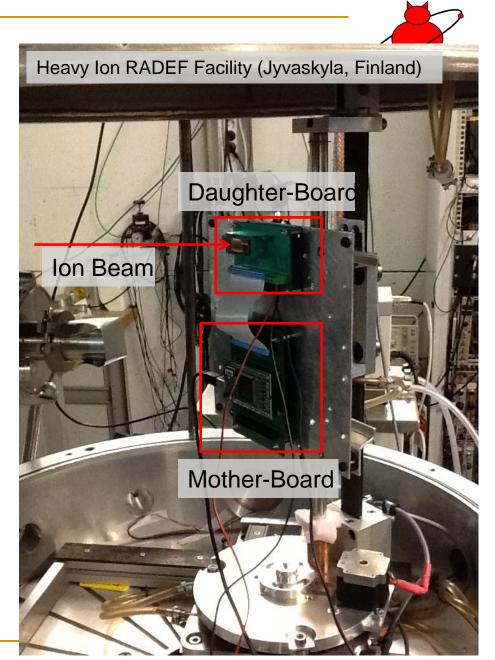

The University of Jyväskylä (JYU) is one of the largest universities in Finland. Department of Physics (JYFL) of the university belongs to the Faculty of Mathematics and Science. Accelerator laboratory of JYFL has operated very successfully as one of the Large Research Access Infrastructures in the FP4 - FP7 programmes of the EU since 1996 (ENSAR for 2013-2014) and acted as a FP5 Marie Curie Training Site. Since 2005 laboratory's RADiation Effects Facility, RADEF has been qualified to one of the External European Component Irradiation Facilities of European Space Agency, ESA. Key Person: Prof. Ari Virtanen

RedCat Devices (RCD) is a privately held fabless semiconductor company involved in several fields of research concerning memories (volatile and non volatile), analog components (ADCs, DACs) and standard digital libraries for special applications. In the last eight years RCD has been involved in several R&D projects including FP7 262890 SkyFlash in the role of coordinator. Key Person: Cristiano Calligaro

Development and design of a radiation hard non-volatile memory technology by using standard CMOS silicon processing.

#### New R<sup>2</sup>RAM approach:

Using the Resistive random-access memory (RRAM) technology

#### www.r2ram.eu

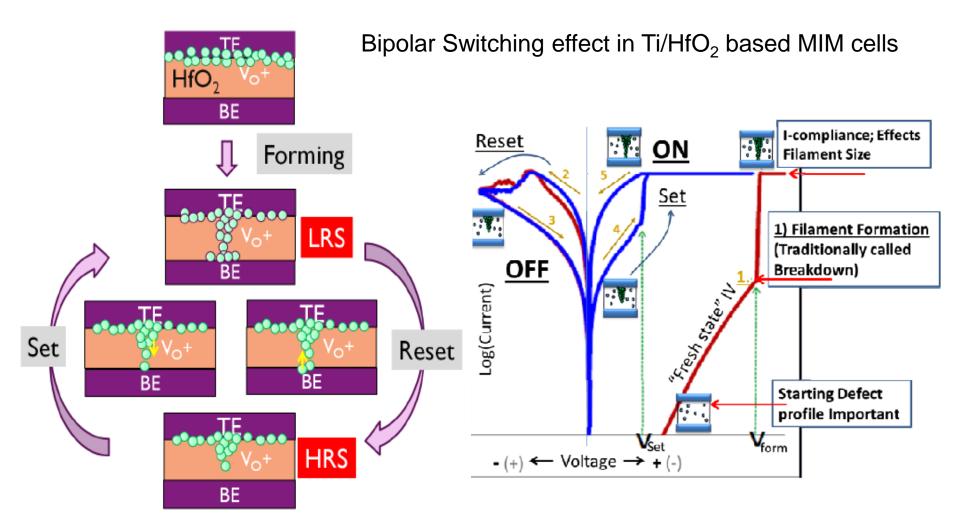

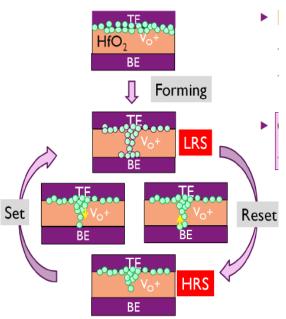

#### R2RAM Technology

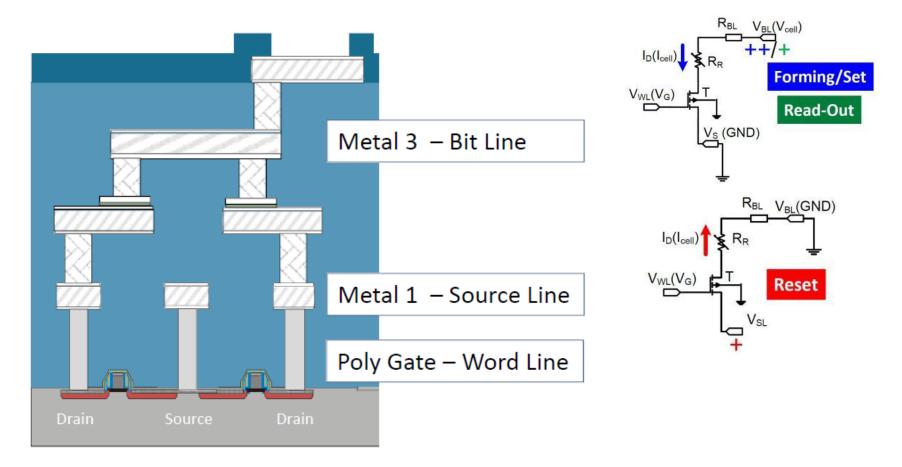

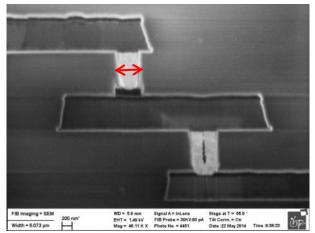

#### Schematic 1T1R Device

#### TiN/HfO<sub>2</sub>/Ti/TiN 1T1R Devices:

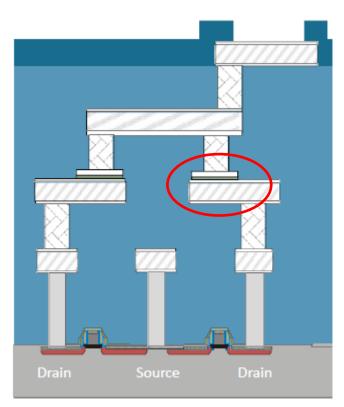

#### Schematic 1T1R Device (Integration Issues)

3. Final anneal at 400 °C for 30 min

#### 1. Cell size: > 500 nm

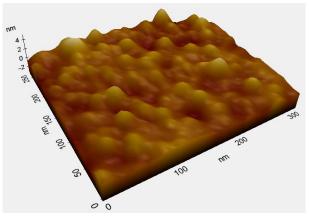

#### 2. Surface roughness of Met 2: > 2 nm

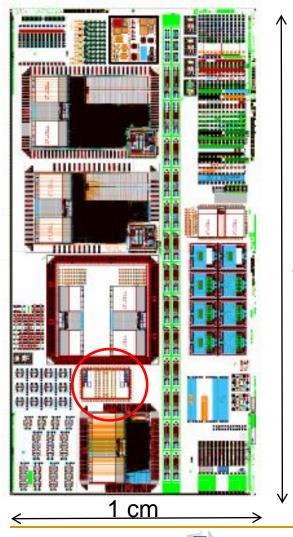

## MPW Approach

#### **Testfield 284**

#### Cost sharing (Multi Project Wafer):

Every circuit designer is using the same design kit

Process flow is equal until finalized Metal 2, split of RRAM wafers

2 cm

2020

#### **Required additional process steps:**

- HfO<sub>2</sub> deposition by CVD or ALD

- Ti/TiN deposition by PVD

- TiN/Ti/HfO<sub>2</sub> etching by RIE

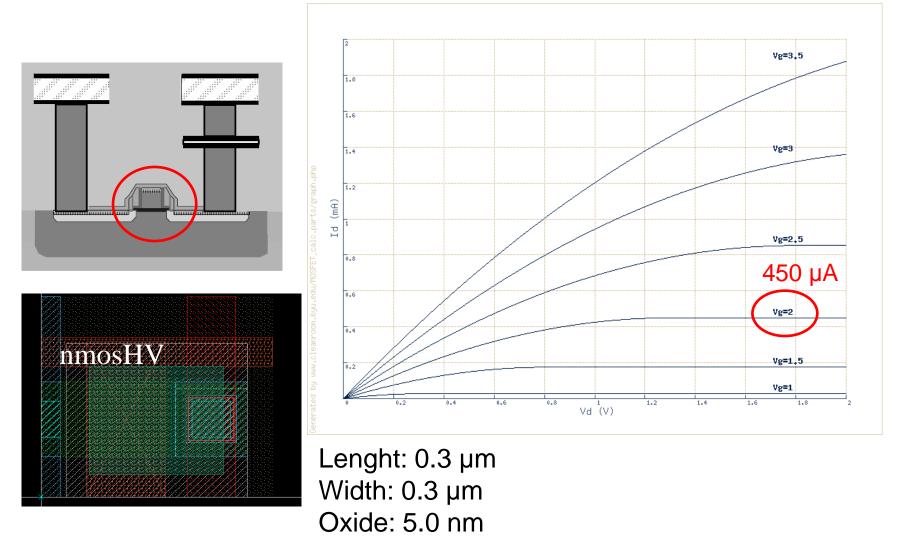

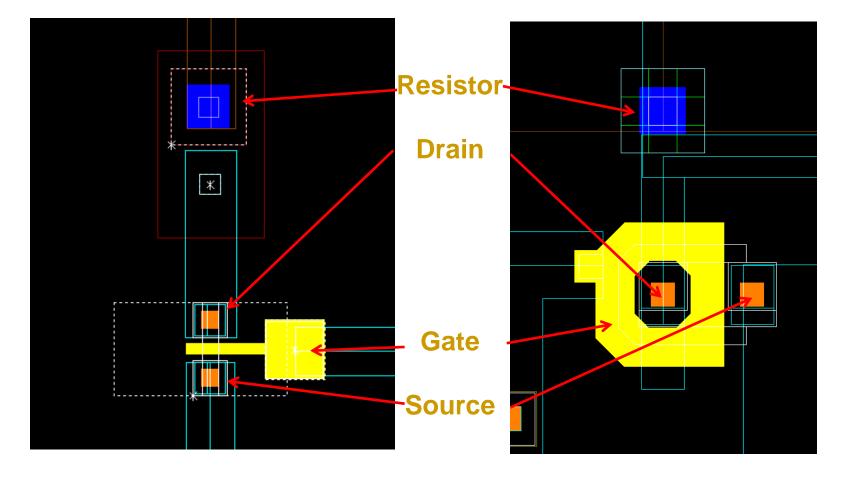

#### Choice of NMOS Select Transistor

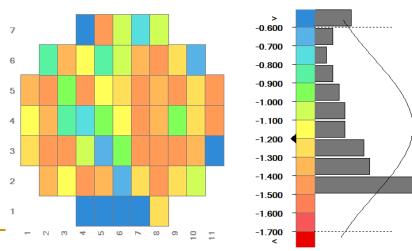

## Yield poly-christalline HfO<sub>2</sub>

**R<sup>2</sup>RAN**

HORIZON 2020

Reset

Set

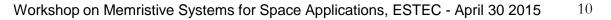

#### Endurance of single 1T1R device

Stable endurance for poly HfO<sub>2</sub>

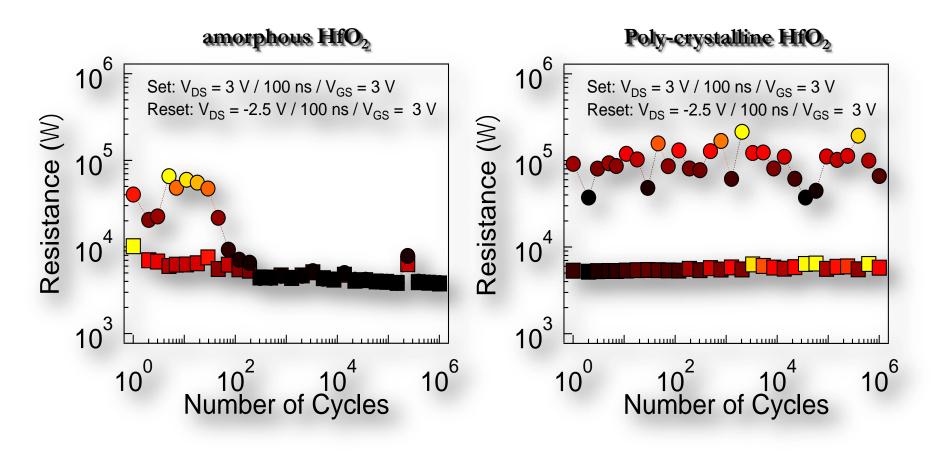

#### 4Kbit Test Vehicle (200mm wafer, 0,25 µm)

#### 4Kbit Test Vehicle (Test at Univ. Ferrara)

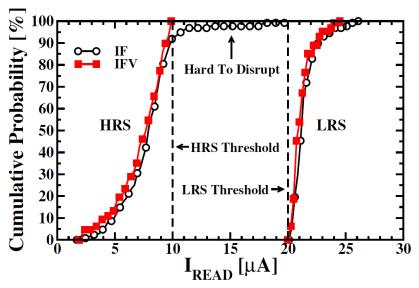

Incremental Form and Verify (IFV):

4kbit array

Workshop on Memristive

New rad-hard 1T1R design

#### Standard cell:

## Rad-hard cell:

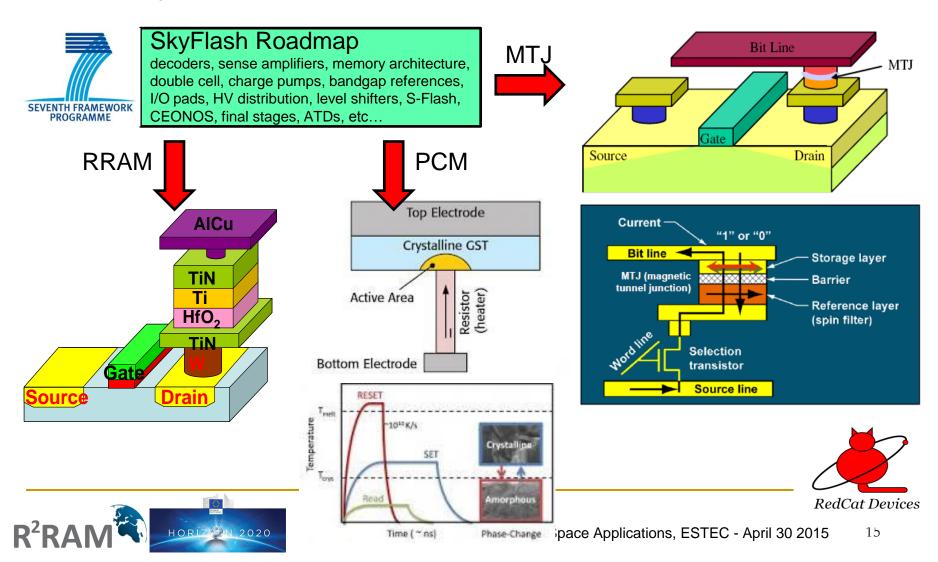

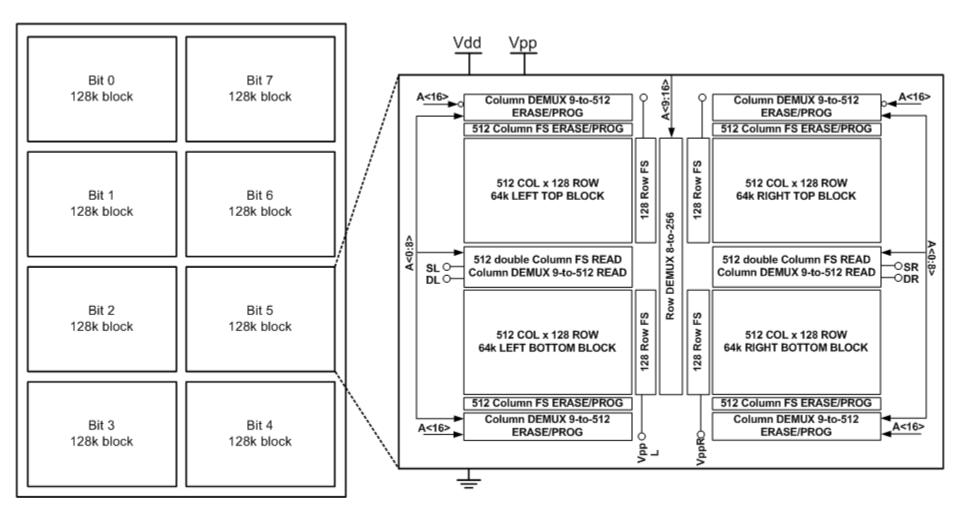

### R2RAM Test Vehicle (The SkyFlash heritage)

• SkyFlash has been focused on Nitride Flash cells but many blocks are in common with others NVM technologies.

#### SkyFlash Test Vehicles

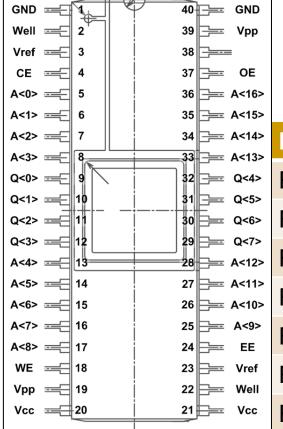

# 1Mbit (128kbit x8)

$\odot$

HORIZ N 2020

R<sup>2</sup>RA

| Ň  |      |  |

|----|------|--|

|    |      |  |

|    |      |  |

| 1  |      |  |

| 17 | //-/ |  |

| ≕ A<15>            |                |                                                         |

|--------------------|----------------|---------------------------------------------------------|

| ≕ A<14><br>≕ A<13> | Prototype Code | Description                                             |

| ≕ Q<4>             | RC27F1024SKY1  | 1Mbit OTP with external HV                              |

| ■ Q<5> ■ Q<6>      | RC27F1024SKY2  | 1Mbit OTP with internal charge pump                     |

| ≕ Q<7><br>≕ A<12>  | RC27F1024SKY3  | 1Mbit OTP with internal charge pump and reference array |

| ≕ A<11><br>≕ A<10> | RC27F1024SKY4  | 1Mbit OTP with internal charge pump and bgref           |

| == A<9>            | RC27F1024SKY5  | 1Mbit OTP with charge pump for erasing                  |

| == Vref<br>== Well | RC27F1024SKY6  | 1Mbit OTP refinement of SKY5                            |

| == Vcc             | RC28F1024SKY1  | 1Mbit NVM based on SKY4 (CEONOS replacement)            |

#### From NROM to ReRAM 1/2

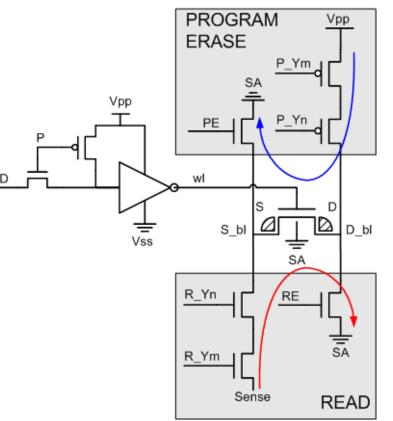

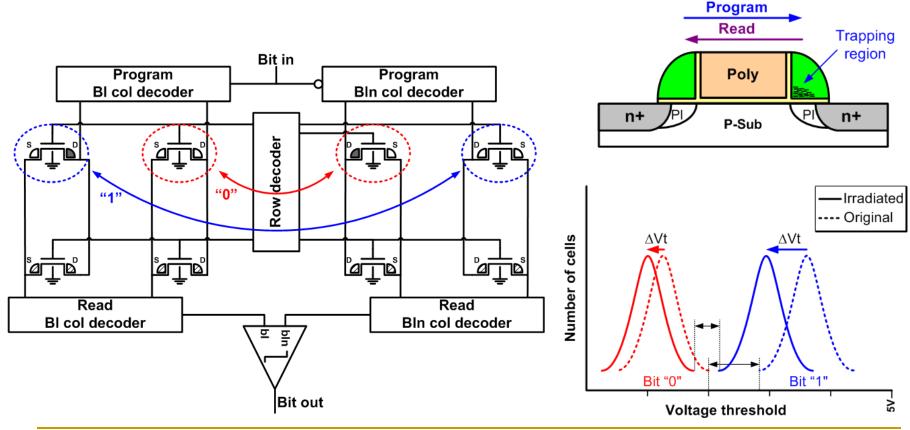

Cell program and erase is based on hot carrier mechanism (CHE) and hot holes generated by band-to-band (BTB) tunneling. The injection of charge in the nitride produces a shift on the threshold voltage. The programming is done from the drain side with voltages of 5-6V using 3.3V transistors.

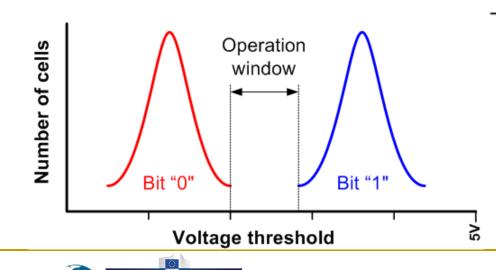

Each bit is represented with different  $V_{th}$  and the distance between them is the operation window. Reading is done on the reverse direction of programming (source), allowing to separate high voltage circuitry from the reading stage.

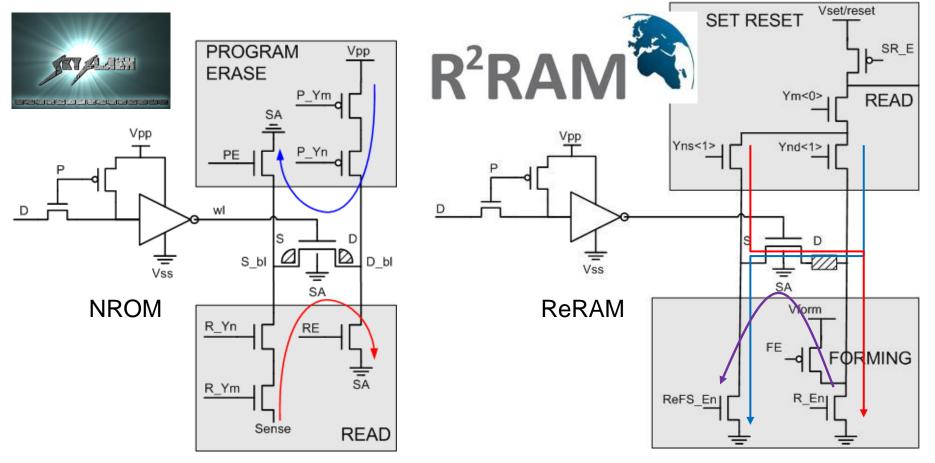

#### From NROM to ReRAM 2/2

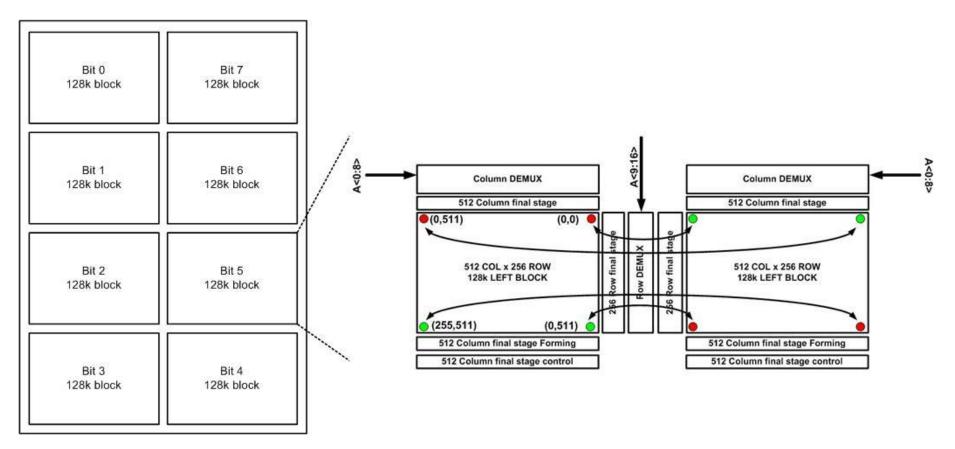

Despite the differences between the two cells, the main goal is to maintain the same architectural approach in the test vehicle

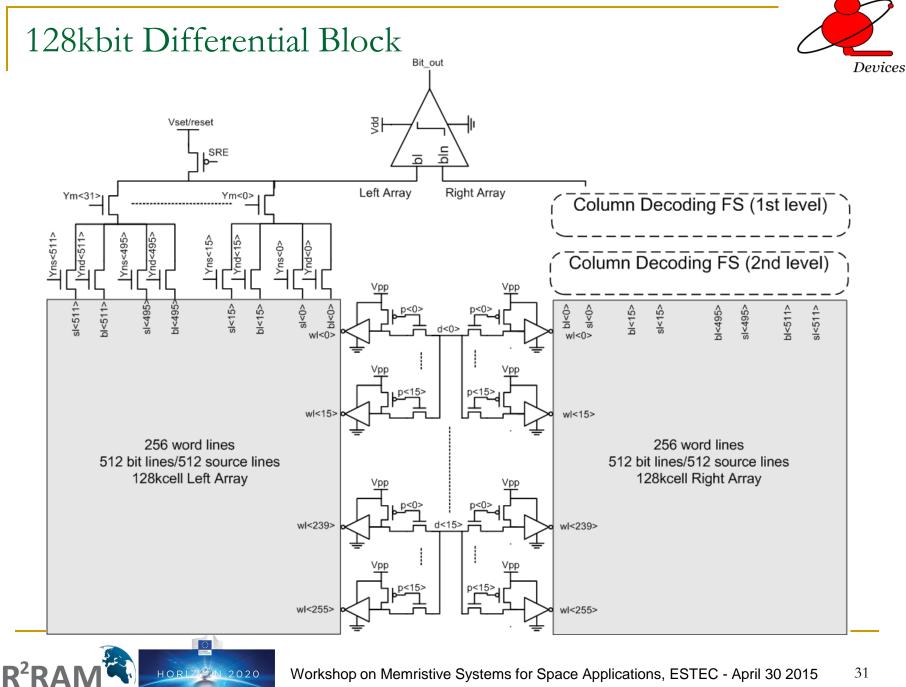

#### Differential Cell Approach (2 cells for 1 bit)

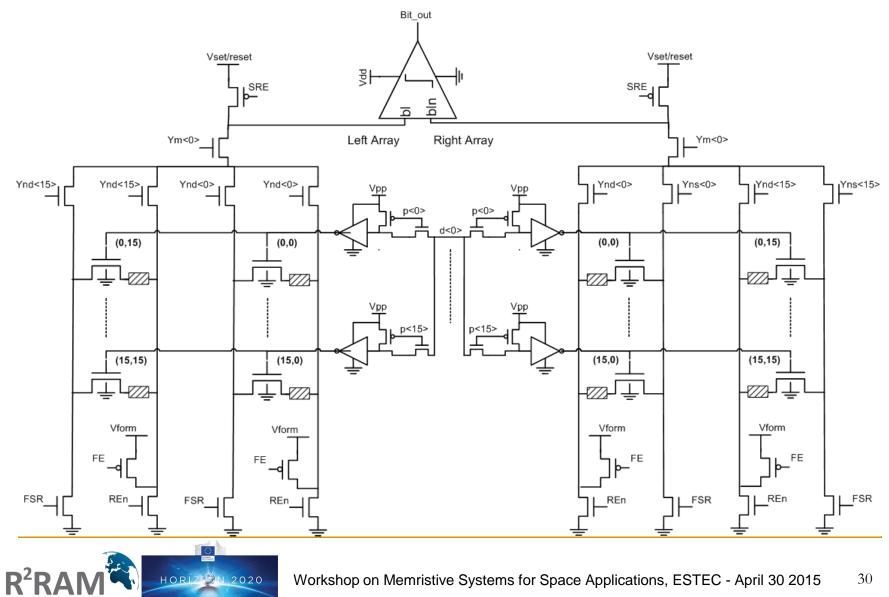

Two cells corresponding to the single bit are placed in two independent arrays. The minimum distance between the two cells of the bit is  $70\mu m$  (length of row decoding scheme).

1.1.2.

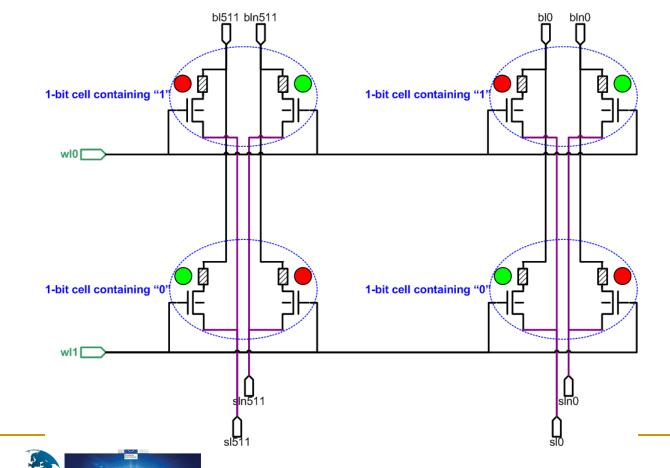

#### Differential Cell in R2RAM

The differential approach in memory array foresees a low resistance cell on the left and a high resistance cell on the right. We call this status "1". Vice-versa for "0". This architectural approach does not require <u>ANY</u> reference cell.

#### SkyFlash 1Mbit (RC27F1024SKYn)

ومراجع بلاز الارتجار بلاز الفراجع الارتجار

#### R2RAM 1Mbit (RC28F1024R2RAMn)

The independence of each bit (independent final stages, ATDs, etc...) guarantees resistance to MBUs.

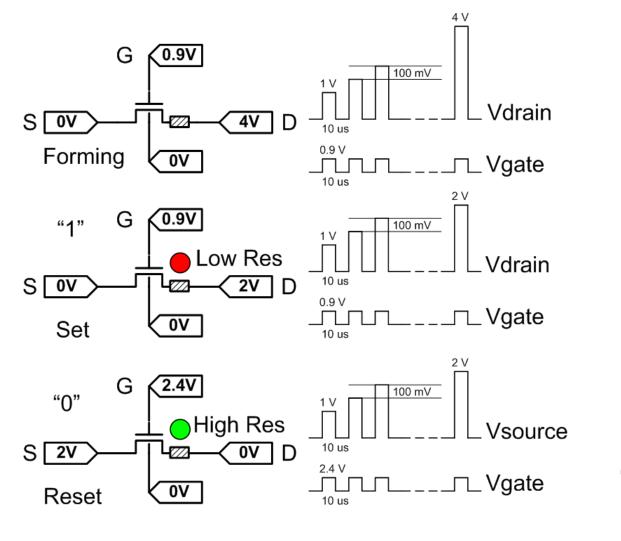

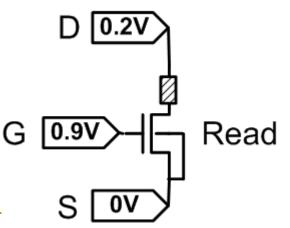

#### ReRAM Cell Working Conditions

Z 🖉 N 2020

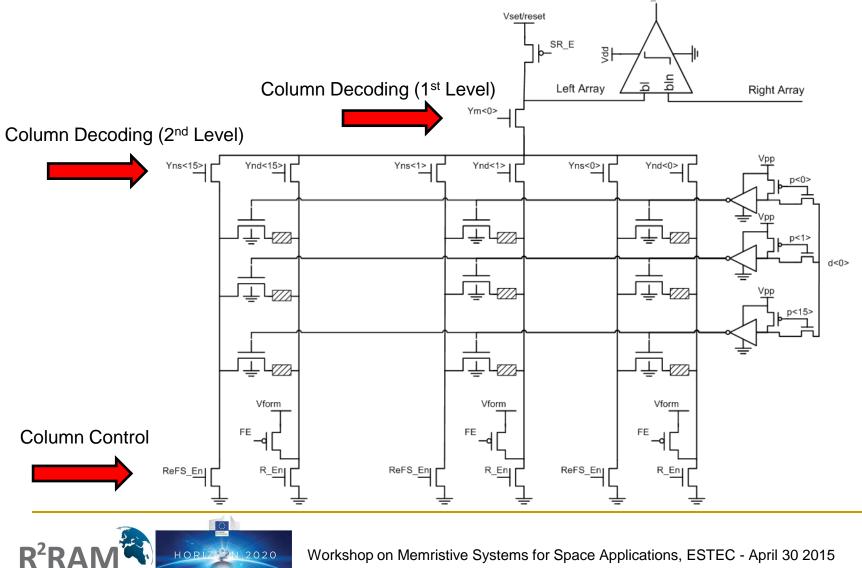

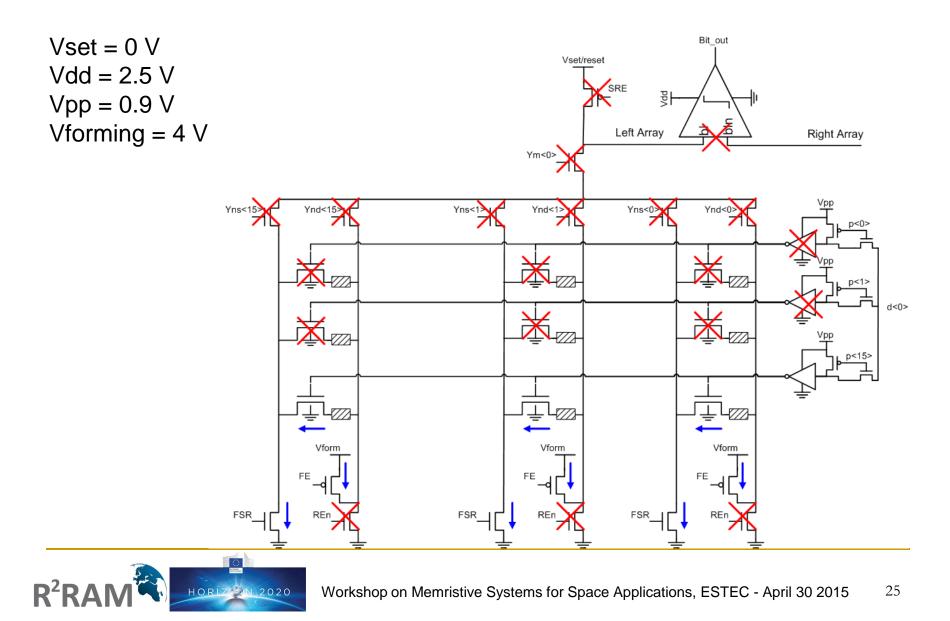

#### Architectural Approach (16 x 16 Bank)

Bit out

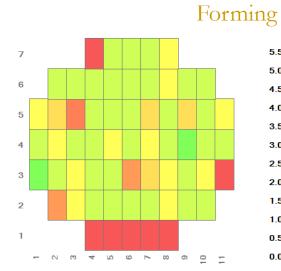

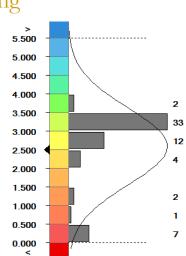

#### Forming Mode (row by row)

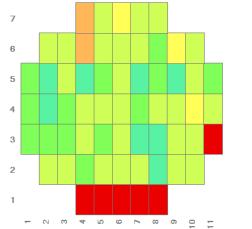

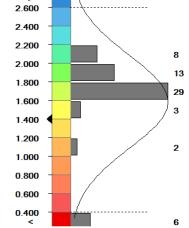

Reset Mode

**R<sup>2</sup>RAN**

Z ON 2020

Bit\_out Vreset = 2 VVset/reset Vdd = 2.5 VSRE Vpp = 2.4 V Pp Left Array **Right Array** Ym<0> Yns<0 Yns<15> Yns<1 Ynd<1 Ynd<0 Ynd≼ p<1> d<0> p<15> Vform Vform Vform FE FE FE FSR FSR REn REn FSR REn

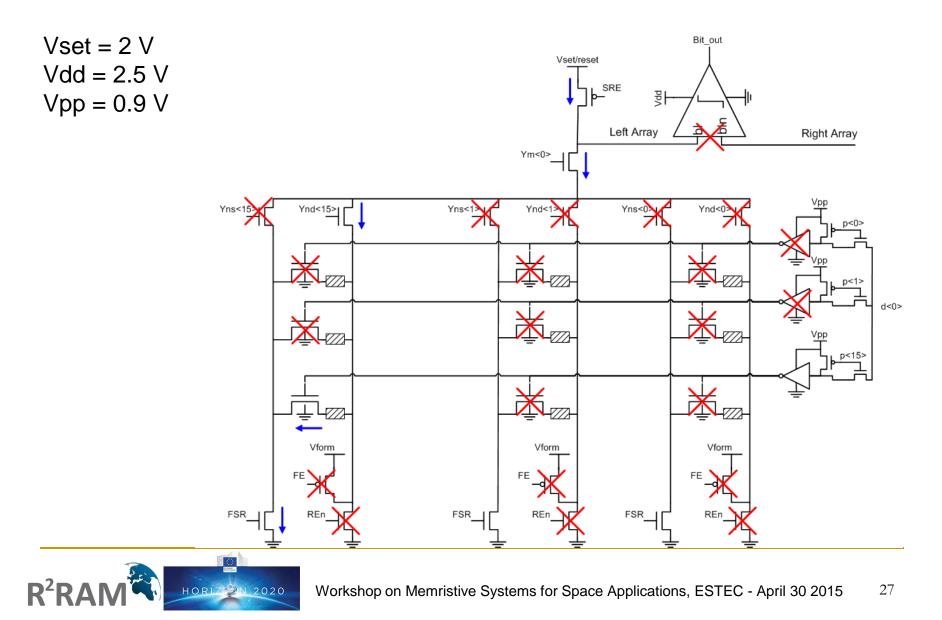

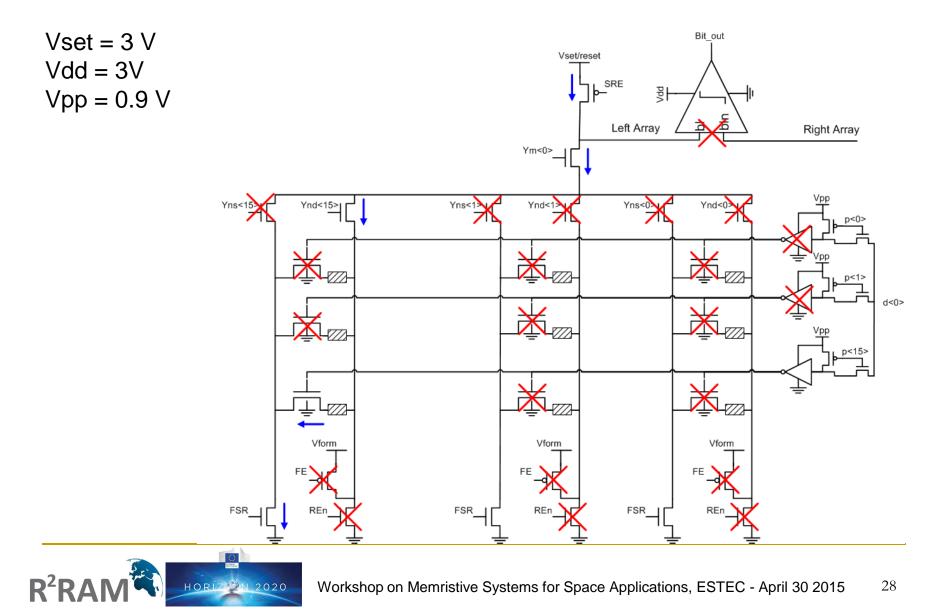

Set Mode

#### Forming Mode (cell by cell)

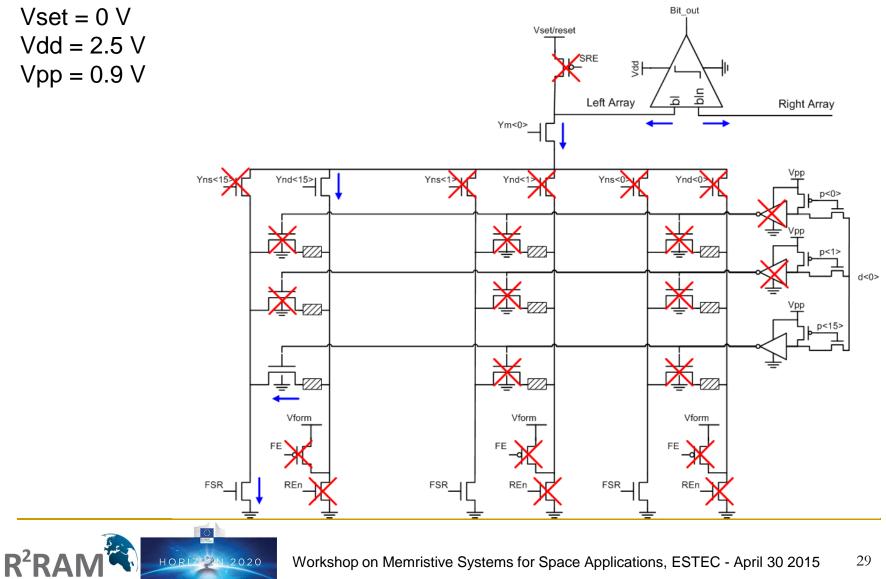

Read Mode

### 16 x 16 Differential Bank

HORIZON 2020

2020 N 2020

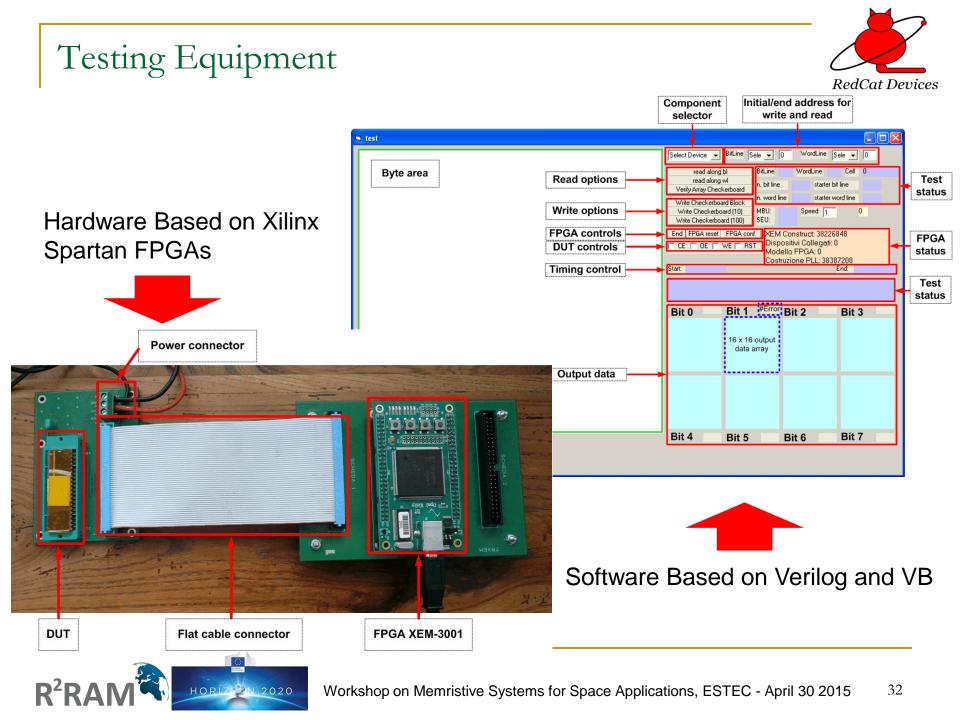

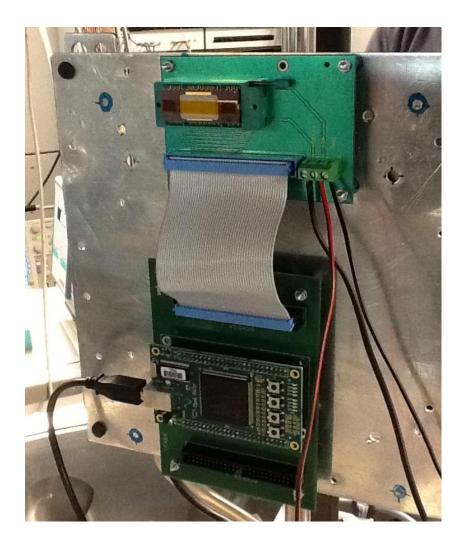

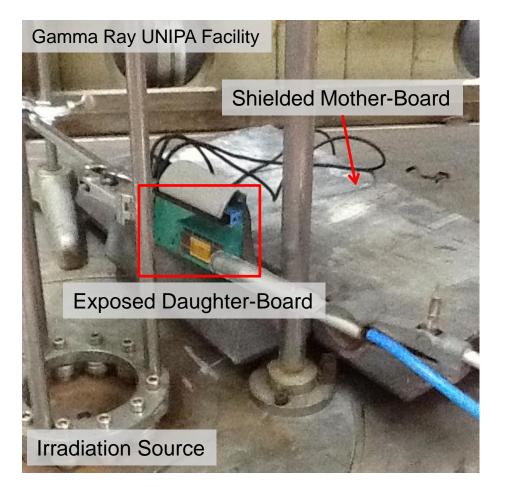

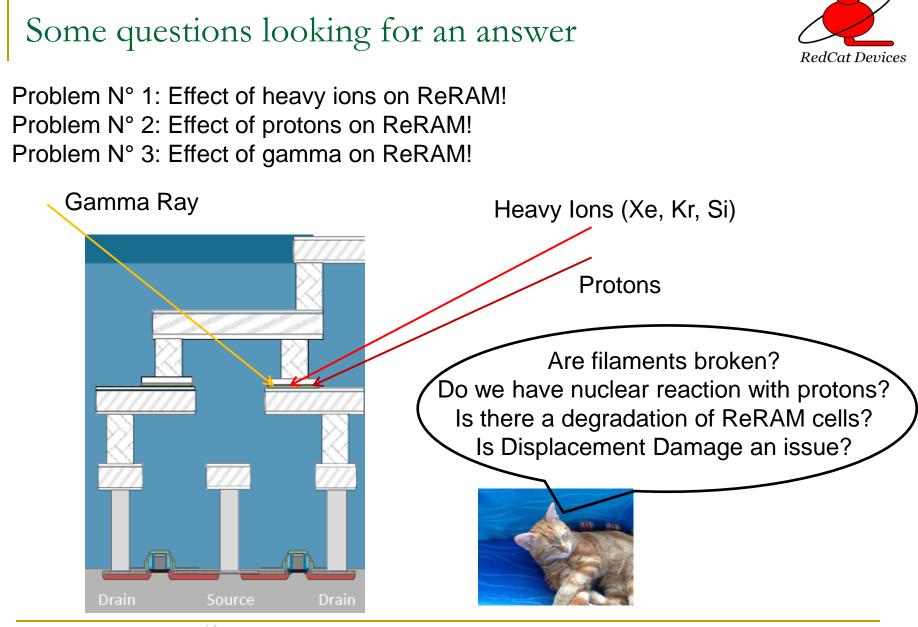

# Testing Equipment (SEE)

## Testing Equipment (TID)

# Thanks for your Attention!!