Speaker

Description

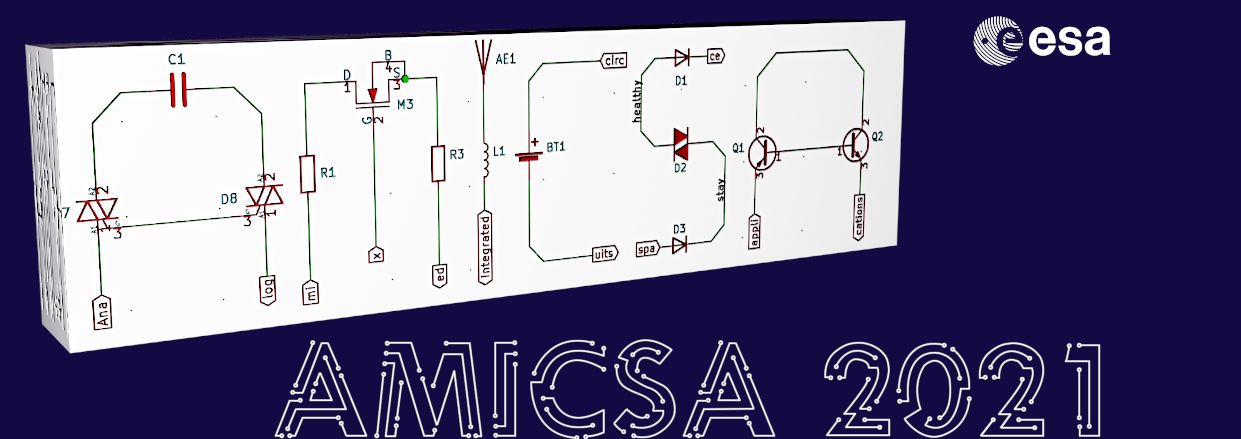

In contrast to a pure digital ASIC design flow, which is highly regarded as a top-down design methodology, building an analog mixed-signal complex function usually requires a bottom-up design approach. The latter is based traditionally on a full custom design approach where each functional analog block, after it has been individually designed and verified, it is integrated at a higher level to form the desired electronic function in silicon. Next, the radiation tolerance or hardening of the mixed-signal ASIC is evaluated in silicon as a whole. In 2015, ESA-ESTEC launched the ITT7794, a collaborative industrial R&D program aiming at demonstrating the capability of building radiation hardened (rad-hard) complex mixed-signal analog functions from pre-verified elementary circuit blocks. This approach would otherwise enable a top-down design methodology for mixed-signal rad-hard ASICs that would significantly speed up the design process with a high level of confidence in terms of radiation hardening of the target electronic function. In the frame of the project, a library of rad-hard analog mixed-signal IP blocks has been developed in the ATMX150RHA 150nm CMOS-SOI technology offered by MicrochipTM, by following a rigorous design methodology and a variety of hardening techniques both at design and layout levels. A number of instances from each IP block were laid out on a common silicon substrate in the form of a packaged Technology Characterization Vehicle (TCV) and characterized both electrically as well as against Total Ionizing Dose (TID) and Single Event Effects (SEE) using a heavy-ion cocktail.

We hereby present the results from the electrical verification as well as the radiation testing of each IP block as those obtained from the stand-alone verification of each IP block performed on the TCV. A total number of twelve (12) analog IP blocks were included in the library as implemented on the TCV and presented in Table 1.

Each IP block was electrically characterized over -40°C to 125°C junction temperature range, and over the specified operating voltage range of 3.3V±10% and 1.8V±10% for the analog and the digital parts respectively. The functionality and electrical performance of the IPs was tested in a radiation environment of up to 300 krad (Si) Total Dose at the high dose rate window of 3.6 krad/h and a maximum LET of 62.5 MeV/mg/cm2 using heavy-ions, exhibiting no hard fail or latch up and with minor performance drifts.