Speaker

Description

Jan Steinkamp1, Frank Henkel1 , Volker Lück2, Dr. Ralf Symanczyk2

1 IMST GmbH, Carl-Friedrich-Gauss-Str.2-4, 47475 Kamp-Lintfort, Germany

2 TESAT-SPACECOM GmbH & Co. KG, Gerberstraße 49, 71522 Backnang, Germany

IMST and TESAT-Spacecom are working together in a DLR funded R&D project on the establishment of a qualified Mixed-Signal ASIC supply chain for space applications. This project is aimed to achieve the capability approval for IMST as a qualified manufacturer given by the ESCC at the end of 2020.

The capability domain covers the design, manufacturing, inspection, test procedure and screening of the ASIC together with a quality control and traceability procedure.

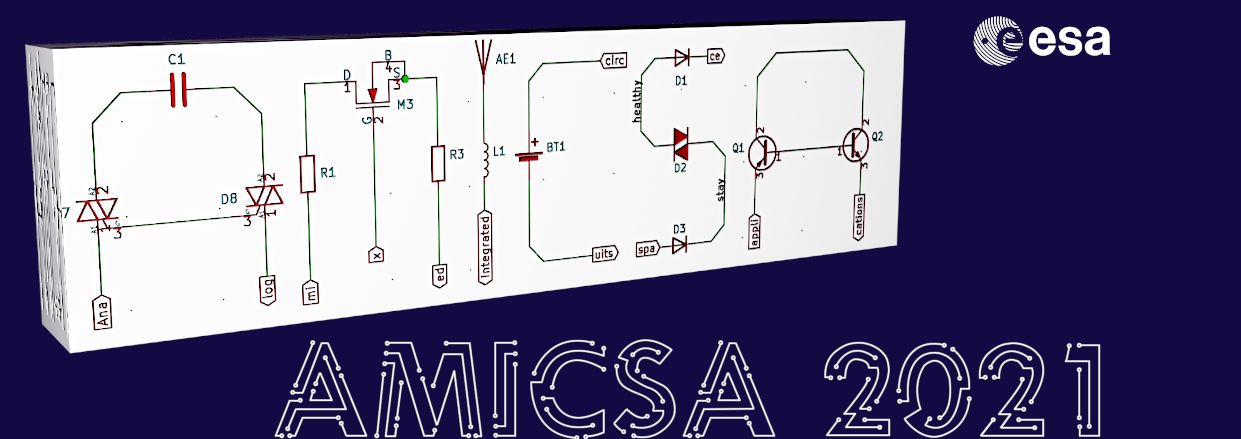

The ASIC design is based on a qualified and Rad-Hard tested mixed-signal IP library called HARD Lib (Hard Against Radiation Design) with multiple library elements usable for a wide range of applications. The IMST IP library is developed on XFABs XH018 technology and contains data converters, biasing cells, reconfigurable opamp, LVDS driver and receiver, SPI interface, OTP cells, clk PLL, oscillators and special I/O cells. The digital design flow supports a full custom design with standard cell libraries and a post-editing script for a triple mode redundancy implementation.

X-FAB serves as the semiconductor foundry in the supply chain and will support small to high volume wafer lots either on a single-mask set or for low quantities with a reduced price on a MLM-set. For the assembly two sizes of a lead frame CQFP package are supported with 256 pins and 132 pins, respectively. The capability approval includes the full screening of the devices as well as qualification and periodic testing according ESCC9000.

With the described capability domain a faster and more reliable ASIC development, with reduced development risk, can be offered compared to a single type ASIC design and qualification flow.

First publications of the ASIC supply chain have been given on the AMICSA 2014 and 2016 showing the design and results of the evaluation phase. In this publication the qualification phase will be presented together with an introduction of the capability domain.

The representative design for the qualification phase has been developed and will be presented. The wafers are fabricated and the assembly process has been started.