Speaker

Description

This paper presents the measurement circuits and simulation results of Single-Event Transients (SET) in a commercial 65nm CMOS technology. The measurements contain two parts: total SET ionized charge and SET pulse duration. Single transistors of different types and dimensions were implemented as victim devices. Additionally, SET variation due to different supply voltage was investigated. The test chip was tested under a heavy-ion beam with a LET (Linear Energy Transfer) from 1.3 to 62.5 MeV.cm2/mg and a 0-degree to 60-degree incidence angle.

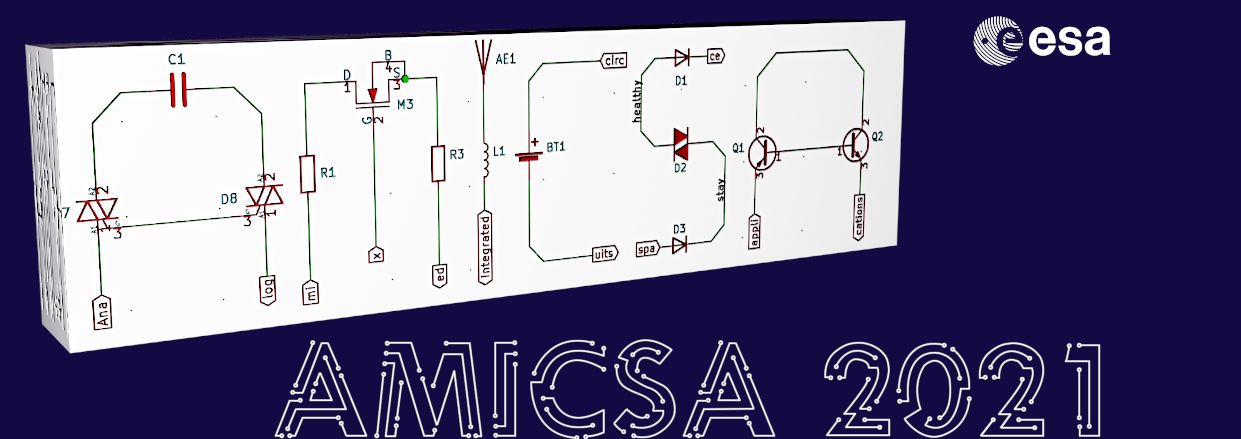

SET ionized charge measurement

The SET ionized charge measurement is based on an adjustable integrator and latch. When the SET ionized charge is generated at one of the victim devices, it will first be integrated by a charge integrator. The integrator feedback consists of 5 binary-weighted capacitors and series switches. By adjusting the feedback capacitor value, the feedback factor and the integrator output can be changed in 31 levels. When the output of the integrator is just enough to flip the latch, the feedback capacitor number is recorded. Then the SET ionized charge amount is converted to the threshold feedback capacitor number.

To calibrate the circuit, a known charge is generated and sent to the integrator. This known charge is injected by a known capacitor with a step signal. The ionized charge measurement circuit can achieve a range of up to 1.5pC with an accuracy of 47fC/step for thin oxide transistor measurement. The measurement range for the thick oxide victim device is up to 4.3pC with an accuracy of 140fC/step.

SET pulse duration measurement

The pulse duration measurement circuits consist of 3 parts: Victim devices, Combiner and Memory Delay Line (MDL). When the SET pulse is generated at one of the victim devices, it will be amplified and picked up by a combiner. Then, this pulse is measured by the MDL. The victim devices are biased by a pair of transistors, one of them is always activated and the other one can be turned on or off to investigate the RC influence on SET pulse duration. To minimize the non-linearity of the measurement, a balanced pulse combiner is built to have the same delay from all input to output. In MDL, the pulse is measured by normalizing it to the number of unit inverter delay T_inv. In this design, a 160-stage MDL is built, which can measure a duration of up to 160x T_inv. Two types of inverter (fast NMOS and fast PMOS) are implemented to minimize the T_inv and improve resolution.

The calibration circuit is implemented to measure the actual Tinv and the delay introduced by the combiner. This is realized by injecting a known pulse to the combiner and MDL. A configurable oscillator is designed to generate this known pulse. The MDL can measure the pulse duration up to 3ns with an accuracy of 18.2ps.